Контроллер передачи данных с псевдослучайной перестройкой рабочей частоты

Иллюстрации

Показать всеИзобретение относится к области радиотехники и может найти применение в адаптивных радиосредствах специальной радиосвязи для передачи данных по радиоканалу в условиях воздействия комплекса преднамеренных помех. Техническим результатом является повышение достоверности передачи информации за счет минимизации воздействия естественных и преднамеренных помех на аппаратуру. Устройство содержит пять регистров (1, 2, 3, 4, 5), (К+7) арифметико-логических устройств (91-9к, 6, 8, 10, 13, 15, 20, 22), два сумматора (7, 18), (К+3) компараторов (111-11K, 14, 34, 36), (К+4) регистров-защелок (121-12K, 16, 17, 19, 21), (M+1) вероятностных арифметико-логических устройств (231-23M+1); M кодовых арифметико-логических устройств (241-24M), M вероятностных компараторов (251-25м), М кодовых компараторов (261-26м), (M+1) кодовых регистров защелки (271-27M+1), (К+3) дешифраторов (291-29K, 28, 30, 31), M вероятностных дешифраторов (321-32м), M кодовых дешифраторов (331-33м), два демультиплексора (35, 37). 2 ил.

Реферат

Изобретение относится к области радиотехники и может найти применение в адаптивных радиосредствах специальной радиосвязи для передачи данных по радиоканалу в условиях воздействия комплекса преднамеренных помех.

Известен контроллер связи, описанный в [1], который включает в себя многорежимный контроллер, предсказатель повторного выбора сотовой ячейки, связанный с многорежимным контроллером, и контроллер эстафетной передачи обслуживания, связанный с многорежимным контроллером. Многорежимный контроллер предназначен для формирования управляющих сигналов для переключения между первым режимом работы, который не поддерживает соединение связи во время повторного выбора сотовой ячейки, и вторым режимом работы, который поддерживает соединение связи во время эстафетной передачи обслуживания, до момента времени, в который предсказана необходимость в повторном выборе сотовой ячейки.

Известен контроллер канала межблочного обмена, описанный в [2], в котором обмен информацией между ЭВМ и внешними устройствами осуществляется кадрами, состоящими из заголовка и данных. В заголовке передаются адрес внешнего устройства, число передаваемых слов и направление передачи.

Недостатком вышеупомянутых устройств является отсутствие адаптации синхросигнала к изменениям помеховой обстановки в случае воздействия преднамеренных помех.

Наиболее близким по технической сущности к заявляемому является программируемый контроллер, описанный в [3], принятый за прототип.

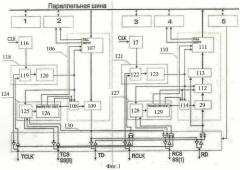

Функциональная схема устройства-прототипа приведена на фиг.1, где приняты следующие обозначения:

1 - первый регистр;

2 - второй регистр;

3 - третий регистр;

4 - четвертый регистр;

5 - пятый регистр;

29 - дешифратор;

106 - блок передатчика;

107 - буфер записи;

108 - счетчик бит передатчика;

109 - выходной мультиплексор;

110 - блок приемника;

111 - буфер чтения;

112 - шестой регистр;

113 - блок логики обмена;

114 - счетчик бит приемника;

116 - делитель частоты передатчика;

117 - делитель частоты приемника;

118 - блок генерации синхроимпульсов передатчика;

119 - мультиплексор тактового сигнала передатчика;

120 - преобразователь тактового сигнала передатчика;

121 - блок генерации синхроимпульсов приемника;

122 - мультиплексор тактового сигнала приемника;

123 - преобразователь тактового сигнала приемника;

124 - блок генерации управляющих сигналов передатчика;

125 - формирователь управляющего сигнала передатчика;

126 - преобразователь управляющего сигнала передатчика;

127 - блок генерации управляющих сигналов приемника;

128 - формирователь управляющего сигнала приемника;

129 - преобразователь управляющего сигнала приемника;

130 - блок управления выводами.

Устройство-прототип содержит регистры управления и состояния приемника и передатчика (первый регистр - регистр управления передатчиком, второй регистр - регистр состояния передатчика, третий регистр - регистр управления приемником, четвертый регистр - регистр состояния приемника), делители частоты приемника и передатчика, блоки генерации синхроимпульсов приемника и передатчика, каждый из которых состоит из мультиплексора тактового сигнала и преобразователя тактового сигнала, блоки генерации управляющих сигналов приемника и передатчика, каждый из которых состоит из формирователя управляющих сигналов и преобразователя управляющих сигналов, блок передатчика, состоящий из буфера записи, счетчика и мультиплексора, блок приемника, состоящий из буфера чтения, блока логики обмена, шестого регистра - приемного регистра, счетчика и дешифратора, блок управления выводами, пятый регистр - регистр управления выводами.

Устройство-прототип работает следующим образом.

Схема контроллера функционально разделена на две части - приемник и передатчик. При этом приемник и передатчик могут работать как независимо (работая по разным интерфейсам и на разных частотах), так и в зависимом состоянии (при этом управляющие и тактовые сигналы передатчика дублируются для приемника), что позволяет приемнику и передатчику использовать один управляющий и один тактовый сигнал при работе порта по одному интерфейсу.

Логика обмена 113 выполняет обнуление или дополнение значением старшего разряда избыточных бит. Это позволяет избежать дополнительной программной обработки и возможных ошибок при приеме слов длиной меньше, чем разрядность регистра приема. Выборка данных через мультиплексор и запись с использованием дешифратора позволяют с минимальными аппаратными затратами реализовать передачу слов произвольной длины как старшим, так и младшим битом вперед.

Контрольные регистры 1, 3 позволяют производить независимую программную настройку передатчика и приемника. Регистры состояния передатчика и приемника 2, 4 содержат информацию о состоянии буфера чтения и буфера записи, а также флаги прерывания.

Регистр управления выводами 5 содержит биты, позволяющие задавать направление каждого вывода. Делители частоты 116, 117 позволяют формировать тактовые сигналы для приемника и передатчика путем деления частоты системного тактового сигнала.

Блок генерации синхроимпульсов передатчика 118 состоит из мультиплексора тактового сигнала передатчика 119 и преобразователя тактового сигнала передатчика 120. Мультиплексор тактового сигнала передатчика позволяет использовать для управления блоком передатчика как внешний тактовый сигнал, так и тактовый сигнал, принимаемый от делителя частоты передатчика. Преобразователь тактового сигнала передатчика инвертирует тактовый сигнал при необходимости работы передатчика по отрицательному фронту. Блок генерации синхроимпульсов приемника 121 состоит из мультиплексора тактового сигнала приемника 122 и преобразователя тактового сигнала приемника 123.

Мультиплексор тактового сигнала приемника позволяет использовать для управления блоком приемника как тактовый сигнал, принимаемый от блока управления выводами (который в свою очередь может либо приниматься с внешнего вывода либо дублировать тактовый сигнал передатчика), так и тактовый сигнал, принимаемый от делителя частоты приемника. Преобразователь тактового сигнала приемника инвертирует тактовый сигнал при необходимости работы приемника по отрицательному фронту. Использование преобразователей тактового сигнала позволяет использовать в схеме блоки приемника и передатчика, срабатывающие по фиксированному фронту тактового сигнала.

Блок генерации управляющих сигналов передатчика 124 состоит из блоков формирователя управляющего сигнала передатчика 125 и преобразователя управляющего сигнала передатчика 126. Формирователь управляющего сигнала передатчика в соответствии с настройками выводов выполняет либо формирование управляющего сигнала для выбранного интерфейса (при этом используется тактовый сигнал, принимаемый от логики генерации синхроимпульсов), либо его прием с внешних выводов схемы.

Преобразователь управляющего сигнала передатчика выполняет преобразование интерфейсного управляющего сигнала, принимаемого от формирователя управляющего сигнала передатчика к трем универсальным контрольным сигналам: TEN (разрешение передачи), ReadWB (разрешение чтения из буфера записи) и trst (сброс счетчика передатчика).

Блок генерации управляющих сигналов передатчика содержит логику формирования двухразрядной шины выбора ведомого устройства. При этом младший разряд шины направляется на вывод контрольного сигнала передатчика, а старший разряд на вывод контрольного сигнала приемника, позволяя таким образом в режиме полнодуплексного SPI работать с двумя параллельно подключенными ведомыми устройствами.

Блок генерации управляющих сигналов приемника 127 состоит из блоков формирователя управляющего сигнала приемника 128 и преобразователя управляющего сигнала приемника 129. Формирователь управляющего сигнала приемника в соответствии с настройками выводов выполняет либо формирование управляющего сигнала для выбранного интерфейса (при этом используется тактовый сигнал, принимаемый от логики генерации синхроимпульсов), либо его прием с внешних выводов схемы. Преобразователь управляющего сигнала приемника выполняет преобразование интерфейсного управляющего сигнала, принимаемого от формирователя управляющего сигнала приемника к трем универсальным контрольным сигналам: REN (разрешение приема), WriteRB (разрешение записи в буфер чтения) и rrst (сброс счетчика приемника).

Контрольные сигналы, формируемые блоками генерации управляющих сигналов для приемника и передатчика, универсальны и не зависят от выбранного протокола передачи. Это позволяет использовать в схеме универсальные блоки приемника и передатчика, что заметно упрощает логику схемы. Кроме того, управляющие сигналы формируются в автоматическом режиме, что дает возможность контроллеру вести передачу данных без участия процессора. Блоки генерации управляющих сигналов приемника и передатчика также содержат логику автоматического определения канала для работы в режиме I2S, а блок генерации управляющих сигналов передатчика - логику формирования двухразрядного сигнала выбора ведомого для полнодуплексного режима SPI.

В общем случае приемник и передатчик могут работать независимо. Однако возможна работа приемника в зависимом от передатчика режиме.

В устройстве-прототипе правильное декодирование информации является эффективным только в условиях воздействия непреднамеренных помех. В средствах специальной радиосвязи центральным направлением является повышение помехозащищенности в условиях непрерывного совершенствования средств радиопротиводействия (СРП), в частности, при воздействии на радиолинию с ППРЧ с целью подавления одной из эффективных с точки зрения энергетических возможностей запаздывающих помех в комплексе с заградительной помехой в части полосы (ЗПП).

Последнее условие свидетельствует о том, что неизменяемая радиолиния, образуемая работой устройства-прототипа, не в состоянии обеспечить заданное качество связи на протяжении всего сеанса связи, поскольку входные условия могут время от времени изменяться. Таким образом, недостатком устройства-прототипа является низкое качество передачи информации в условиях преднамеренных помех. В этом случае возникает необходимость использования адаптивного устройства управления, которое, используя регулярный процесс поиска, постоянно ищет оптимум в пределах допустимого класса возможностей.

Задачей заявляемого изобретения является введение адаптации устройства управления передачей данных с ППРЧ к изменениям помеховой обстановки и уменьшение потерь информации.

Достигаемый при этом технический результат - минимизация воздействия естественных и преднамеренных помех на аппаратуру связи, составной частью которой является данный контроллер, и повышение достоверности передачи информации.

Для реализации указанной задачи в микроконтроллер, содержащий пять регистров и дешифратор, согласно изобретению введены два сумматора, два демультиплексора, (К+3) компараторов, М кодовых компараторов, М вероятностных компараторов, (К+4) регистров-защелок, (М+1) кодовых регистров-защелок, (К+2) дешифраторов, М кодовых дешифраторов, М вероятностных дешифраторов, (К+7) арифметико-логических устройств (АЛУ), М кодовых АЛУ и (М+1) вероятностных АЛУ, при этом выход первого регистра через последовательно соединенные (К+1)-е АЛУ, (К+5)-е АЛУ, (К+1)-й компаратор, (Д+2)-й дешифратор, (К+1)-й регистр-защелку, второй сумматор, (К+6)-е АЛУ, (К+3)-й компаратор и (К+3)-й дешифратор соединен со вторым входом второго сумматора; выход второго регистра через последовательно соединенные (К+3)-е АЛУ, (К+2)-й компаратор, (К+1)-й дешифратор, первый сумматор и первый демультиплексор соединен со вторыми входами (К+5)-го АЛУ, (К+6)-го АЛУ, (К+7)-го АЛУ и 1-го-М-го кодовых АЛУ; выход первого сумматора соединен, кроме того, со вторым входом (К+3)-го АЛУ, а второй выход (К+1)-го АЛУ - с третьим входом (К+3)-го АЛУ, четвертый вход которого, объединенный со вторым входом (К+3)-го регистра-защелки, является третьим входом устройства; выход (К+3)-го регистра-защелки соединен с третьим входом второго сумматора, выход которого соединен, кроме того, через второй демультиплексор с первым входом (К+4)-го регистра-защелки, выход которого, соединенный шиной с пятым входом (К+7)-го АЛУ и с выходом (К+2)-го регистра-защелки, является вторым выходом устройства; второй выход (К+3)-го дешифратора соединен со вторым входом (К+4)-го регистра-защелки; выход (К+3)-го компаратора соединен, кроме того, со вторым входом второго демультиплексора, а второй выход (К+5)-го АЛУ соединен шиной с (К+2)-м регистром-защелкой; четвертый вход (К+6)-го АЛУ, соединенный с четвертым входом (К+7)-го АЛУ, является четвертым входом устройства; выход (К+2)-го компаратора соединен, кроме того, со вторым входом 1-го демультиплексора; выход четвертого регистра соединен с четвертым входом (К+5)-го АЛУ и первым входом (К+7)-го АЛУ, выход которого является третьим выходом устройства; выход третьего регистра соединен со вторым входом первого сумматора; второй выход (К+1)-го дешифратора соединен с третьими входами (К+5)-го, (К+6)-го и (К+7)-го АЛУ, а также с первыми входами 1-го-М-го кодовых АЛУ, причем выход каждого i-го кодового АЛУ (где i∈[1,…,М]) соединен с первым входом соответствующего i-го кодового компаратора, выход которого соединен с входом соответствующего i-го кодового дешифратора; соединенные шиной входы 1-го-(М+1)-го вероятностных АЛУ являются вторым входом устройства, причем выход каждого i-го вероятностного АЛУ соединен с первым входом соответствующего i-го вероятностного компаратора, выход которого соединен с входом соответствующего i-го вероятностного дешифратора; выход (М+1)-го вероятностного АЛУ соединен со вторыми входами 1-го-М-го вероятностных компараторов; второй выход каждого i-го кодового дешифратора соединен с входом соответствующего i-го кодового регистра-защелки; выход (М+1)-го кодового регистра-защелки, соединенный с выходами 1-го-М-го кодовых регистров-защелок, является четвертым выходом устройства; выход пятого регистра соединен со вторым входом (К+1)-го компаратора; объединенные входы 1-го - К-го АЛУ соединены шиной с первым входом устройства, а выход каждого j-го АЛУ (где j∈[1,…,K]) соединен с соответствующим j-м входом (К+2)-го АЛУ, выход которого соединен с входами 1-го - К-го компараторов, причем выход каждого j-го компаратора соединен с входом соответствующего j-го дешифратора, выход которого соединен с входом соответствующего j-го регистра-защелки, выход которого соединен с соответствующим j-м входом (К+4)-го АЛУ, выход которого соединен с пятым входом (К+5)-го АЛУ; кроме того, выходы 1-го - К-го регистров-защелок объединены в первый выход устройства; второй выход каждого ℓ-го дешифратора (где ℓ∈[1,…,K-1]) соединен со вторым входом соответствующего (ℓ+1)-го компаратора, а выход каждого β-го вероятностного дешифратора, где β∈[1,…,M-1], объединенный с выходом соответствующего β-го кодового дешифратора, соединен с входом соответствующего (β+1)-го вероятностного компаратора; второй выход каждого вероятностного дешифратора соединен с входом соответствующего кодового компаратора; выход М-ого вероятностного дешифратора соединен с входом (М+1)-го кодового регистра-защелки, а выход М-го кодового дешифратора соединен с третьим входом первого сумматора; синхровходы каждого из вышеупомянутых блоков соединены с пятым, синхронизирующим входом устройства.

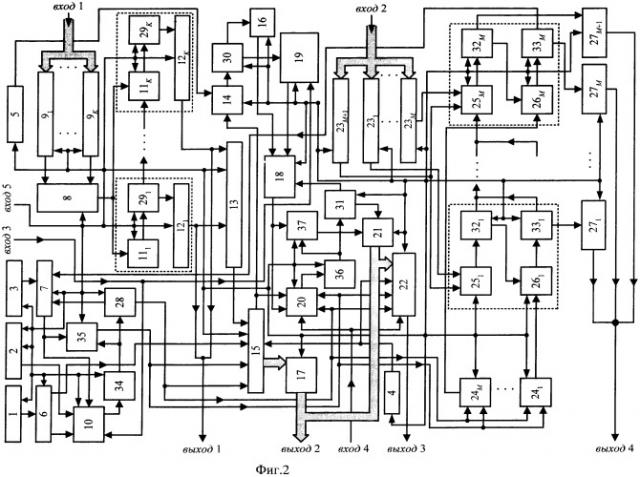

Функциональная схема заявляемого устройства приведена на фиг.2, где приняты следующие обозначения:

1 - первый регистр;

2 - второй регистр;

3 - третий регистр;

4 - четвертый регистр;

5 - пятый регистр;

6 - (K+1)-е арифметико-логическое устройство (АЛУ);

7 - первый сумматор;

8 - (К+2)-е АЛУ;

91-9K - 1-е-K-е АЛУ;

10 - (К+3)-е АЛУ;

111-11K - с 1-го по K-й компараторы;

121-12K - с 1-го по К-й регистры-защелки (РЗ);

13 - (К+4)-е АЛУ;

14 - (К+1)-й компаратор;

15 - (К+5)-е АЛУ;

16 - (К+1)-й РЗ;

17 - (К+2)-й РЗ;

18 - второй сумматор;

19 - (К+3)-й РЗ;

20 - (К+6)-е АЛУ;

21 - (К+4)-й РЗ;

22 - (К+7)-е АЛУ;

231-23М+1 - с 1-го по (М+1)-е вероятностные АЛУ;

241-24М - с 1-го по М-е кодовые АЛУ;

251-25М - с 1-го по М-й вероятностные компараторы;

261-26М - с 1-го по М-й кодовые компараторы;

271-27M+1 - с 1-го по (М+1)-й кодовые РЗ;

28 - (К+1)-й дешифратор;

291-29К - с 1-го по K-й дешифраторы;

30 - (К+2)-й дешифратор;

31 - (К+3)-й дешифратор;

321-32М - с 1-го по М-й вероятностные дешифраторы;

331-33М - с 1-го по М-й кодовые дешифраторы;

34 - (К+2)-й компаратор;

35 - первый демультиплексор;

36 - (К+3)-й компаратор;

37 - второй демультиплексор.

Заявляемое устройство содержит последовательно соединенные первый регистр 1, (К+1)-е АЛУ 6, (К+5)-е АЛУ 15, (К+1)-й компаратор 14, (К+2)-й дешифратор 30, (К+1)-й регистр-защелку (РЗ) 16, второй сумматор 18, (К+6)-е АЛУ 20, (К+3)-й компаратор 36 и (К+3)-й дешифратор 31, выход которого соединен со вторым входом второго сумматора 18; последовательно соединенные второй регистр 2, (К+3)-е АЛУ 10, (К+2)-й компаратор 34, (К+1)-й дешифратор 28, первый сумматор 7 и первый демультиплексор 35, выход которого соединен со вторыми входами (К+5)-го АЛУ 15, (К+6)-го АЛУ 20, (К+7)-го АЛУ 22, а также со вторыми входами М кодовых АЛУ 241-24М. Выход первого сумматора 7 соединен, кроме того, со вторым входом (К+3)-го АЛУ 10, а второй выход (К+1)-го АЛУ 6 - с третьим входом (К+3)-го АЛУ 10, четвертый вход которого является третьим входом устройства, соединенным со вторым входом (К+3)-го РЗ 19, выход которого соединен с третьим входом второго сумматора 18, выход которого соединен также с первым входом второго демультиплексора 37, выход которого соединен с первым входом (К+4)-го РЗ 21, выход которого, соединенный шиной с пятым входом (К+7)-го АЛУ 22 и с выходом (К+2)-го РЗ 17, является вторым выходом устройства. Выход (К+3)-го дешифратора 31 соединен со вторым входом (К+4)-го РЗ 21. Выход (К+3)-го компаратора 36 соединен, кроме того, со вторым входом второго демультиплексора 37. Второй выход (К+5)-го АЛУ 15 соединен шиной с входом (К+2)-го РЗ 17. Четвертый вход (К+6)-го АЛУ 20, соединенный с четвертым входом (К+7)-го АЛУ 22, является четвертым входом устройства. Выход (К+2)-го компаратора 34 соединен также со вторым входом первого демультиплексора 35. Выход четвертого регистра 4 соединен с четвертым входом (К+5)-го АЛУ 15 и первым входом (К+7)-го АЛУ 22, выход которого является третьим выходом устройства. Выход третьего регистра 3 соединен со вторым входом первого сумматора 7.

Второй выход (К+1)-го дешифратора 28 соединен с третьими входами (К+5)-го АЛУ 15, (К+6)-го АЛУ 20 и (К+7)-го АЛУ 22, а также с первыми входами 1-го, …, М-го кодового АЛУ 241-24М, причем выход i-го кодового АЛУ 24i (где i∈[1,…,М]) соединен с входом i-го кодового компаратора 26i, выход которого соединен с входом i-го кодового дешифратора 33i.

Соединенные шиной входы 1-го-(М+1)-го вероятностных АЛУ 231-23М+1 являются вторым входом устройства, причем выход i-го вероятностного АЛУ 23i соединен с входом i-го вероятностного компаратора 25i, выход которого соединен с входом i-го вероятностного дешифратора 32i.

Выход (М+1)-го вероятностного АЛУ 23M+1 соединен со вторыми входами 1-го-М-го вероятностных компараторов 251-25M. Выход i-го кодового дешифратора 33i соединен с входом i-го кодового РЗ 27i. Объединенные выходы 1-го-М-го кодовых РЗ 271-27М объединены с выходом (М+1)-го кодового РЗ 27М+1 в четвертый выход устройства.

Выход пятого регистра 5 соединен со вторым входом (К+1)-го компаратора 14. Объединенные входы 1-го - К-го АЛУ 91-9К соединены шиной с первым входом устройства, а выход j-го (где j∈[1,…,K]) АЛУ 91-9К соединен с соответствующим j-м входом (К+2)-го АЛУ 8, выход которого соединен со входами 1-го - К-го компараторов 111-11K, причем выход j-го компаратора 11j соединен с входом j-го дешифратора 29j.

Выход j-го дешифратора 29j соединен с входом j-го РЗ 12j, выход которого соединен с j-м входом (K+4)-го АЛУ 13, выход которого соединен с пятым входом (К+5)-го АЛУ 15. Также, выходы 1-го - К-го РЗ 121-12K объединяются в первый выход устройства.

Второй выход ℓ-го дешифратора 29ℓ, где ℓ∈[1,…, K-1], соединен со вторым входом (ℓ+1)-го компаратора 11ℓ+1. Выход β-го вероятностного дешифратора 32β, где β∈[1,…, M-1], объединен с выходом соответствующего β-го кодового дешифратора 33β и соединен с входом (β+1)-го вероятностного компаратора 25β+1. Второй выход каждого вероятностного дешифратора 32i соединен с соответствующим входом кодового компаратора 26i. Выход М-ого вероятностного дешифратора 32М соединен с входом (М+1)-го кодового РЗ 27М+1. Выход М-ого кодового дешифратора 33М соединен с третьим входом первого сумматора 7.

Синхровходы каждого из пяти регистров 1, 2, 3, 4 и 5, первого 7 и второго 18 сумматоров, первого 35 и второго 37 демультиплексоров, (К+1) компараторов 111-11K и 14, М кодовых компараторов 261-26M, М вероятностных компараторов 251-25M, (К+4) регистров-защелок 121-12K, 16, 17, 19 и 21, (М+1) кодовых регистров-защелок 271-27М+1 (K+3) дешифраторов 291-29К, 28, 30, 31, М кодовых дешифраторов 331-33M, М вероятностных дешифраторов 321-32M, (К+7) АЛУ 91-9K, 6, 8, 10, 13, 15, 20, 22, М кодовых АЛУ 241-24M, (М+1) вероятностных АЛУ 231-23M+1 соединены с пятым, синхронизирующим входом устройства.

Заявляемое устройство работает следующим образом.

Работа начинается с нулевого состояния блока 3, где происходит обнуление количества информационных слотов (δ=0), а также с присвоения в блоке 1 значения времени перестройки частоты Tn=const 1, в блоке 2 - значения времени рассинхронизации синтезаторов частот Тр=const 2, в блоке 4 - значения числа повторов слотов синхронизации d=const 3 и в блоке 5 - значения минимально необходимого числа бит в служебных фреймах е=const 4.

На основании значения блока 1, в блоке 6 происходит расчет необходимого количества битов перестройки частоты:

,

где V - скорость передачи в радиосредстве;

[] - целая часть.

В блоке 7 первоначально происходит увеличение значения блока 3 на единицу, и это значение загружается в блок 35.

На основании значения блоков 6, 2, 7 и значения технической скорости передачи информации V с 3-го входа устройства, в блоке 10 происходит вычисление значения количества информационных битов слота:

,

где q=[x·λ] - количества защитных бит информационного слота;

λ2 - коэффициент, зависящий от количества частоты ППРЧ и априорно известных условий распространения сигнала (например, для фиксированной частоты можно принять λ2≈3%; для ППРЧ из двух частот - λ2≈6% и т.д.).

Полученное значение x поступает в блок 34, где происходит проверка условия x - целое.

Из блока 34 в блоки 35 и 28 поступает сигнал, который является для данных блоков сигналом управления:

- если условие x - целое не будет выполнено, то данный сигнал представляет собой логический "0", который в блоке 35 запрещает выходной сигнал, а в блоке 28 направляет сигнал в блок 7, где происходит увеличение значения этого блока на единицу и это значение загружается в блоки 35 и 10;

- если условие x - целое выполнено, то данный сигнал представляет собой значение x, которое через блок 28 загружается в блоки 15, 20, 22, 241-24M, а в блоке 35 разрешает выходной сигнал, и из этого блока значение δ поступает в блоки 15, 20, 22, 241-24M.

В блоках 241-24M рассчитывается число кодовых слов в информационном фрейме , , …, , соответственно (n1, n2,…, nM - длины тех М помехоустойчивых кодов, которые используются в данном радиосредстве).

С первого входа в блоки 91-9К по шине данных поступают характеристики качества канала синхронизации для определения вероятностей правильного приема Рпр и ложной тревоги Рлт [4]. В этих блоках производится расчет средних рисков Rj (j=1…К) по формуле:

R=a·Pнал.сигн·(1-Pпр)+b·Pотс.сигн·(1-Pлт),

где Ротс.сигн - априорная вероятность отсутствия сигнала;

Рнал.сигн - априорная вероятность наличия сигнала;

а и b - весовые коэффициенты, зависящие от того, насколько опасна Рлт по сравнению с 1-Рпр.

Полученные в блоках 91-9К значения средних рисков R1-RK поступают в блок 8, где определяется минимальное из них значение - min, которое поступает в блоки 111-11K, каждый из которых формирует сигналы управления для блоков 291-29K, соответственно.

В блоках 11ℓ, где ℓ∈[1,…,K-1], последовательно, начиная с блока 111, производится проверка условий:

- если условие min=Rℓ выполняется, то сигнал управления представляет собой логическую "1", которая направляет сигнал из блока 29ℓ в блок 12ℓ, где присваивается значение длины синхропоследовательности L=Lℓ; если условие min=Rℓ не выполняется, то сигнал управления представляет собой логический "0", который направляет сигнал из блока 29ℓ в блок 11ℓ+1, где происходит проверка условия min=Rℓ+1.

Затем в блоке 11K производится проверка условий:

- если условие min=RK выполняется, то сигнал управления представляет собой логическую "1", которая направляет сигнал из блока 29К в блок 12K, где присваивается значение длины синхропоследовательности L=LК; если условие min=RK не выполняется, то сигнал управления представляет собой логический "0", который не позволяет передать сигнал из блока 29К.

Значение того из блоков 121-12К, где произошло присвоение, поступает на первый выход контроллера для регулирования вида синхропоследовательности на передающей и приемной частях радиосредства, в которое входит данный контроллер, и в блок 13, где происходит вычисление количества защитных бит служебного слота:

z=[L·λ1],

где [] - целая часть, а λ1 - коэффициент, зависящий от количества частот ППРЧ и априорно известных условий распространения сигнала, аналогичный описанному выше.

Значения блоков 4, 6 и 13 вводятся в блок 15, где производится расчет количества бит во фрейме Ψ=(y+L+z)·d+(y+x+q)·δ. Значения y, L, x, z, d, Ψ и δ по шине данных записываются в блок 17 и по шине данных поступают на второй выход контроллера для регулировки вида пакета на передающей и приемной частях радиосредства, в которое входит данный контроллер.

Значение необходимой скорости передачи информации С, подаваемое с четвертого входа устройства, а также значение Ψ, полученное в блоке 15 и значение блока 18, загружаются в блок 20, где происходит вычисление значения времени передачи пакета:

.

Полученное значение Т поступает в блок 36, где происходит проверка условия Т - конечная десятичная дробь. Из блока 36 в блоки 31 и 37 поступает сигнал, который является для данных блоков сигналом управления:

- если условие Т - конечная десятичная дробь не будет выполнено, то данный сигнал представляет собой логический "0", который в блоке 37 запрещает выходной сигнал, а в блоке 31 направляет сигнал в блок 18, где происходит увеличение значения этого блока на единицу и это значение загружается в блоки 37 и 20;

- если условие Т - конечная десятичная дробь выполнено, то данный сигнал представляет собой значение Т, которое через блок 31 загружается в блоки 21, а в блоке 37 разрешает выходной сигнал, и из этого блока значение δ поступает в блок 21.

Из блока 21 величины Т и g по шине данных поступают на второй выход контроллера для регулировки вида пакета на передающей и приемной частях радиосредства, в которое входит данный контроллер. Кроме того, значения Т и g из блока 21 по шине данных загружаются в блок 22. Сюда же загружается значение блока 4 и значение необходимой скорости передачи информации С с четвертого входа устройства, и рассчитывается скорость ППРЧ:

Из блока 22 значение γ поступает на третий выход контроллера для регулировки процессами модуляции и демодуляции на передающей и приемной, соответственно, частях радиосредства, в которое входит данный контроллер.

Из блока 15 значение Ψ, кроме того, загружается в блок 14, где происходит проверка условия е≤Ψ. Из блока 14 в блок 30 поступает сигнал, который является для данного блока сигналом управления:

- если условие е≤Ψ не будет выполнено, то данный сигнал представляет собой логический "0", который направляет сигнал в блок 19, где происходит присвоение , где [] - целая часть на основании поступающего значения технической скорости передачи информации V с 3-го входа устройства;

- если условие Т - конечная десятичная дробь выполнено, то данный сигнал представляет собой логическую "1", которая направляет сигнал в блок 16, где происходит присвоение g=0.

Значение того из блоков 16 или 19, где произошло присвоение, загружается в блок 18, где увеличивается на единицу.

Со второго входа в блоки 231-23M+1 по шине данных поступают характеристики информационного канала для определения вероятностей правильного приема W, W1-WM кодовых слов тех М помехоустойчивых кодов, которые используются в данном радиосредстве (W рассчитывается для случая, когда помехоустойчивый код не используется) [5]. Полученные в блоках 231-23М значения W1-WM поступают, соответственно, в блоки 251-25M.

Значение блока 23М+1 также поступает в каждый из блоков 251-25М, каждый из которых формирует сигналы управления для блоков 321-32К, соответственно. В блоках 25β, где β∈[1,…,M-1] последовательно, начиная с блока 251, производится проверка условий:

- если условие Wβ>W выполняется, то сигнал управления представляет собой логическую "1", которая направляет сигнал из блока 32β в блок 26β, где происходит сравнение Ωβ с целым числом; если условие Wβ>W не выполняется, то сигнал управления представляет собой логический "0", который направляет сигнал из блока 32β в блок 25β+1, где происходит проверка условия Wβ+1>W.

Затем в блоке 25М производится проверка условий:

- если условие WM>W выполняется, то сигнал управления представляет собой логическую "1", которая направляет сигнал из блока 32М в блок 26М, где происходит сравнение ΩM с целым числом; если условие WM>W не выполняется, то сигнал управления представляет собой логический "0", который направляет сигнал из блока 32М в блок 27М+1, где происходит присвоение i=0.

Рассчитанные в блоках 241-24M значения Ω1, Ω2, …, ΩM поступают, соответственно, в блоки 261-26М, каждый из которых формирует сигналы управления для блоков 331-33М, соответственно. В блоках 26β, где β∈[1,…,M-1], последовательно, начиная с блока 261, производится проверка условий:

- если выполняется условие, что Ωβ - целое число, то сигнал управления представляет собой логическую "1", которая направляет сигнал из блока 33β в блок 27β, где происходит присвоение i=β; если условие, что Ωβ целое число не выполняется, то сигнал управления представляет собой логический "0", который направляет сигнал из блока 33β в блок 25β+1, где происходит проверка условия Wβ+1>W.

Затем в блоке 26М производится проверка условий:

- если выполняется условие, что ΩM - целое число, то сигнал управления представляет собой логическую "1", которая направляет сигнал из блока 33М в блок 27М, где происходит присвоение i=М; если условие, что ΩM - целое число не выполняется, то сигнал управления представляет собой логический "0", который направляет сигнал из блока 33M в блок 7, где происходит увеличение значения блока 7 на единицу.

Значение того из блоков 271-27M+1, где произошло присвоение, поступает на четвертый выход контроллера для регулировки вида помехоустойчивого кода на передающей и приемной частях радиосредства, в которое входит данный контроллер.

С 5-го входа контроллера на блоки 1-37 по шине данных подаются тактовые импульсы, определяющие начало каждой микрооперации, в результате чего обеспечивается синхронизация работы устройства в целом.

Регистры, АЛУ, сумматоры, компараторы, дешифраторы и демультиплексоры могут быть реализованы физически на базе элементов, описанных в [8]. Регистры-защелки могут быть реализованы физически на базе элементов, описанных в [7].

Контроллер в целом может быть реализован в виде перепрограммируемого цифрового устройства [6].

Таким образом, введение в заявляемом устройстве новых блоков и связей позволяет увеличить достоверность приема информации за счет адаптации к изменению помеховой обстановки, что позволяет применять его в спецсвязи в условиях воздействия преднамеренных помех.

Источники информации

1. Патент РФ на изобретение №2366107 "Контроллер связи и способ для поддержания соединения связи во время повторного выбора сотовой ячейки. Шейман А., Блэк Г., Песен М., 2007 год.

2. Патент РФ на изобретение №2345407 "Контроллер канала межблочного обмена", Горшков С.Н., 2007 год.

3. Патент РФ на изобретение №2360282 "Программируемый контроллер последовательных шин". Путря Ф.М., 2007 год.

4. Шумоподобные сигналы в системах передачи информации./ Под ред. проф. В.Б.Пестрякова. М., "Сов. радио", 1973.

5. Феер. К. Беспроводная цифровая связь. Методы модуляции и расширения спектра: Пер. с англ. / Под ред. В.И.Журавлева. - М., Радио и связь, 2000.

6. Техническое обеспечение цифровой обработки сигналов. Справочник. Куприянов М.С., Матюшкин Б.Д., Иванова В.Е., Матвиенко Н.И., Усов Д.Ю. - СПб. "Форт", 2000.

7. Искуство схемотехники. П.Хоровиц, У.Хилл - Москва. "Мир", 1998, п.8.24.

8. Алексеенко А.Г., Шакулин И.И. "Микросхемотехника". Учебное пособие для вузов. - 2-е изд., перераб. и доп. - Москва, "Радио и связь", 1990.

Контроллер передачи данных с псевдослучайной перестройкой рабочей частоты, содержащий пять регистров и дешифратор, отличающийся тем, что в него введены два сумматора, два демультиплексора, (К+3) компараторов, М кодовых компараторов, М вероятностных компараторов, (К+4) регистров-защелок, (M+1) кодовых регистров-защелок, (К+2) дешифраторов, М кодовых дешифраторов, М вероятностных дешифраторов, (К+7) арифметико-логических устройств (АЛУ), М кодовых АЛУ и (M+1) вероятностных АЛУ, при этом выход первого регистра через последовательно соединенные (К+1)-е АЛУ, (К+5)-е АЛУ, (К+1)-й компаратор, (К+2)-й дешифратор, (К+1)-й регистр-защелку, второй сумматор, (К+6)-е АЛУ, (К+3)-й компаратор и (К+3)-й дешифратор соединен со вторым входом второго сумматора; выход второго регистра через последовательно соединенные (К+3)-е АЛУ, (К+2)-й компаратор, (К+1)-й дешифратор, первый сумматор и первый демультиплексор соединен со вторыми входами (К+5)-го АЛУ, (К+6)-го АЛУ, (К+7)-го АЛУ и 1-го - М-го кодовых АЛУ; выход первого сумматора соединен, кроме того, со вторым входом (К+3)-го АЛУ, а второй выход (К+1)-го АЛУ - с третьим входом (К+3)-го АЛУ, четвертый вход которого, объединенный со вторым входом (К+3)-го регистра-защелки, является третьим входом устройства; выход (К+3)-го регистра-защелки соединен с третьим входом второго сумматора, выход которого соединен, кроме того, через второй демультиплексор с первым входом (К+4)-го регистра-защелки, выход которого, соединенный шиной с пятым входом (К+7)-го АЛУ и с выходом (К+2)-го регистра-защелки, является вторым выходом устройства; второй выход (К+3)-го дешифратора соединен со вторым входом (К+4)-го регистра-защелки; выход (К+3)-го компаратора соединен, кроме того, со вторым входом второго демультиплексора, а второй выход (К+5)-го АЛУ соединен шиной с (К+2)-м регистром-защелкой; четвертый вход (К+6)-го АЛУ, соединенный с четвертым входом (К+7)-го АЛУ, является четвертым входом устройства; выход (К+2)-го компаратора соединен, кроме того, со вторым входом 1-го демультиплексора; выход четвертого регистра соединен с четвертым входом (К+5)-го АЛУ и первым входом (К+7)-го АЛУ, выход которого является третьим выходом устройст