Экстраполятор приращений для цифровой интегрирующей л\ашиньг

Иллюстрации

Показать всеРеферат

244735

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 05.Ill.1968 (№ 1223378/18-24) с присоединением заявки №

Приоритет

Опубликовано 28Х.1969. Бюллетень № 18

Дата опубликования описания 20.Х,1969

Кл. 42птз, 1/02

МПК G 06т

УДК 681.332.64(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Авторы изобретения

А. В. Каляев и П. П. Кравченко

Таганрогский радиотехнический институт

Заявитель

ЭКСТРАПОЛЯТОР ПРИРАЩЕНИЙ ДЛЯ ЦИФРОВОЙ

ИНТЕГРИРУЮЩЕЙ МАШИНЫ

Изобретение относится к области цифровых дифференциальных анализаторов.

Известны экстраполяторы приращений для цифровой интегрирующей машины с полноразрядными приращениями, работающие по формуле экстраполяции и-го порядка и с числами, запятая которых фиксирована, содержащие регистры, сумматоры, преобразователи кода и блоки выделения значащей части числа.

Предлагаемый экстраполятор отличается от известных тем, что вход интегратора и сумматора приращений соединен со входами первого и второго сумматоров и со входом первого регистра, выход которого связан со входом первого преобразователя кода. Выход первого преобразователя соединен со входом первого сумматора, выход которого соединен со входом второго сумматора. Выход второго сумматора связан со входом третьего сумматора, выход первого сумматора подключен ко входу четвертого сумматора и к блоку выделения значащей части числа, выход которого соединен со входом второго регистра. Выход последнего соединен со входом преобразователя кода, выход которого соединен со входом третьего сумматора.

Это позволяет уменьшить объем требуемого оборудования.

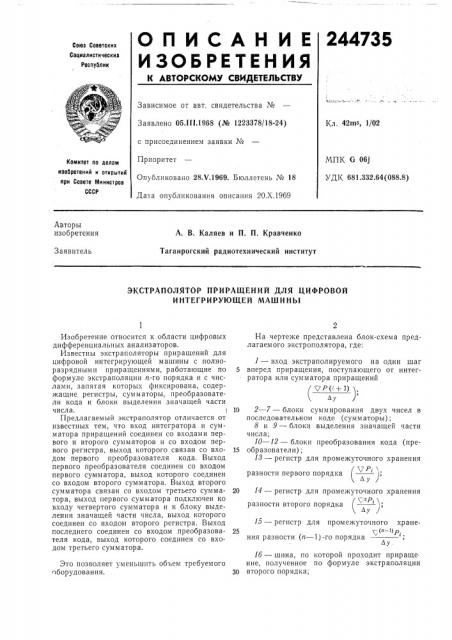

На чертеже представлена блок-схема предлагаемого экстрополятора, где:

1 — вход экстраполируемого на один шаг

5 вперед приращения, поступающего от интегратора или сумматора приращений

VP(! + 1)

10 2 — 7 — блоки суммирования двух чисел в последовательном коде (сумматоры);

8 и 9 — блоки выделения значащей части числа;

10 — 12 — блоки преобразования кода (пре15 образователи);

18 — регистр для промежуточного хранения б 7Р разности первого порядка ); у )

20 14 — регистр для промежуточного хранения с,зр, разности второго порядка ); 1 к

15 — регистр для промежуточного хране25 — (и — 1) р ния разности (n — 1) -го порядка

Ау.

1б — шина, по которой проходит прираще ние, полученное по формуле экстраполяции

30 второго порядка;

317 — шина, по которой проходит приращение, полученное по формуле экстраполяции третьего порядка;

l8 — выход экстраполятора, работающего по формуле экстраполяции и-го порядка;

19 — каналы, по которым в экстраполятор поступают управляющие сигналы из устройства управления цифровой интегрирующей машины (ЦИМ).

Блоки выделения значащей части числа предназначены для выделения в числе количества разрядов, установленного при проектировании ЦИМ.

Блоки преобразования кода предназначены для инверсии кода и размножения знака числа. Размножение знака числа соответствует выравниванию весов разрядов чисел при сложении в дополнительном коде.

Регистры для промежуточног 7Р 72 Р разностей

Ду Ду о хранения (n — 1) р

Ду

7P(it.2) 7 (Е, 1) + P(it I)

Д Дy + Дy + гор(е,1) Un P(it 1) Ду Ду 7 Р(Е11) 7 (i, 1) 7pi

Ду 72Р.

Ду Ду (Е-1 1) + (Е + 1) д у Д у

Ду

«(n — 1) р 7 Р(Е 1) (Е41)

Ду Ду

Ду где: е — номер шага интегрирования; и — порядок экстраполяции;

Лу — вес кванта подынтегральной функции;

2 (+2) — экстраполированное на один

Ду шаг вперед значение приращения, вычисляемое по формуле экстраполяции и-го порядка; 7 P(i+1)

Ду — приращение интеграла или подынтегральной функции, поступающее от интегратора или сумматора приращений

ЦИМ;

С- р,- 7з р. (е — 1) р. разности приДу hy Ду ращений от первого до (и — 1)-го порядков, полученные в 1-м шаге интегрирования, хранящиеся до (i,+1)-го шага и используемые служат для приема, хранения в течение одного шага интегрирования и выдачи значащих частей соответствующих разностей.

Ниже приводится алгоритм, описывающий работу предлагаемого экстраполятора приращений:

244735

4 7 Р(е+2) для вычисления ду

" (Е+1) Приращение, поступающее на

5 Ду вход 1 экстраполятора, складывается на сум 7Р маторе 2 с инвертированным значением

Ду

10 проходящим через преобразователь 10 кода 7 Р(е . 1) из регистра 18. В то же время + поду ступает в регистр 18 и запоминается в нем до следующего шага. Полученная с помощью 72Р сумматора 2 разность приращений ду поступает на вход сумматора 8 и складывает20 Q P(it 1) ся с (+ ). На выходной шине lб сумматоду

С выхода сумматора 2 разность

Ду поступает на вход сумматора 4 и склады 72 р. вается с инвертированным значением д

30 проходящим через преобразователь ll кода 7 Р(Е-1 1) из регистра 14. В то же время через ду блок 8 выделения значащей части числа поступает в регистр 14 и запоминается в нем до следующего шага. Полученная на суммаЕ 1 торе 4 разность " проходит на вход

Ду

40 сумматора 5 и складывается с числом, поступающим по шине lб из сумматора 8. На вы45 ходной шине 17 сумматора 5 получается экстраполированное значение приращения, вычисленное по формуле экстраполяции третьего порядка.

«(n 1) P(, ) (i 1-1) постуДу

Аналогично разность пает на вход сумматора б и складывается с (— 1) Р; инвертированным значением, прохо55 у дящим через преобразователь 12 кода из (Е+ 2) регистра 15. В то же время (+ ) чеДу

60 рез блок 9 выделения значащей части числа поступает в регистр 15 и запоминается в нем до следующего шага.. Полученная на сумма 7" Р(Е I) торе б разность ) проходит на вход

Ду

65 сумматора 7 и складывается с экстраполирора 8 получается экстраполированное значение приращения, полученное по формуле экстра25 поляции второго порядка.

244735

Предмет изобретения

Составитель А. А. Плащин

Редактор Б. С. Нанкина Техре Л. Я. Левина Корректоры: А. Николаева и А. Абрамова

Заказ 2580, 2 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 ванным значением приращения, вычисленным по формуле экстраполяции (и — 1) -го порядка. На выходе 18 сумматора 7 получается экстраполированное значение приращения +(f-2) вычисленное по формуле экстраhy поляции и-го порядка.

Количество разрядов каждого из регистров устанавливается при проектировании ЦИМ из расчета хранения разности соответствующего порядка.

Сокращение разрядности числа и затем выравнивание весов разрядов перед сложением в дополнительном коде осуществляется с помощью блоков выделения значащей части числа и преобразователя кода. Можно отметить, что выполнение блока выделения значащей части числа требует незначительного объема оборудования. Эта операция легко выполняется, например, с помощью распределенных рабочих импульсов, соответствующих разрядам выделяемой части числа и поступающих по каналам 19 из устройства управления ЦИМ.

Количество сумматоров, используемых в предлагаемом экстраполяторе, незначительно отличается от соответствующего количества в известном экстраполяторе. Количество регистров в предлагаемом экстраполяторе и в известных одинаково и составляет (n — 1).

При использовании предлагаемого изобретения об.ьем экстраполятора уменьшается благодаря уменьшению количества запоминающих элементов в регистрах.

Экстраполятор приращений для цифровой интегрирующей машины с полноразрядными

l0 приращениями, работающий по формуле экстраполяции и-го порядка и с числами, запятая которых фиксирована, содержащий регистры, сумматоры, преобразователи кода и блоки выделения значащей части числа, отли15 чаюи ийся тем, что, с целью экономии оборудования, вход интегратора и сумматора приращений соединен со входами первого и второго сумматоров и со входом первого регистра, выход которого связан со входом первого преобразователя кода, выход первого преобразователя соединен со входом первого сумматора, выход которого соединен со входом второго сумматора, выход второго сумматора связан со входом третьего сумматора, 25 выход первого сумматора подключен ко входу четвертого сумматора и к блоку выделения значащей части числа, выход которого соединен со входом второго регистра, выход которого соединен со .входом преообразователя кода, выход последнего соединен со входом третьего сумматора.