Цифровой фазоразностный манипулятор

Иллюстрации

Показать всеИзобретение относится к технике радиосвязи, в частности к фазоразностным модуляторам с одно- и двукратной относительной фазовой манипуляцией для мощных передатчиков, и может быть использовано в аппаратуре передачи данных. Технический результат заключается в уменьшении величины паразитного изменения длительности информационной посылки в выходном сигнале. Цифровой фазоразностный манипулятор содержит генератор опорной частоты, делитель на восемь, D-триггер, постоянное запоминающее устройство, двухразрядный накапливающий сумматор, регистр, схему И, две схемы ИСКЛЮЧАЮЩЕЕ ИЛИ и формирователь импульса, содержащий последовательный трехразрядный регистр, инвертор и схему И. 1 з.п. ф-лы, 13 ил.

Реферат

Изобретение относится к технике радиосвязи, в частности к фазоразностным модуляторам с одно- и двукратной относительной фазовой манипуляцией для мощных передатчиков, и может быть использовано в аппаратуре передачи данных.

Известно устройство, которое используется как фазоразностный манипулятор [1. Заездный А.М. и др. Фазоразностная модуляция и ее применение для передачи дискретной информации. М., «Связь», 1967, с.62, рис.2.6], содержащий генератор опорной частоты, делитель на восемь, два ключа и дешифратор. На выходе делителя колебание несущей частоты, манипулированное по фазе, представляет собой прямоугольное напряжение, поскольку деление частоты осуществляется на триггерах. Недостаток данного устройства - паразитное изменение длительности информационной посылки в выходном сигнале, вызванное переходными процессами в моменты смены фазы колебания.

Из известных цифровых фазоразностных манипуляторов наиболее близким по технической сущности является цифровой фазоразностный манипулятор [2. Патент РФ №2401514 "Цифровой фазоразностный манипулятор"], содержащий генератор опорной частоты, делитель на восемь, D-триггер, постоянное запоминающее устройство, двухразрядный накапливающий сумматор, формирователь импульса и регистр. На выходе D-триггера колебание несущей частоты, манипулированное по фазе, представляет собой прямоугольное напряжение.

Недостаток данного устройства - паразитное изменение длительности информационной посылки в выходном сигнале, вызванное "привязкой" сигнала информации к сигналу с частотой несущего колебания. Использование данного устройства в передатчике приводит к снижению помехоустойчивости приемных устройств.

Целью изобретения является уменьшение величины паразитного изменения длительности информационной посылки в выходном сигнале.

Поставленная цель достигается тем, что цифровой фазоразностный манипулятор, содержащий последовательно соединенные генератор опорной частоты и делитель на восемь, D-триггер, постоянное запоминающее устройство, двухразрядный накапливающий сумматор, формирователь импульса и регистр, причем второй вход D-триггера соединен с выходом генератора опорной частоты, выход D-триггера является выходом цифрового фазоразностного манипулятора, первый и второй входы двухразрядного накапливающего сумматора являются одноименными информационными входами цифрового фазоразностного манипулятора, третий вход двухразрядного накапливающего сумматора и первый вход формирователя импульса объединены и являются третьим (тактовым) входом цифрового фазоразностного манипулятора, первые два выхода делителя на восемь соединены с соответствующими входами постоянного запоминающего устройства, первый и второй выходы двухразрядного накапливающего сумматора соединены с соответствующими входами регистра, первый и второй выходы регистра соединены с третьим и четвертым входами регистра и с четвертым и пятым входами постоянного запоминающего устройства соответственно, третий и четвертый выходы регистра соединены с шестым и седьмым входами постоянного запоминающего устройства соответственно, выход формирователя импульса соединен с пятым входом регистра и восьмым входом постоянного запоминающего устройства, дополнительно снабжен двумя схемами ИСКЛЮЧАЮЩЕЕ ИЛИ и схемой И, причем второй вход формирователя импульса соединен со вторым выходом делителя на восемь, шестой вход регистра и первый вход первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с третьим выходом делителя на восемь, первый и второй входы схемы И соединены с выходом формирователя импульса и пятым выходом регистра соответственно, второй вход первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ и первый вход второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходом схемы И, третий вход постоянного запоминающего устройства соединен с выходом первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, выход постоянного запоминающего устройства соединен со вторым входом второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которой соединен с первым входом D-триггера.

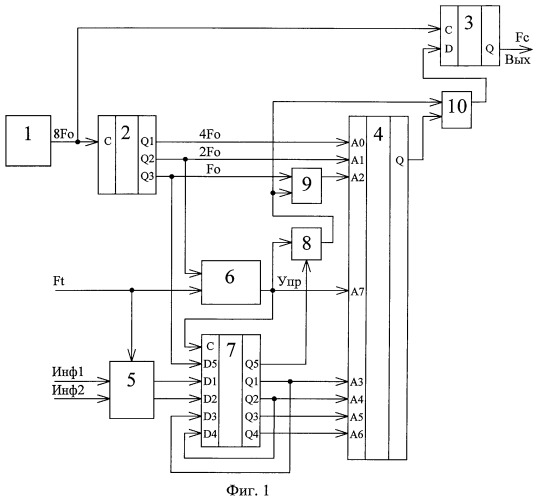

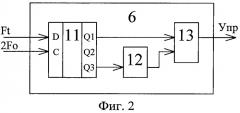

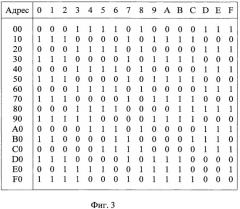

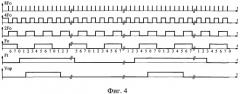

На фиг.1 приведена блок-схема цифрового фазоразностного манипулятора; на фиг.2 - блок-схема формирователя импульса; на фиг.3 - таблица истинности (в шестнадцатеричном коде) постоянного запоминающего устройства; на фиг.4 - эпюры напряжений, поясняющие работу формирователя импульса; на фиг.5 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при отсутствии импульса управления при значениях абсолютной фазы φx выходного колебания, равной 0°, 90°, 180° или 270°; на фиг.6 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 0°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo нулю; на фиг.7 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 270°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo нулю; на фиг.8 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 180°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo нулю; на фиг.9 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 90°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo нулю; на фиг.10 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 0°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo единице; на фиг.11 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 270°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo единице; на фиг.12 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 180°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo единице; на фиг.13 - эпюры напряжения на выходе цифрового фазоразностного манипулятора при смене фазы выходного колебания с фазы φx, равной 90°, на фазу φx+1, равную 0°, 270°, 180° или 90° в момент равенства сигнала Fo единице.

Цифровой фазоразностный манипулятор содержит последовательно соединенные генератор 1 опорной частоты и делитель 2 на восемь, D-триггер 3, постоянное запоминающее устройство 4, двухразрядный накапливающий сумматор 5, формирователь 6 импульса, регистр 7, схему и 8 и две схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и 10, причем второй вход D-триггера 3 соединен с выходом генератора 1 опорной частоты, выход D-триггера 3 является выходом цифрового фазоразностного манипулятора, первый и второй входы двухразрядного накапливающего сумматора 5 являются одноименными информационными входами цифрового фазоразностного манипулятора, третий вход двухразрядного накапливающего сумматора 5 и первый вход формирователя 6 импульса объединены и являются третьим (тактовым) входом цифрового фазоразностного манипулятора, первые два выхода делителя 2 на восемь соединены с соответствующими входами постоянного запоминающего устройства 4, первый и второй выходы двухразрядного накапливающего сумматора 5 соединены с соответствующими входами регистра 7, первый и второй выходы регистра 7 соединены с третьим и четвертым входами регистра 7 и с четвертым и пятым входами постоянного запоминающего устройства 4 соответственно, третий и четвертый выходы регистра 7 соединены с шестым и седьмым входами постоянного запоминающего устройства 4 соответственно, выход формирователя 6 импульса соединен с пятым входом регистра 7, восьмым входом постоянного запоминающего устройства 4 и первым входом схемы И 8, второй вход формирователя 6 импульса соединен со вторым выходом делителя 2 на восемь, шестой вход регистра 7 и первый вход первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 9 соединены с третьим выходом делителя 2 на восемь, второй вход схемы И 8 соединен с пятым выходом регистра 7, второй вход первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и первый вход второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 10 соединены с выходом схемы И 8, третий вход постоянного запоминающего устройства 4 соединен с выходом первой схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 9, выход постоянного запоминающего устройства 4 соединен со вторым входом второй схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 10, выход которой соединен с первым входом D-триггера 3.

Формирователь 6 импульса (см. фиг.2) содержит последовательный трехразрядный регистр 11, инвертор 12 и схему И 13, выход которой является выходом формирователя 6 импульса, первый и второй входы (вход данных и тактовый вход соответственно) последовательного трехразрядного регистра 11 являются одноименными входами формирователя 6 импульса, первый выход (выход первого разряда) последовательного трехразрядного регистра 11 соединен с первым входом схемы И 13, второй выход (выход третьего разряда) последовательного трехразрядного регистра 11 соединен с входом инвертора 12, выход которого соединен со вторым входом схемы И 13.

Цифровой фазоразностный манипулятор работает следующим образом.

Рассмотрим работу цифрового фазоразностного манипулятора на примере работы в режиме двукратной относительной фазовой манипуляции.

Сигнал 8Fo с выхода генератора 1 опорной частоты поступает на счетный вход делителя 2 на восемь и на счетный вход D-триггера 3. Поделенные сигналы 4Fo и 2Fo с выхода делителя 2 на восемь постоянно поступают соответственно на первый и второй входы постоянного запоминающего устройства 4, а сигнал Fo через схему ИСКЛЮЧАЮЩЕЕ ИЛИ 9 - на третий. Причем первый вход является младшим разрядом.

Информация о приращении фазы выходного сигнала (код 11 соответствует сдвигу фазы на +90°, код 10 - сдвигу фазы на +180°, код 01 - сдвигу фазы на +270°, код 00 - сдвигу фазы на +0°), поступающая на вход двухразрядного накапливающего сумматора 5, складывается в накапливающем сумматоре 5 с его выходной и по заднему фронту тактового сигнала Ft переписывается на выход накапливающего сумматора 5. Таким образом, на выходе накапливающего сумматора 5 получается двухразрядный двоичный код абсолютной фазы выходного сигнала: 00 - пропорциональный 0°, 01 - пропорциональный 270°, 10 - пропорциональный 180° или 11 - пропорциональный 90°.

С приходом переднего фронта тактового сигнала Ft на выходе формирователя 6 импульса по переднему фронту сигнала 2Fo формируется сигнал Упр, длительность которого равна периоду сигнала Fo, а его положение "привязано" к середине одного из полупериодов сигнала Fo (см. фиг.2, фиг.4). По переднему же фронту сигнала Упр двухразрядный код абсолютной фазы текущей информационной посылки с выхода накапливающего сумматора 5 записывается на первый и второй выходы регистра 7, а код абсолютной фазы предыдущей информационной посылки переписывается на третий и четвертый выходы регистра 7 соответственно. Одновременно на пятый выход регистра 7 записывается значение сигнала Fo, то есть происходит запоминание: в середине какого из полупериодов сигнала Fo начинается смена фазы выходного сигнала Fc.

Во время действия сигнала Упр на выход схемы И 8 проходит сигнал с пятого выхода регистра 7, схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и 10 работают как повторители или как инверторы (в зависимости от состояния пятого выхода регистра 7), а на выходе постоянного запоминающего устройства 4 формируется сигнал с постепенным (без резких изменений длительности импульса) изменением фазы в соответствии с кодами фаз предыдущей и текущей информационных посылок. Сигнал с выхода постоянного запоминающего устройства 4 поступает через схему ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и D-триггер 3, со сдвигом на один период сигнала 8Fo, на выход цифрового фазоразностного манипулятора (см. фиг.3, фиг.6…13). При этом выходной сигнал Fc сформирован таким образом, чтобы во время смены фазы скважность оставалась равной двум, а длительность полупериодов отличалась от номинального значения не более чем на четверть.

После окончания сигнала Упр, когда переход на текущую фазу завершен, на выходе схемы И 8 присутствует логический ноль, схемы ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и 10 работают как повторители, а на выходе устройства формируется сигнал Fc с абсолютной фазой 0°, 90°, 180° или 270° в соответствии с записанным на первом и втором выходах регистра 7 кодом (00, 11, 10 или 01 соответственно) текущей абсолютной фазы выходного сигнала (см. фиг.3, фиг.5).

Работа цифрового фазоразностного манипулятора в режиме однократной относительной фазовой манипуляции отличается от работы в режиме двукратной относительной фазовой манипуляции только тем, что на первый (младший) вход накапливающего сумматора 5 постоянно подается логический ноль. При этом фаза выходного сигнала Fc в зависимости от начального состояния первого (младшего) выхода накапливающего сумматора 5 имеет всегда два значения: 0°, 180° или 90°, 270°.

Таким образом, использование данного устройства в передатчике в качестве модулятора позволит (за счет "привязки" начала смены фазы колебания к сигналу с удвоенной несущей частотой) уменьшить величину паразитного изменения длительности информационной посылки в выходном сигнале.

Источники информации

1. Заездный А.М. и др. Фазоразностная модуляция и ее применение для передачи дискретной информации. М., «Связь», 1967, с.62, рис.2.6.

2. Патент РФ №2401514 Цифровой фазоразностный манипулятор.

1. Цифровой фазоразностный манипулятор, содержащий последовательно соединенные генератор опорной частоты и делитель на восемь, D-триггер, постоянное запоминающее устройство, двухразрядный накапливающий сумматор, формирователь импульса и регистр, причем второй вход D-триггера соединен с выходом генератора опорной частоты, выход D-триггера является выходом цифрового фазоразностного манипулятора, первый и второй входы двухразрядного накапливающего сумматора являются одноименными информационными входами цифрового фазоразностного манипулятора, третий вход двухразрядного накапливающего сумматора и первый вход формирователя импульса объединены и являются третьим (тактовым) входом цифрового фазоразностного манипулятора, первые два выхода делителя на восемь соединены с соответствующими входами постоянного запоминающего устройства, первый и второй выходы двухразрядного накапливающего сумматора соединены с соответствующими входами регистра, первый и второй выходы регистра соединены с третьим и четвертым входами регистра и с четвертым и пятым входами постоянного запоминающего устройства соответственно, третий и четвертый выходы регистра соединены с шестым и седьмым входами постоянного запоминающего устройства соответственно, выход формирователя импульса соединен с пятым входом регистра и восьмым входом постоянного запоминающего устройства, отличающийся тем, что дополнительно снабжен двумя схемами исключающее или и схемой И, причем второй вход формирователя импульса соединен со вторым выходом делителя на восемь, шестой вход регистра и первый вход первой схемы исключающее или соединены с третьим выходом делителя на восемь, первый и второй входы схемы И соединены с выходом формирователя импульса и пятым выходом регистра соответственно, второй вход первой схемы исключающее или и первый вход второй схемы исключающее или соединены с выходом схемы И, третий вход постоянного запоминающего устройства соединен с выходом первой схемы исключающее или, выход постоянного запоминающего устройства соединен со вторым входом второй схемы исключающее или, выход которой соединен с первым входом D-триггера.

2. Цифровой фазоразностный манипулятор по п.1, отличающийся тем, что формирователь импульса выполнен на последовательном трехразрядном регистре, инверторе и схеме И, выход которой является выходом формирователя импульса, первый и второй входы (вход данных и тактовый вход соответственно) последовательного трехразрядного регистра являются одноименными входами формирователя импульса, первый выход последовательного трехразрядного регистра (выход первого разряда) соединен с первым входом схемы И, второй выход последовательного трехразрядного регистра (выход третьего разряда) соединен с входом инвертора, выход которого соединен со вторым входом схемы И.