Устройство хранения информации с обнаружением одиночных и двойных ошибок

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении достоверности функционирования устройства за счет обнаружения 100% двойных ошибок. Устройство хранения информации с обнаружением одиночных и двойных ошибок, содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок выявления ошибки, блок элементов И, элемент И, элемент ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка». 1 ил., 1 табл.

Реферат

Изобретение относится к вычислительной технике и может быть использована для повышения достоверности функционирования запоминающих устройств.

Известно самокорректирующееся устройство [1] использующие корректирующий код (наиболее часто используется код Хемминга, корректирующий одиночную ошибку и обнаруживающий двойную ошибку) для обнаружения и коррекции ошибок, содержащее исходный вычислительный канал (запоминающее устройство), кодирующее устройство, избыточный вычислительный канал (для хранения значений контрольных разрядов), блок вычисления синдрома, дешифратор, корректор, входы устройства подключены к входам исходной схемы и к входам кодирующего устройства, выходы которого подключены к первым входам блока вычисления синдрома, выходы исходного вычислительного канала подключены к вторым входам блока вычисления синдрома и к первым входам корректора, выходы блока вычисления синдрома подключены к входам дешифратора, соединенного своими выходами со вторыми входами корректора, выходы корректора являются выходами устройства.

Недостатком устройства является большая информационная избыточность (большое число контрольных разрядов) и как следствие аппаратурная избыточность связанная с необходимостью хранения значений контрольных разрядов.

Наиболее близким по техническому решению является отказоустойчивое оперативное запоминающее устройство [2], содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок выявления ошибки, блок элементов И, элемент И, элемент ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», входной блок кодирования формирует значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов х1, х2, х3, у1, у2, у3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕у1⊕у2; r2=х2⊕х3⊕у2⊕у3, выходной блок кодирования формирует значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов х1С, х2С, х3С, у1С, у2С, у3С, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=х1С⊕х2С⊕у1С⊕у2С; r2П=х2С⊕х3С⊕у2С⊕у3С, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные символы поступают на пятые входы узла памяти совместно с контрольными символами, полученными из информационных символов с помощью входного блока кодирования, вход синхронизации подключен к шестому входу узла памяти и к первым входам блока элементов И и элемента И, информационные символы с информационных выходов узла памяти поступают на вторые входы блока элементов И и на входы выходного блока кодирования, выходные символы выходного блока кодирования поступают на первые входы блока выявления ошибки, на вторые входы которого поступают контрольные символы с информационных выходов узла памяти, выходы блока выявления ошибки подключены к входам элемента ИЛИ, выход элемента ИЛИ подключен к второму входу элемента И, выходы блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала «ошибка».

Недостатком устройства является недостаточная достоверность функционирования устройства т.к. используемый метод кодирования имеет недостаточную обнаруживающую способность двойных ошибок.

Целью изобретения является повышение достоверности функционирования устройства за счет обнаружения 100% двойных ошибок.

Поставленная цель достигается тем, что устройство, содержащие узел памяти, входной блок кодирования, выходной блок кодирования, блок выявления ошибки, блок элементов И, элемент И, элемент ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», входной блок кодирования формирует значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов х1, х2, х3, у1, у2, у3, поступающих на входы входного блока кодирования, в соответствии с правилом: r1=х1⊕х2⊕у1⊕у2; r2=х2⊕х3⊕у2⊕у3, выходной блок кодирования формирует значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов х1С, х2С, х3С, у1С, у2С, у3С, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r1П=х1С⊕х2С⊕у1С⊕у2С; r2П=х2С⊕х3С⊕у2С⊕у3С, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы, подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные символы поступают на пятые входы узла памяти совместно с контрольными символами, полученными из информационных символов с помощью входного блока кодирования, вход синхронизации подключен к шестому входу узла памяти и к первым входам блока элементов И и элемента И, информационные символы с информационных выходов узла памяти поступают на вторые входы блока элементов И и на входы выходного блока кодирования, выходные символы выходного блока кодирования поступают на первые входы блока выявления ошибки, на вторые входы которого поступают контрольные символы с информационных выходов узла памяти, выходы блока выявления ошибки подключены к входам элемента ИЛИ, выход элемента ИЛИ подключен к второму входу элемента И, выходы блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала «ошибка», отличается тем, что оно дополнительно содержит два контрольных разряда r3 и r4 значения которых формируются путем сложения по модулю 2 информационных символов x1, x2, x3, у1, у2, y3, поступающих на входы входного блока кодирования, в соответствии с правилом: r3=x1⊕х2⊕х3 и r4=y1⊕у2⊕y3, выходной блок кодирования формирует значения проверочных контрольных разрядов r3П, r4П путем сложения по модулю 2 информационных символов х1С, х2С, х3С, у1С, у2С, у3С, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом: r3П=x1C⊕х2С⊕х3С и r4П=y1C⊕у2С⊕y3C, причем значения символов контрольных разрядов r3 и r4, полученными из информационных символов с помощью входного блока кодирования, поступают на шестые входы узла памяти, значения символов контрольных разрядов r3П и r4П, полученными при считывании информации с информационных выходов узла памяти с помощью выходного блока кодирования, поступают на третьи входы блока выявления ошибки, на четвертые входы которого поступают контрольные символы r3, r4 с выходов узла памяти.

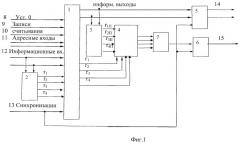

На фиг.1 представлена блок-схема устройства. Устройство хранения информации с обнаружением одиночных и двойных ошибок содержит: узел 1 памяти, входной блок 2 кодирования, выходной блок 3 кодирования, блок 4 выявления ошибки, блок 5 элементов И, элемент 6 И, элемент 7 ИЛИ, вход 8 установки в нулевое состояние, вход 9 записи, вход 10 считывания, адресные входы 11, информационные входы 12, вход 13 синхронизации, информационные выходы 14, выход 15 сигнала "ошибка".

Вход 8 установки в нулевое состояние, вход 9 записи, вход 10 считывания, адресные входы 11, подключены соответственно к первому, второму, третьему и четвертому входам узла 1 памяти, информационные входы 12 подключены к пятым входам узла 1 памяти и к входам входного блока 2 кодирования, выходы которого подключены к шестым входам узла 1 памяти, вход синхронизации подключен к седьмому входу узла 1 памяти и к первым входам блока 5 элементов И и элемента 6 И, первые выходы узла 1 памяти подключены к входам выходного блока 3 кодирования и к вторым входам блока 5 элементов И, первые выходы выходного блока 3 кодирования подключены к первым входам блока 4 выявления ошибки, к вторым входам которого подключены вторые выходы узла 1 памяти, вторые выходы выходного блока 3 кодирования подключены к третьим входам блока 4 выявления ошибки, к четвертым входам которого подключены третьи выходы узла 1 памяти, а выходы подключены к входам элемента 7 ИЛИ, выход элемента 7 ИЛИ подключен к второму входу элемента 6 И, выходы блока 5 элементов И являются информационными выходами 14 устройства, выход элемента 6 И является выходом 15 сигнала «ошибка».

Узел 1 памяти, в данном случае, представляет собой статическое полупроводниковое оперативное устройство памяти и предназначен для хранения кодовых наборов: УК=x1x2x3 y1y2 y3 r1 r2 r3 r4, полученных при кодировании исходных двоичных наборов: У=x1,x2,x3, y1,y2,y3.

Входной блок 2 кодирования предназначен для формирования значений контрольных разрядов r1, r2, r3, r4 путем сложения по mod2 информационных символов в соответствии с правилом:

r1=x1⊕x2⊕y1⊕y2;

r2=x2⊕x3⊕y2⊕y3.

r3=x1⊕x2⊕x3;

r4=y1⊕y2⊕y3.

Выходной блок 3 кодирования предназначен для формирования значений проверочных контрольных разрядов r1П, r2П путем сложения по mod2 информационных символов (xiC, yiC), полученных при считывании информации с узла 1 памяти в соответствии с правилом:

r1П=x1C⊕x2C⊕y1C⊕y2C;

r2П=x2C⊕x3C⊕y2C⊕y3C;

r3П=x1C⊕x2C⊕x3C;

r4П=y1C⊕y2C⊕y3C.

Блок 4 выявления ошибки предназначен для обнаружения ошибки в кодовом наборе при считывании информации с узла 1 памяти путем сложения по mod2 значений контрольных разрядов r1C, r2C, r3C и r4C, считываемых с вторых выходов узла 1 памяти, соответственно с значениями контрольных разрядов r1П, r2П, r3П и r4П, сформированных на выходах выходного блока 3 кодирования.

Результат поразрядного сложения:

λ1=r1C⊕r1П;

λ2=r2C⊕r2П;

λ3=r3C⊕r3П;

λ4=r4C⊕r4П;

Нулевой результат суммы свидетельствует об отсутствии ошибки, и ее наличии в противном случае.

Выходы λ1, λ2 λ3 и λ4 блока 4 выявления ошибки объеденены в один выход элементом 7 ИЛИ, значение сигнала на данном выходе поступает на второй вход элемента 6 И.

Считывание выходной информации с выходов устройства проводится при поступлении сигнала с входа синхронизации на первые входы блока 5 элементов И и элемента 6 И.

Устройство работает следующим образом. Перед началом работы устройства на вход 8 "установки в нулевое состояние" подается единичный сигнал, который переводит устройство в нулевое состояние.

При записи информации в узел 1 памяти, подаются единичные сигналы на вход 13 синхронизации, вход 9 записи, адресные входы 11 и информационные входы 12.

Например, на информационные входы поступает кодовая комбинация: х1х2х3 у1у2у3 соответствующая значению - 000110

В этом случае входной блок 2 кодирования формирует вектор r1=х1⊕х2⊕у1⊕у2=0; r2=x2⊕x3⊕у2⊕у3=1; r3=x1⊕x2⊕x3=0; r4=у1⊕y2⊕у3=0;

Соответственно в узел 1 памяти запишется информация: 0001100100.

При считывании информации на вход 10 устройства подается сигнал, разрешающий считывание информации с узла 1 памяти. Если ошибки нет, то выходной блок 3 кодирования относительно информационных разрядов формирует значения: r1П=0 и r2П=1, r3П=0 и r4П=0, которые равны соответственно значениям r1C, r2C, r3C, r4C, поэтому на выходе блока 4 выявления ошибки имеем значения: λ1=0, λ2=0, λ3=0, λ4=0,

Допустим, произошла ошибка в первом информационном разряде:

1* 00 110 0100. В этом случае на выходах выходного блока 3 кодирования получим значения сигналов: r1П=1, r2П=1, r3П=1, r4П=0.

Так как значение r1П≠r1C, то на выходе блока 4 выявления ошибки получим значения сигналов: λ1=1, λ2=0, λ3=1, λ4=0, соответственно на выходе элемента 7 ИЛИ появится единичное значение сигнала, которое при поступлении сигнала с входа 13 синхронизации поступит на выход элемента 6 И, что свидетельствует о возникновении ошибки. Аналогичным образом полезная модель работает при появлении других одиночных и двойных ошибках.

Таким образом, в предлагаемом устройстве хранения информации обнаруживаются все одиночные ошибки и двойные при меньшем числе контрольных разрядов (меньших аппаратурных затратах на хранение значений контрольных разрядов в накопителе информации) по отношению к коду Хемминга, получено требуемое значение достоверности функционирования устройства хранения информации рациональным введением необходимого числа контрольных разрядов.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Щербаков Н.С. Достоверность работы цифровых устройств. М: Машиностроение, 1989, с.82, рис.39., 224 с.

2. Патент на изобретение №2403615 "Устройство хранения и передачи информации с обнаружением двойных ошибок / Павлов А.А., Царьков А.Н. и др.от 27.01.2009 г.

Приложение к заявке на изобретение: «Устройство хранения информации с обнаружением одиночных и двойных ошибок»

Так как достоверность функционирования устройств хранения информации существенно зависит от выбранного метода обнаружения ошибок: - обнаруживающей способности выбранного метода контроля информации и аппаратурных затрат, необходимых для реализации данного метода (надежности аппаратуры контроля), то для данных устройств существует необходимость в разработке методов, позволяющих обнаруживать ошибки требуемой кратности без значительного увеличения аппаратурных затрат по отношению к известным методам.

Для исходной информации, представленной на k-информационных разрядах, имеем множество Nk=2k рабочих или разрешенных комбинаций.

Для получения возможности обнаружения или исправления ошибок на данном множестве, к информационным разрядам добавляется r-контрольных разрядов, в результате получаем кодовый набор n=k+r.

В этом случае для множества возможных кодовых наборов N=2n только множество кодовых наборов Nk (Nk<N) являются разрешенными, остальные (N-Nk) кодовые наборы являются запрещенными. При этом разрешенные кодовые наборы отличаются на d-разрядах, называемых кодовым расстоянием или хемминговым расстоянием.

Если выполняется условие d≥t+1 (где t - число ошибочных разрядов в кодовом наборе), то любая ошибка кратности не более t может быть обнаружена.

Если все разрешенные кодовые наборы разнести на кодовое расстояние d≥2t+1, то любая ошибка кратности не более t может быть исправлена.

В прототипе изобретения [1] для этих целей предлагается использовать метод обнаружения одиночных и двойных ошибок, реализующий следующие правило кодирования информации:

произвольного числа информационных правила кодирования информации для двух контрольных разрядов включает следующие правила:

1) Двоичный набор разбивается на блоки информации (пусть число информационных разрядов кратно трем), по три разряда в каждом блоке:

2) Проводится формирование значений двух контрольных разрядов по правилу:

В результате кодирования получим кодовый набор:

или:

Пример. Пусть число информационных разрядов равно шести, тогда, для рассматриваемого числа информационных разрядов имеем кодовый набор:

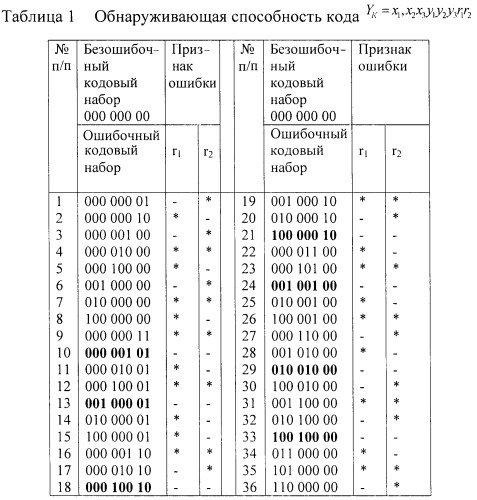

В табл.1 представлены ошибочные кодовые наборы для одиночных и двойных ошибок относительно безошибочного кодового набора: 000000 00.

Примечание. Символом "*" обозначен признак обнаруживаемой ошибки в соответствующем контрольном разряде, символом "-" - не обнаруживаемой.

Анализ табл.1 позволяет выявить следующие свойства предлагаемого кода:

Свойство 1. Предлагаемый код обнаруживает 100% одиночных ошибок.

Свойство 2. Предлагаемый код не обнаруживает двойные ошибки, вызванные одиночными ошибками в одноименных разрядах блоков информации (ошибки представленные в строках 24, 29, 33 табл.1), и двойные вызванные одиночными ошибками в информационных разрядах и одиночными ошибками в контрольных разрядах (ошибки, представленные строками 10, 13, 18 табл.1) т.к. данные ошибки приводят к нулевому значению синдрома ошибки ("маскируются").

Свойство 3. Увеличение числа информационных разрядов ведет к снижению обнаруживающей способности двойных ошибок предлагаемого кода.

В общем случае, число не обнаруживаемых ошибок рассматриваемого кода равно:

где w - число блоков информационных разрядов.

В связи с тем, что с увеличением числа информационных разрядов предлагаемый код снижает свои обнаруживающие способности двойных ошибок, возникает необходимость компенсировать данный недостаток за счет введения дополнительных контрольных разрядов.

Построение модифицированного кода повышенной обнаруживающей способности рассмотрим на примере кодового набора, содержащего два информационных блока (см. табл.1), двойные ошибки не обнаруживаются в семи кодовых наборах:

Анализ представленных кодовых наборов показывает, что для обнаружения 100% двойных ошибок (выполнения условия d≥3 необходимо) ввести два дополнительных разряда, реализующий функцию:

и

Тогда кодовый набор модифицированного линейного кода для шести информационных разрядов, позволяющий обнаружить все одиночные и двойные ошибки, может быть представлен в виде:

или: Yk6MM=x1x2x3, y1y2y3, r1r2r3r4.

При использовании кода Хемминга для обнаружения (коррекции) одиночных ошибок количество контрольных разрядов rX=n-k определяется из следующего неравенства:

2k-1<1+k+rX≤2k

или rX==log2(n+1).

В этом случае для шести информационных разрядов потребуется четыре контрольных разряда, код корректирует одиночные ошибки и обнаруживает 18% двойных ошибок.

При использовании модифицированного кода Хемминга для коррекции одиночных и обнаружения двойных ошибок потребуется пять контрольных разрядов, т.е. предлагаемый метод обнаружения ошибок требует на один контрольный разряд меньше.

Во многих случаях для получения требуемого значения достоверности функционирования устройства хранения информации, целесообразно ограничить число вводимых дополнительных контрольных разрядов. При этом необходимо выбрать дополнительную проверку, в которой обнаруживается наибольшее количество двойных ошибок, желательно в старших разрядах двоичного набора (оказывающих наибольшее влияние на погрешность вычислений).

В рассматриваемом примере целесообразно использовать один дополнительный контрольный разряд r3, на котором обнаруживается четыре двойных ошибки из семи, расположенных в старших разрядах информации (строки 21, 24, 29, 33 табл.1).

Таким образом, предлагаемый метод обнаружения ошибок позволяет обнаруживать все одиночные ошибки и двойные при меньшем числе контрольных разрядов (меньших аппаратурных затратах на хранение значений контрольных разрядов в накопителе информации) по отношению к коду Хемминга, получить требуемое значение достоверности функционирования устройства хранения информации рациональным введением необходимого числа контрольных разрядов.

1. Патент на изобретение №2403615 "Устройство хранения и передачи информации с обнаружением двойных ошибок" / Павлов А.А., Царьков А.Н. и др. от 27.01.2009 г.

Устройство хранения информации с обнаружением одиночных и двойных ошибок, содержащее узел памяти, входной блок кодирования, выходной блок кодирования, блок выявления ошибки, блок элементов И, элемент И, элемент ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», входной блок кодирования формирует значения контрольных разрядов r1 и r2 путем сложения по модулю 2 информационных символов x1, х2, х3, y1, у2, у3, поступающих на входы входного блока кодирования, в соответствии с правилом r1=x1⊕x2⊕y1⊕y2; r2=х2⊕х3⊕у2⊕у3, выходной блок кодирования формирует значения проверочных контрольных разрядов r1П, r2П путем сложения по модулю 2 информационных символов х1С, х2С, х3С, y1С, у2С, у3С, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом r1П=х1С⊕х2С⊕у1С⊕у2С; r2П=х2С⊕х3Сс⊕у2С⊕у3С, вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные символы поступают на пятые входы узла памяти совместно с контрольными символами, полученными из информационных символов с помощью входного блока кодирования, вход синхронизации подключен к шестому входу узла памяти и к первым входам блока элементов И и элемента И, информационные символы с информационных выходов узла памяти поступают на вторые входы блока элементов И и на входы выходного блока кодирования, выходные символы выходного блока кодирования поступают на первые входы блока выявления ошибки, на вторые входы которого поступают контрольные символы с информационных выходов узла памяти, выходы блока выявления ошибки подключены к входам элемента ИЛИ, выход элемента ИЛИ подключен к второму входу элемента И, выходы блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала «ошибка», отличающееся тем, что оно дополнительно содержит два контрольных разряда r3 и r4 значения которых формируются путем сложения по модулю 2 информационных символов х1, х2, х3, у1, у2, y3, поступающих на входы входного блока кодирования, в соответствии с правилом r3=х1⊕х2⊕х3 и r4=y1⊕y2⊕y3, выходной блок кодирования формирует значения проверочных контрольных разрядов r3П, r4П путем сложения по модулю 2 информационных символов x1C, х2С, х3C, y1C, y2C, y3C, поступающих на входы выходного блока кодирования и полученных при считывании информации с информационных выходов узла памяти в соответствии с правилом r3П=x1С⊕х2С⊕х3С и r4П=y1С⊕y2С⊕y3С, причем значения символов контрольных разрядов r3 и r4, полученных из информационных символов с помощью входного блока кодирования, поступают на шестые входы узла памяти, значения символов контрольных разрядов r3П и r4П, полученных при считывании информации с информационных выходов узла памяти с помощью выходного блока кодирования, поступают на третьи входы блока выявления ошибки, на четвертые входы которого поступают контрольные символы r3, r4 с выходов узла памяти.