Управляемая линия задержки

Иллюстрации

Показать всеИзобретение относится к области информационных технологий, к системам и технологиям регулирования, управления скорости информационного потока цифровых данных и аналоговых сигналов. Техническим результатом является расширение функциональных возможностей линии задержки посредством регулирования скорости поступающего информационного потока в сторону ее повышения или снижения. Линия задержки содержит n двухвходовых мультиплексоров, n выходы которых соединены с n входами адресной выборки данных ОЗУ, n-разрядный двоичный счетчик адреса записи данных ОЗУ с n входами установки кода задаваемой величины управляемой задержки, n-разрядный двоичный счетчик адреса чтения данных ОЗУ с n входами установки кода задаваемой величины управляемой задержки, при этом первые входы n двухвходовых мультиплексоров соответственно соединены с n выходами двоичного счетчика адреса записи данных ОЗУ, а вторые входы n двухвходовых мультиплексоров соответственно соединены с n выходами двоичного счетчика адреса чтения данных ОЗУ, причем управляющие входы n двухвходовых мультиплексоров объединены между собой и соединены с выходом ДПКД, тот же выход ДПКД соединен со счетными входами двоичных счетчиков адресов записи чтения данных ОЗУ, управляющие коэффициентом деления выводы ДПКД определяют необходимую величину дискрета управления линии задержки. 2 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к области информационных технологий, систем временной синхронизации информационных потоков, автоматики, средств связи, радиолокации, радионавигации и других, в частности, к системам и технологиям регулирования, управления скорости информационного потока цифровых данных и аналоговых сигналов.

Известна линия задержки по патенту [1], формирующая на своем выходе импульсы с задержкой, не превышающей длительность поступающих импульсов. Недостатком данной линии задержки является то, что задержанные импульсы формируются только при наличии поступающих импульсов по их фронтам. Это обстоятельство ограничивает возможность применения данной линии задержки для последовательности импульсов с задержкой, превышающей их длительность. Такие требования к линии задержки могут возникать в случаях, например, при регулировании скорости поступающих данных информационного потока.

Также известно устройство задержки импульсных сигналов по патенту [2], принятое в качестве прототипа данного изобретения и содержащее генератор тактовых импульсов, выход которого соединен с входом делителя с переменным коэффициентом деления (ДПКД), оперативное запоминающее устройство (ОЗУ), формирующее необходимые задержанные импульсы относительно поступающих импульсов с использованием вычислительных процедур на сумматоре. Применяемое в устройстве ОЗУ служит для кратковременного хранения кодов задержки импульсов и выполняет предназначенные известные функции оперативной памяти. Недостатком данного устройства также является формирование соответственно задержанного импульса относительно поступающего импульсного сигнала. Полученная, таким образом, последовательность импульсов, задержанная относительно фронтов поступающих импульсов, всегда будет запаздывать по времени и не позволит получения последовательности импульсов, превышающей скорость поступающего информационного потока. В известных устройствах задержки такая возможность исключается в связи с запаздыванием импульсов, сформированных относительно фронтов поступающих импульсов.

Целью предлагаемого изобретения является расширение функциональных возможностей работы линии задержки в части реализации изменения и регулирования длительности интервалов времени в тракте прохождения поступающих данных информационного потока. В этом случае независимо от наличия импульсов, их длительностей в информационном потоке мы получаем возможность управления скоростью следования импульсов поступающего информационного потока. Таким образом, управляя длительностью интервалов времени прохождения информационного потока в линии задержки, мы получаем возможность регулирования скорости информационного потока в любую сторону повышения скорости или ее снижения. Такая возможность регулировать скорость линии задержки информационного потока может найти применение для синхронизации информационных потоков в транспортных сетях передачи данных, возникающих из-за расхождения частот генераторов передающих и приемных узлов [3].

Указанная цель достигается тем, что в предлагаемой линии задержки, имеющей, по меньшей мере, внешний вывод для приема поступающих данных, внешний вывод для выдачи задержанных данных, внешние выводы для приема команд управления величиной задержки, содержащей задающий генератор импульсов, выход которого соединен со счетным входом делителя с переменным коэффициентом деления (ДПКД), соответственно организованную систему элементов ячеек памяти оперативного запоминающего устройства (ОЗУ), емкостью двумерной матрицы p×2n бит, где p - количество одновременно, параллельно записываемых/считываемых данных ОЗУ по адресно управляемой выборке 2n бит с выводами записи/чтения данных ОЗУ, также имеющего n выводов для адресной выборки записи/чтения данных ОЗУ, дополнительно введены n двухвходовые мультиплексоры, n выходы которых соединены с n входами адресной выборки данных ОЗУ, n-разрядный двоичный счетчик адреса записи данных ОЗУ с n входами установки кода задаваемой величины управляемой задержки, n-разрядный двоичный счетчик адреса чтения данных ОЗУ с n входами установки кода задаваемой величины управляемой задержки, при этом первые входы n двухвходовых мультиплексоров соответственно соединены с n выходами двоичного счетчика адреса записи данных ОЗУ, а вторые входы n двухвходовых мультиплексоров соответственно соединены с n выходами двоичного счетчика адреса чтения данных ОЗУ, причем управляющие входы n двухвходовых мультиплексоров объединены между собой и соединены с выходом ДПКД, тот же выход ДПКД соединен со счетными входами двоичных счетчиков адресов записи чтения данных ОЗУ, управляющие коэффициентом деления, выводы ДПКД определяют необходимую величину дискрета управления линии задержки, кроме этого при использовании ОЗУ с организацией памяти p=1 она трансформируется в линию задержки цифровых данных информационного потока, при этом вход записи данных ОЗУ соединен с внешним выводом для приема поступающих данных, а выход чтения данных ОЗУ соединен с внешним выводом для выдачи задержанных данных, а при использовании ОЗУ с организацией памяти p>1 она трансформируется в линию задержки аналоговых сигналов и дополнительно содержит p-разрядный аналого-цифровой преобразователь (АЦП) также p-разрядный цифроаналоговый преобразователь (ЦАП), при этом внешний вывод для приема поступающих данных соединен с аналоговым входом АЦП, p выходы которого соответственно соединены с p входами записи данных ОЗУ, а p выходы чтения данных ОЗУ соответственно соединены с p входами ЦАП, выход которого соединен с внешним выводом для выдачи задержанных данных.

Сопоставительный анализ с прототипом показывает, что предложенная управляемая линия задержки позволяет управлять скоростью поступающего информационного потока, например, для решения задач временной синхронизации информационных потоков, для автоматической подстройки скорости поступающих данных и других применений. Предложенная управляемая линия задержки также может работать с оцифрованными данными поступающих аналоговых сигналов. Возможность регулирования скорости поступающего информационного потока в сторону ее повышения или снижения расширяет функциональные возможности применения данной линии задержки в различных устройствах электронной техники. Предложенная линия задержки, выполненная в виде монолитной интегральной микросхемы, найдет применение у разработчиков микроэлектронной техники.

Проведенный анализ изобретательского уровня, включающий поиск по патентным и научно-техническим источникам информации и выявление источников, содержащих сведения об аналогах заявляемого устройства, позволяет установить, что заявителем не обнаружены решения, характеризующиеся признаками, идентичными всем существенным признакам заявленного изобретения. Определение из перечня выявленных аналогов, прототипа позволило выявить совокупность существенных отличительных признаков в заявляемом объекте, изложенную в формуле изобретения. Следовательно, заявляемое изобретение соответствует требованию "новизна" по действующему законодательству. Сведений об известности отличительных признаков известных технических решений с достижением такого же, как у заявляемого устройства, положительного эффекта не имеется. На основании этого сделан вывод, что предлагаемое техническое решение соответствует критерию "изобретательский уровень".

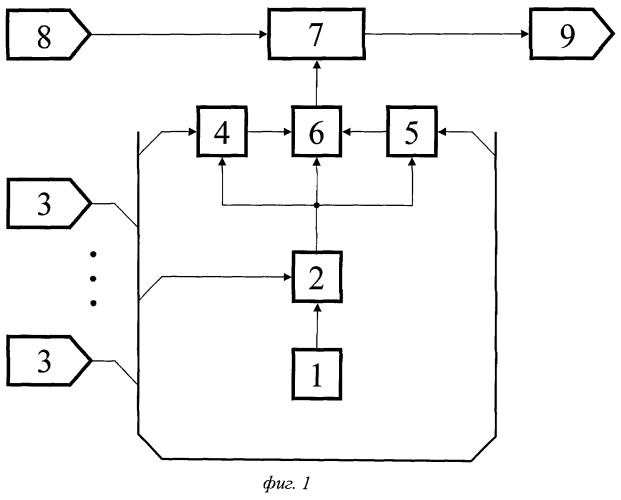

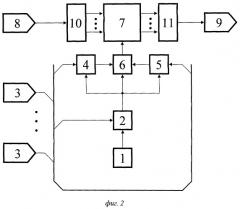

На фигуре 1 представлена блок-схема управляемой линии задержки цифровых данных информационного потока, содержащая задающий генератор 1 импульсных сигналов, выход которого соединен со счетным входом делителя с переменным коэффициентом деления (ДПКД) 2, выводы, задающие коэффициент деления, которые соединены с группой внешних выводов 3 для приема команд управления задержкой, при этом выход ДПКД 2 соединен со счетным входом n-разрядного двоичного счетчика адреса записи 4 данных ОЗУ и со счетным входом n-разрядного двоичного счетчика адреса чтения 5 данных ОЗУ, также с управляющими входами n двухвходовых мультиплексоров 6, n выходы которых соединены с n входами адресной выборки данных ОЗУ 7, вход записи данных которого соединен с внешним выводом 8 для приема поступающих данных, а вывод чтения данных ОЗУ 7 соединен с внешним выводом 9 для выдачи задержанных данных, кроме этого n выходов счетчика адреса записи 4 данных ОЗУ 7 соответственно соединены с первыми входами n двухвходовых мультиплексоров 6, a n выходы счетчика адреса чтения 5 данных ОЗУ 7 соответственно соединены со вторыми входами n двухвходовых мультиплексоров 6, кроме того, выводы установки кодов задержки счетчиков адресов записи 4, чтения 5 данных ОЗУ 7 соответственно соединены с группой внешних выводов 3 для приема кодов управления задержкой. На фигуре 2 представлена блок-схема управляемой линии задержки аналоговых сигналов, где в отличие от линии задержки по фигуре 1 оперативное запоминающее устройство (ОЗУ) 7 использовано с организацией памяти p×2n бит, где p>1, кроме этого дополнительно содержит p-разрядный аналого-цифровой преобразователь (АЦП) 10, аналоговый вход которого соединен с внешним выводом 8 для приема поступающих данных, а p выходы АЦП 10 соответственно соединены с p входами записи данных ОЗУ 7, кроме того, линия задержки дополнительно содержит p-разрядный цифроаналоговый преобразователь (ЦАП) 11, p входы которого соответственно соединены с p выходами чтения данных ОЗУ 7, а аналоговый выход ЦАП 11 соединен с внешним выводом 9 для выдачи задержанных данных.

Представленная управляемая линия задержки работает следующим образом. Основным элементом линии задержки является оперативное запоминающее устройство ОЗУ 7, имеющее вход записи данных, выход чтения данных и n-разрядный вход адресной выборки данных. Рассмотрим работу линии задержки цифровых данных информационного потока, когда используется одноразрядное ОЗУ (p=1) по блок-схеме фигуры 1. ОЗУ для выполнения функции линии задержки работает в динамическом режиме непрерывного увеличения (приращения адреса на единицу) адресной выборки для записи непрерывно поступающих данных информационного потока и их считывания. Для этого генератор импульсных сигналов 7 вырабатывает последовательность импульсов, поступающих на счетный вход делителя с переменным коэффициентом деления ДПКД 2, который формирует на своем выходе тактовые импульсы со скважностью два. Период повторения тактовых импульсов на выходе ДПКД 2 определяется кодом установки коэффициента деления ДПКД 2 на группе внешних выводов 3. При этом длительность периода тактовых импульсов ДПКД будет определять величину дискрета управления линии задержки. Тактовые импульсы с выхода ДПКД 2 поступают на счетные входы n-разрядных двоичных счетчиков адресов записи 4 и чтение 5 данных ОЗУ 7. Таким образом, за каждый период тактового интервала происходит синхронное приращение содержимого двоичных счетчиков адресов 4, 5 на единицу. Тактовые импульсы с выхода ДПКД 2 также поступают на управляющие входы n двухвходовых мультиплексоров 6, переключающих n выходы счетчиков адресов 4, 5 на n входы адресной выборки данных ОЗУ 7. В результате переключения двухвходовых мультиплексоров за первый полупериод действия тактовых импульсов осуществляется подключение содержимого счетчика адреса записи 4 данных ОЗУ на вход адресной выборки данных ОЗУ, а за второй полупериод действия тактового интервала подключается содержимое счетчика адреса чтения 5 на вход адресной выборки данных ОЗУ. Функциональное разделение операций записи и считывания данных ОЗУ, выполненное на отдельных двоичных счетчиках адресов, позволяет упростить реализацию принятого динамического режима работы ОЗУ. Поступающие через внешний вывод 8 данные информационного потока последовательно записываются в ячейках памяти ОЗУ в темпе длительности тактовых импульсов дискрета управления величиной задержки, в таком же темпе считываются данные информационного потока и выдаются на внешний вывод 9. Теперь рассмотрим вопросы формирования и управления величиной задержки в ячейках памяти ОЗУ 7. Рассмотрим первый вариант работы линии задержки, когда содержимое счетчиков адресов записи и чтения 4, 5 одинаковые, тогда в первом полупериоде счетного тактового импульса осуществляется запись бита поступающих данных ячейки памяти ОЗУ 7 и тут же во втором полупериоде тактового интервала счетного импульса считывается содержимое данной ячейки памяти ОЗУ. Так как счетчики n адресов 4, 5 непрерывно, синхронно увеличивают свое содержимое, то по всему адресному пространству ОЗУ 7 поступающие данные информационного потока записываются и тут же считываются без задержки на выход устройства. Таким образом, в этом варианте работы линии задержки, при одинаковых содержимых счетчиков адресов 4, 5 поступающие данные без задержки выдаются на выход линии задержки. В другом варианте работы линии задержки рассмотрим формирование необходимой величины задержки поступающих данных информационного потока. Для обеспечения требуемой величины задержки информационного потока в линии задержки необходимо установить двоичный код требуемой величины задержки, превышающей текущее значение кода счетчика адреса чтения 5 данных ОЗУ. Другими словами, это означает, что насколько код счетчика адреса записи 4 будет превышать значение кода счетчика адреса чтения 5, на столько же будут задерживаться данные на выходе линии задержки относительно поступающих данных. Например, если мы установили код адреса записи 4, равное десяти относительно кода чтения 5 данных ОЗУ, то мы получим величину задержки данных информационного потока равной десяти, умноженную на величину длительности дискрета линии задержки.

Таким образом, величина кода превышения содержимого счетчика адреса записи 4 над содержимым счетчика адреса чтения 5 будет определять величину задержки данных информационного потока, поступающих на линию задержки. Моменты времени изменения содержимых счетчиков адресов записи чтения данных ОЗУ должны быть синхронизированы с последовательностью тактовых импульсов, поступающих на счетные входы счетчиков адресов. При возникновении задачи регулирования скорости поступающих данных информационного потока необходимо периодически повторять или изменять величину разности кодов между счетчиками адресов записи и чтения данных ОЗУ, например, если мы имеем код разности между счетчиком адреса записей и чтения равной ста. Рассмотрим три вида режима работы линии задержки. Первый режим - режим неизменной, постоянной скорости выходных данных, но постоянно задерживаемых данных, соответствующих коду задержки ста единиц. Этот режим будет обеспечиваться однократной записью кода разности требуемой величины задержки. Второй режим - режим уменьшения скорости выходных данных относительно поступающих данных информационного потока. Такой режим снижения скорости информационного потока достигается тем, что периодически необходимо увеличивать задержку, например, увеличивать код задержки в каждом периоде цикла на десять единиц. В этом случае пока мы периодически увеличиваем величину кода задержки, например, на десять единиц, мы на такую же величину снижаем скорость поступающего информационного потока. И, наконец, третий режим - режим повышения скорости поступающего информационного потока, который достигается тем, что после однократного формирования кода задержки, например, на величину сто единиц необходимо периодически, циклически уменьшать величину задержки шагом, например, на десять единиц. В этом случае мы получим повышение скорости поступающих данных информационного потока относительно той величины скорости, которую мы имели при однократной задержке данных на сто единиц. Максимальная величина задержки устройства определяется разрядностью двоичных счетчиков адресов линии задержки, максимальная величина дискрета задержки определяется разрядностью кода коэффициента деления ДПКД. Таким образом, предельно максимальная задержка будет определяться суммой разрядностей коэффициента деления ДПКД и счетчиков адресов. Для получения минимальной величины дискрета задержки необходимо иметь как можно высокую частоту следования импульсов задающего генератора 1. Такие скоростные параметры работы линии задержки с наносекундной величиной дискрета управления могут быть обеспечены при ее монолитном интегральном исполнении.

Работа управляемой линии задержки аналоговых сигналов по блок-схеме фигуры 2 происходит следующим образом. Для работы с аналоговыми сигналами линия задержки дополнительно содержит p-разрядный аналого-цифровой преобразователь (АЦП) 10, на аналоговый вход которого через внешний вывод 8 поступают аналоговые сигналы, которые с учетом дискретизации по Котельникову преобразуются на АЦП 10 в p-разрядный параллельный код, поступающий на р входы записи данных ОЗУ 7 (p>1). Затем эти p-разрядные коды в соответствии с заданной величиной задержки через p выходы чтения данных ОЗУ 7 поступают на p входы дополнительно введенного p-разрядного цифроаналогового преобразователя (ЦАП) 11, с выхода которого задержанные аналоговые сигналы выдаются на внешний вывод 9 линии задержки. Как и прежде, основным элементом линии задержки является оперативное запоминающее устройство ОЗУ 7 только в многоразрядном виде. В остальном работа линии задержки ничем не отличается от функционирования устройства предыдущего варианта исполнения. Отличительной особенностью предлагаемой линии задержки является возможность управления величиной задержки путем изменения величины длительности временных интервалов в тракте прохождения информационного потока, не привязываясь к фронтам, спадам импульсов и их длительностям. Такой принцип управления величиной задержки информационного потока в тракте его прохождения позволяет регулировать скорость поступающих данных информационного потока. Синхронизация информационных потоков в транспортных сетях передачи данных возникает, когда данные информационного потока записываются с одной частотой поступления (с одной скоростью), а считываются данные с другой частотой (с другой скоростью). Для решения таких задач синхронизации информационных потоков может найти применение предлагаемая линия задержки. В случае реализации данной линии задержки в виде монолитной интегральной микросхемы минимальная величина дискрета управляемой задержки может быть в пределах наносекундного диапазона. Точностные параметры исполняемой величины задержки полностью зависят и определяются стабильностью работы задающего генератора импульсов.

Источники информации

1. RU 2377717 C1, H03H 7/30, H03K 5/13.

2. RU 2386208 C1, H03K 5/14.

3. «Сети синхронизации: сценарии взаимодействия» - Николай Бирюков, Наталья Триска. www.seti.com.ua

1. Управляемая линия задержки, имеющая, по меньшей мере, внешний вывод для приема поступающих данных, внешний вывод для выдачи задержанных данных, внешние выводы для приема команд управления величиной задержки, содержащая задающий генератор импульсов, выход которого соединен со счетным входом делителя с переменным коэффициентом деления (ДПКД), соответственно организованную систему элементов ячеек памяти оперативного запоминающего устройства (ОЗУ), емкостью двумерной матрицы p×2n бит, где p - количество одновременно, параллельно записываемых/считываемых данных ОЗУ по адресно управляемой выборке 2n бит с выводами записи/чтения данных ОЗУ, также имеющего n выводов для адресной выборки записи/чтения данных ОЗУ, отличающаяся тем, что линия задержки дополнительно содержит n двухвходовых мультиплексоров, n выходы которых соединены с n входами адресной выборки данных ОЗУ, n-разрядный двоичный счетчик адреса записи данных ОЗУ с n входами установки кода задаваемой величины управляемой задержки, n-разрядный двоичный счетчик адреса чтения данных ОЗУ с n входами установки кода задаваемой величины управляемой задержки, при этом первые входы n двухвходовых мультиплексоров соответственно соединены с n выходами двоичного счетчика адреса записи данных ОЗУ, а вторые входы n двухвходовых мультиплексоров соответственно соединены с n выходами двоичного счетчика адреса чтения данных ОЗУ, причем управляющие входы n двухвходовых мультиплексоров объединены между собой и соединены с выходом ДПКД, тот же выход ДПКД соединен со счетными входами двоичных счетчиков адресов записи чтения данных ОЗУ, управляющие коэффициентом деления выводы ДПКД определяют необходимую величину дискрета управления линии задержки.

2. Линия задержки по п.1, отличающаяся тем, что при использовании ОЗУ с организацией памяти p=1, она трансформируется в линию задержки цифровых данных информационного потока, при этом вход записи данных ОЗУ, соединен с внешним выводом для приема поступающих данных, а выход чтения данных ОЗУ соединен с внешним выводом для выдачи задержанных данных.

3. Линия задержки по п.1, отличающаяся тем, что при использовании ОЗУ с организацией памяти p>1, она трансформируется в линию задержки аналоговых сигналов и дополнительно содержит p-разрядный аналого-цифровой преобразователь (АЦП) также p-разрядный цифроаналоговый преобразователь (ЦАП), при этом внешний вывод для приема поступающих данных соединен с аналоговым входом АЦП, p выходы которого соответственно соединены с p входами записи данных ОЗУ, а p выходы чтения данных ОЗУ соответственно соединены с p входами ЦАП, выход которого соединен с внешним выводом для выдачи задержанных данных.