Устройство кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении достоверности принимаемой информации в каналах с высоким уровнем помех. Устройство кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями содержит накопитель информации, состоящий из ОЗУ1, ОЗУ2 и схемы управления, схему формирования наиболее вероятных векторов ошибок, блок сумматоров, схему определения границ слов и номеров, схемы определения границ блоков, схему счета последовательности номеров и схему сборки, при этом вход признаков наименее достоверных символов устройства является объединенным входом для схемы формирования наиболее вероятных векторов ошибок и накопителя, а выход признаков наименее достоверных символов накопителя также является выходом устройства. В устройство введены общие блоки пороговых элементов и сборки, при этом один из входов общего блока порогового элемента схемы определения границ слов и номеров соединен с выходами блоков счетчиков для мягких решений, а другой вход блока порогового элемента соединен с выходом схемы счетчиков в схеме жесткого определения границ блоков, выход общего блока порогового элемента соединен с одним из входов сборки, а другой вход сборки соединен с выходом порогового элемента в схеме жесткого определения границ блоков, а выходы сборок соединены с входами схемы сборки, выход которой является выходом устройства для формирования сигналов об окончании каждого блока информации. 1 ил.

Реферат

Изобретение относится к системам передачи дискретной информации и может быть использовано для цикловой синхронизации в системах помехоустойчивой защиты информации, в которых применяются корректирующие, в частности каскадные, коды.

В устройствах кодовой цикловой синхронизации синхронизирующие признаки передаются словами помехоустойчивого кода. Для синхронизации используется избыточность кода, поэтому передачи дополнительных синхронизирующих символов не требуется. После приема последовательной информации признаки синхронизации снимаются с помехоустойчивого кода, не уменьшая при этом корректирующей способности кода.

Использование кодовой цикловой синхронизации наиболее эффективно в каскадных кодах. В этом случае синхронизация обеспечивается за счет многократного повторения признаков синхронизации в различных словах внутреннего кода каскадного кода.

При разработке устройств кодовой цикловой синхронизации актуальной задачей является повышение вероятности установления синхронизации, а значит, повышение достоверности принимаемой информации в каналах связи с высоким уровнем помех. Однако известные устройства кодовой цикловой синхронизации не обеспечивают необходимой достоверности принимаемой информации.

Известно устройство цикловой синхронизации, содержащее накопитель информации, выполненный на регистре задержки, и узел обнаружения ошибок, входы накопителя информации и узла обнаружения ошибок объединены и соединены с информационным входом устройства, при этом узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из последовательно соединенных регистра и сумматора по модулю два, выход второго фильтра Хаффмена соединен с входом регистра синдрома, выход которого соединен с входом блока дешифраторов [авторское свидетельство СССР №849521, МПК H04L 7/08, опубл. 1981].

Устройство обладает недостаточной достоверностью принимаемой информации в каналах связи с помехами из-за того, что синхронизация устанавливается только по безошибочным словам помехоустойчивого кода, а в каналах с ошибками безошибочные слова могут отсутствовать.

Следующим аналогом к предлагаемому устройству является устройство кодовой цикловой синхронизации, содержащее накопитель, состоящий из оперативного запоминающего устройства (ОЗУ1), ОЗУ2 и схемы управления, входы которых объединены и соединены с информационным входом устройства, узел обнаружения ошибок, выполненный из двух последовательно соединенных первого фильтра и второго фильтра Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из регистра и сумматора по модулю два, выход сумматора второго фильтра Хаффмена соединен с входом регистра синдрома, блок дешифраторов, блок сумматоров по модулю два, блок регистров, полный сумматор номеров, схему сравнения номеров, схему счета последовательности номеров, состоящую из схемы отбора, коммутатора счета, схемы регистров счета, полного сумматора и схемы определения последовательности заданной длины, дешифратор подтвержденных слов, коммутатор номеров, распределитель, блок счетчиков, пороговый блок [патент РФ №2383104, МПК H04L 7/08, опубл. 27.02.2010].

Недостатком этого устройства является недостаточная достоверность принимаемой информации в каналах связи с помехами, так как применяются только жесткие решения и отсутствуют функциональные узлы, позволяющие выполнять цикловую синхронизацию с применением мягких решений в словах помехоустойчивого кода.

Также известно устройство кодовой цикловой синхронизации с мягкими решениями, содержащее накопитель информации, состоящий из ОЗУ1, ОЗУ2 и схемы управления, вход которого является информационным входом устройства, а его выход - информационным выходом устройства, схему формирования наиболее вероятных векторов ошибок, блок сумматоров, схемы определения границ блоков и схему сборки, при этом вход признаков наименее достоверных символов схемы формирования наиболее вероятных векторов ошибок является входом устройства и соединен с входом накопителя, а выход признаков наименее достоверных символов накопителя является выходом устройства, выходы схемы формирования наиболее вероятных векторов ошибок соединены с входами блока сумматоров, другой вход блока сумматоров соединен с информационным входом устройства, выходы блока сумматоров соединены с входами схем определения границ блоков, каждая из которых содержит схемы определения границ слов и их номеров, схему фильтрации номеров, распределитель, блок счетчиков и пороговый элемент, каждая схема определения границ слов и их номеров содержит узел обнаружения ошибок, блок дешифраторов и блок сумматоров по модулю два, при этом каждый узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из последовательно соединенных регистра и сумматора по модулю два, выход сумматора второго фильтра Хаффмена соединен с входом регистра синдрома, выход регистра синдрома является выходом узла обнаружения ошибок и соединен с входом блока дешифраторов, один выход которого соединен с одним из входов распределителя, а другой выход блока дешифраторов соединен с входом сумматора по модулю два, другой вход которого соединен с выходом второго фильтра Хаффмена, выход блока сумматоров, являясь выходом схемы определения границ слов и номеров, соединен с одним из входов схемы фильтрации номеров, выходы которой соединены с входами блока счетчиков, другие входы блоков счетчиков соединены с выходами распределителей, входы распределителя соединены с выходами блоков дешифраторов, выход блока счетчиков соединен с входом порогового элемента, выходы пороговых элементов являются выходами схем определения границ блоков и соединены с входами сборки, выход которой является выходом устройства для формирования сигналов об окончании каждого блока информации [Ромачева И.А., Третьяков А.В., Трушин С.А. Устройство цикловой синхронизации с мягкими решениями. Труды IX Российской научно-технической конференции «Новые информационные технологии в системах связи и управления». Калуга. 2010. С.328-338].

Недостатком этого устройства является недостаточная достоверность принимаемой информации в каналах связи с помехами, так как применяются только мягкие решения и отсутствуют функциональные узлы, позволяющие выполнять цикловую синхронизацию с применением жестких решений в словах помехоустойчивого кода за пределами корректирующей способности кода.

Наиболее близким аналогом предлагаемого устройства кодовой цикловой синхронизации (прототип) является устройство кодовой цикловой синхронизации, состоящее из двух рассмотренных выше устройств кодовой цикловой синхронизации и содержащее функциональные узлы, позволяющие выполнять цикловую синхронизацию с применением мягких и жестких решений в словах помехоустойчивого кода [Ромачева И.А., Трушин С.А. Устройство декодирования с мягкими решениями для двухступенчатого каскадного кода. Труды IX Российской научно-технической конференции. «Новые информационные технологии в системах связи и управления». Калуга. 2010. С.353-369].

Недостатком этого устройства является недостаточная достоверность принимаемой информации в каналах связи с помехами, так как в нем для синхронизации независимо применяют только мягкие или только жесткие схемотехнические решения и отсутствует их взаимная интеграция в единое целое.

Цель изобретения - повышение достоверности принимаемой информации устройством кодовой цикловой синхронизации за счет увеличения вероятности установления синхронизации и, как следствие, обеспечение возможности наиболее эффективной работы его в каналах с высоким уровнем помех.

Для достижения цели предложено устройство кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями, содержащее накопитель информации, состоящий из ОЗУ1, ОЗУ2 и схемы управления, вход которого является информационным входом устройства, схему формирования наиболее вероятных векторов ошибок, блок сумматоров, схему определения границ слов и номеров, схемы определения границ блоков, схему счета последовательности номеров и схему сборки, при этом вход признаков наименее достоверных символов устройства является объединенным входом для схемы формирования наиболее вероятных векторов ошибок и накопителя, а выход признаков наименее достоверных символов накопителя также является выходом устройства, выходы схемы формирования наиболее вероятных векторов ошибок соединены с входами блока сумматоров, другой вход блока сумматоров соединен с информационным входом устройства, который объединен с входом общей схемы определения границ слов и номеров, выходы блока сумматоров соединены с входами схем определения границ блоков, каждая из которых содержит схемы определения границ слов и номеров, схему фильтрации номеров, распределители, блоки счетчиков, блок порогового элемента и схему жесткого определения границ блоков, каждая схема определения границ слов и номеров содержит узел обнаружения ошибок, блок дешифраторов и блок сумматоров по модулю два, при этом каждый узел обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффмена и регистра синдрома, причем каждый фильтр Хаффмена состоит из последовательно соединенных регистра и сумматора по модулю два, выход сумматора второго фильтра Хаффмена соединен с входом регистра синдрома, выход регистра синдрома является выходом узла обнаружения ошибок и соединен с входом блока дешифраторов, один выход которого соединен с одним из входов распределителей, а другой выход блока дешифраторов соединен с входом сумматора по модулю два, другой вход которого соединен с выходом второго фильтра Хаффмена, выход блока сумматоров, является выходом схемы определения границ слов и номеров, выход общей схемы определения границ слов и номеров соединен с одним из входов блоков счетчиков, с входом схем фильтрации номеров, с входом схем жесткого определения границ блоков и с входом схемы счета последовательности номеров, выходы схем определения границ слов и номеров, содержащихся в схемах определения границ блоков, соединены с одним из входов счетчиков и с входом схемы фильтрации номеров, другие входы блока счетчиков соединены с выходами распределителей, а одни из входов распределителей соединены с выходами блоков дешифраторов, выходы блоков счетчиков соединены с входами блоков пороговых элементов, при этом схема счета последовательности номеров содержит блок регистров, сумматор номеров, схему сравнения номеров, схему отбора, коммутатор счета, схему регистров счета, полный сумматор и схему определения последовательности, входы блока регистров и схемы сравнения объединены и являются входом схемы счета последовательности номеров, выход блока регистров соединен с входом сумматора номеров, на другой вход сумматора номеров поступает уровень лог.1, выход сумматора номеров соединен с входом схемы сравнения номеров, выход которой соединен с входом схемы отбора, а другой вход схемы отбора и вход коммутатора счета соединен с выходом полного сумматора, выход схемы отбора соединен с входом коммутатор счета, выход коммутатор счета соединен с входом схемы регистров счета, выход которой соединен с одним из входов полного сумматора, а другой вход полного сумматора соединен с уровнем лог.1, выход полного сумматора соединен с входом схемы определения последовательности, выход которой является выходом схемы счета последовательности номеров и соединен с одним из входов схемы определения границ блоков, которые объединены и подключены к одним из входов коммутаторов и схем распределителей, содержащихся в схемах жесткого определения границ блоков, при этом каждая схема жесткого определения границ блоков содержит коммутатор, фильтр, схему распределителя, схему счетчиков, пороговый элемент, а выход коммутатора соединен с входом фильтра и одним из входов схемы счетчиков, выход фильтра соединен с одним из входов схемы распределителя, выход которого соединен с входом схемы счетчиков, а выход схемы счетчиков соединен с входом порогового элемента, при этом выходы накопителя являются выходом признаков наименее достоверных символов и информационным выходом устройства. Новым является то, что в устройство введены общие блоки порогового элемента для мягких и жестких решений и сборки, при этом один из входов общего блока порогового элемента схемы определения границ слов и номеров соединен с выходами блоков счетчиков для мягких решений, а другой вход общего блока порогового элемента соединен с выходом схемы счетчиков в схеме жесткого определения границ блоков, выход общего блока порогового элемента соединен с одним из входов сборки, а другой вход сборки соединен с выходом порогового элемента в схеме жесткого определения границ блоков, а выходы сборок соединены с входами схемы сборки, выход которой является выходом устройства для формирования сигналов об окончании каждого блока информации.

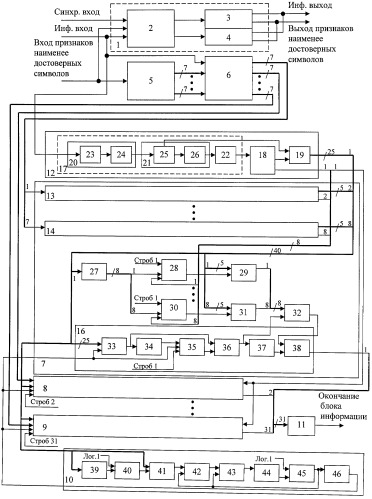

В предлагаемом устройстве мягкие и жесткие решения интегрированы введением их общих пороговых элементов. На чертеже приведена структурная схема предлагаемого устройства.

Устройство кодовой цикловой синхронизации с интегрированными мягкими и жесткими решениями содержит накопитель информации 1, состоящий из схемы управления 2, ОЗУ1 3, и ОЗУ2 4, схему формирования наиболее вероятных векторов ошибок 5, блок сумматоров 6, схемы определения границ блоков 7, 8, 9, схему счета последовательности номеров 10, схему сборки 11, общую схему определения границ слов и номеров 12, каждая из схем определения границ блоков состоит из схем определения границ слов и номеров 13, 14, схемы фильтрации номеров 27, распределителей 28, 30, блоков счетчиков 29, 31, блока порогового элемента 32 и схемы жесткого определения границ блоков 16, которая содержит коммутатор 33, фильтр 34, схему распределителя 35, схему счетчиков 36, пороговый элемент 37 и сборку 38, причем каждая из схем определения границ слов и номеров содержит узел обнаружения ошибок 17, блок дешифраторов 18 и блок сумматоров по модулю два 19, при этом каждый узел обнаружения ошибок 17 выполнен из двух последовательно соединенных первого фильтра Хаффмена 20 и второго фильтра Хаффмена 21 и регистра синдрома 22, причем первый фильтр Хаффмена 20 состоит из регистра 23 и сумматора по модулю два 24, а второй фильтр Хаффмена 21 состоит из регистра 25 и сумматора по модулю два 26, при этом схема счета последовательности номеров 10 содержит блок регистров 39, сумматор номеров 40, схему сравнения номеров 41, схему отбора 42, коммутатор счета 43, схему регистров счета 44, полный сумматор 45, схему определения последовательности 46.

Устройство работает следующим образом.

На передающей стороне в качестве выходной информации формируется последовательность c1⊕c2i⊕c3n, представляющая собой поразрядную сумму по модулю два трех последовательностей: последовательности внутренних двоичных кодов каскадного кода c1, синхронизирующей двоичной последовательности c2i=c21c22c23 … c2n и последовательности c3n=c3c3c3 … c3, нарушающей циклические свойства исходного кода и состоящей из повторяющихся циклических последовательностей, где n - число слов кода Боуза-Чоудхури-Хоквингема (БЧХ), c2i - синхронизирующая последовательность для i-го слова БЧХ.

Для получения последовательности c1 на передающей стороне исходная информация объемом k m-ичных (m>1) символов кодируется m-ичным помехоустойчивым кодом, например, m-ичным помехоустойчивым кодом Рида-Соломона (PC). Код PC является внешним кодом или кодом первой ступени помехоустойчивого каскадного кода.

В результате такого кодирования исходной информации получают блок из слов кода PC (n,k), информационная длина которого k равна слову PC, a блоковая - n символов.

Далее блок информации, состоящий из слов PC, кодируется двоичным кодом, например двоичным кодом БЧХ с проверочным многочленом h1(x). Код БЧХ является внутренним кодом или кодом второй ступени помехоустойчивого каскадного кода. Слово кода БЧХ имеет следующие параметры: n1 - блоковая длина кода, k1 - информационная длина кода. В результате кодирования блока из слов PC кодом БЧХ получают блок из n двоичных слов кода БЧХ (n1,k1), представляющих собой последовательность c1.

Далее слова кода БЧХ суммируются по модулю два с синхронизирующей последовательностью c2i. В качестве синхронизирующей последовательности выбирают двоичный код с блоковой длиной n1 и информационной длиной k2, например код Рида-Маллера (РМ) первого порядка (последовательность максимального периода) с проверочным многочленом h2(x). Информационная длина k2 кода РМ соответствует двоичной записи номеров слов БЧХ. Между номерами слов БЧХ в каскадном коде и информационной частью синхронизирующей последовательности устанавливается взаимно однозначное соответствие. Первое слово БЧХ суммируется по модулю два с последовательностью, полученной в результате кодирования двоичной записи первого номера слова БЧХ кодом РМ, второе слово БЧХ суммируется по модулю два с последовательностью, полученной в результате кодирования двоичной записи второго номера слова БЧХ кодом РМ и так далее. Такая операция суммирования выполняется со всеми словами кода БЧХ. Если проверочные многочлены h1(x) и h2(x) суммируемых кодов БЧХ и РМ взаимно просты и являются делителями двучлена xn1+1, в результате суммирования будет получено n слов циклического кода БЧХ с длиной n1 и информационной длиной k1+k2. Этот код будет корректировать ошибки, число которых

e≤r/log2(n1+1),

где r=n1-k1-k2 - число проверочных символов кода.

Третья последовательность c3, с которой суммируются слова БЧХ, будет постоянной последовательностью длиной n1 бит для всех слов. Такой последовательностью может быть любая последовательность, не являющаяся кодовым словом кода БЧХ, например последовательность 10000…000.

В реальных каналах возможны помехи, которые можно рассматривать как последовательность с4, наличие единиц в которой соответствует размещению ошибок в словах. Для безошибочных слов последовательность с4 содержит только нули.

Информация в виде последовательности c1⊕c2i⊕c3n⊕c4, сформированной из четырех последовательностей, поступает на информационный вход устройства кодовой цикловой синхронизации. Эта последовательность записывается в накопитель информации 1 и одновременно поступает на один из входов блока сумматоров 6. Блок сумматоров 6 состоит из параллельных двухвходовых сумматоров по модулю два, один из входов каждого двухвходового сумматора по модулю два соединен с информационным входом устройства, а на другой вход двухвходовых сумматоров по модулю два поступает соответствующий вектор ошибок с выходов схемы формирования наиболее вероятных векторов ошибок 5. Выходы двухвходовых сумматоров по модулю два являются выходами блока сумматоров 6, на которых формируются кодовые слова с мягкими решениями. Схема формирования наиболее вероятных ошибок 5 содержит распределитель на длину слова БЧХ на основе счетчика Джонсона. Пример реализации варианта распределителя на основе счетчика Джонсона приведен в источнике [В.Л.Шило. Популярные цифровые микросхемы. Справочник. Москва. Металлургия, 1988, стр.240, рис.2.40]. Таким образом, интервал между импульсами на одном из выходов распределителя на основе счетчика Джонсона соответствует границам слов БЧХ. На вход схемы формирования наиболее вероятных векторов ошибок 5, являющийся одним их входов устройства, поступает сигнал в виде логической «1» на позициях наиболее недостоверных символов, а на остальных позициях - в виде логического «0».

Вектор ошибок формируется в соответствии с известным алгоритмом Чейза, метод 2 [Кларк Дж., мл., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи. М.: Радио и связь, 1987 г., стр.161]. В данном алгоритме всевозможные комбинации векторов формируются на [d/2] позициях наименее достоверных символов, где d - минимальное кодовое расстояние. Для кодового слова БЧХ (31, 16) значение [d/2] равно трем. Если слово БЧХ содержит более трех наименее достоверных символов, то для данного устройства векторы ошибок формируются только для первых трех позиций, а значения остальных символов остаются исходными. Для формирования векторов ошибок надо знать позиции наименее достоверных символов в слове БЧХ, для чего устройство должно определять границы слов БЧХ. Возможные границы слов БЧХ определяются импульсами на выходах распределителя на основе счетчика Джонсона схемы формирования наиболее вероятных векторов ошибок 5. В рамках границ слов БЧХ на позициях наименее достоверных символов можно сформировать соответствующие варианты векторов ошибок, например, схемой, состоящей из четырех D-триггеров сдвигового регистра и комбинаторной логики. При поступлении наименее достоверного символа в первый D-триггер записывается логическая «1», которая затем продвигается на выход этого регистра с приходом каждого нового наименее достоверного символа. Таким образом, положение и количество наименее достоверных символов в слове фиксируется состоянием регистра, значение которого можно использовать для разрешения или запрета логической «1» в сигнале наиболее недостоверных символов, поступившем в устройство, и, соответственно, формировать векторы ошибок. Импульс, определяющий границу слова БЧХ, и сигнал начальной установки сбрасывают D-триггеры сдвигового регистра в исходное нулевое состояние. Варианты векторов ошибок с выходов схемы формирования наиболее вероятных векторов ошибок 5 поступают на входы блока сумматоров 6, где складываются по модулю два с принимаемой информацией, и с выходов блока сумматоров 6 приходят на входы схемы определения границы блока 7.

В накопителе информации 1 последовательность и признаки наименее достоверных символов записываются в одно из двух ОЗУ, пока схемой сборки 11 не будет определен конец блока слов БЧХ, после чего схема управления накопителя начнет запись в другое ОЗУ последующей информации, а из предыдущего ОЗУ начнет считывание информации для дальнейших операций ее обработки и декодирования. Использование накопителя информации 1, содержащего два ОЗУ, позволяет применить конвейерный способ обработки информации, обеспечив одновременную запись и считывание информации из накопителя информации 1, что повышает быстродействие устройства.

В фильтрах Хаффмена 20, 21 последовательность умножается на проверочные многочлены кодов БЧХ и РМ h1(x) и h2(x). Таким образом, в первом фильтре Хаффмена 20 вычисляется синдром слова кода БЧХ последовательности c1, а во втором фильтре Хаффмена 21 - синдром кода РМ последовательности c2i.

Для безошибочного слова синдром кода равен нулю, и в регистре синдрома 22 будет записана комбинация d0, соответствующая преобразованной в фильтрах Хаффмена 20 и 21 последовательности c3.

Для слов с ошибками, исправление которых возможно в пределах корректирующей способности кода, в регистре синдрома 22 будет записана комбинация из некоторого множества {di}, соответствующая преобразованной в фильтрах Хаффмена 20 и 21 последовательности c3⊕c4 и однозначно определяющая комбинацию ошибок. Жесткое декодирование принятой последовательности позволяет исправлять не более (d-1)/2 ошибок. Однако если в принятом слове БЧХ содержится не более (d-1) ошибок и при мягких решениях с помощью [d/2] вариантов векторов ошибок удалось исправить [d/2] ошибок, то остальные ошибки исправит жесткий декодер, а в результате может исправиться (d-1) ошибка, что превышает в два раза число ошибок, которое исправляет жесткий декодер. Таким образом, предлагаемое устройство может осуществлять синхронизацию и по словам кода БЧХ, содержащим ошибки за пределами корректирующей способности последовательности.

Блок дешифраторов 18 при обнаружении в регистре синдрома 22 комбинации d0 или комбинации из множества {di} выдает на вход блока сумматоров по модулю два 19 соответствующие комбинации для исправления ошибок.

В этот момент в регистре 25 второго фильтра Хаффмена 21 находится двоичная комбинация номеров, однозначно соответствующая последовательности c2i, поскольку последовательность c1 снимается первым фильтром Хаффмена 20, а последовательность c3 является постоянной.

Эта двоичная комбинация номеров с выхода регистра 25 подается на другой вход блока сумматоров по модулю два 19. В блоке сумматоров по модулю два 19 осуществляется коррекция разрядов рассматриваемой комбинации номеров так, чтобы на его выходе была двоичная комбинация, соответствующая предполагаемому истинному номеру слова кода БЧХ. Комбинации синдрома, которые распознаются блоком дешифраторов 20, получают путем вычисления синдрома для каждой из возможных комбинаций ошибок. Пример построения блока дешифраторов 20 представлен в источнике [Кларк Дж., мл., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи: пер. с англ. - М.: Радио и связь, 1987, с.96-101].

Для слов кода БЧХ (31, 21) вычисляются синдромы для однозначной коррекции их номеров до двух ошибок в слове. Откорректированные номера слова кода БЧХ с выхода блока сумматоров по модулю два 19 поступают на вход схемы фильтрации номеров 27. На вход схемы фильтрации могут поступить одновременно восемь номеров, которые надо сравнить между собой, и для несовпадающих номеров их значения подаются на соответствующие входы блока счетчиков 29, 31. Если все восемь вариантов номеров различные, то они соответственно записываются на восемь входов блока счетчиков. Схема фильтрации номеров сравнивает первый номер с остальными и для совпадающих номеров блокируется их запись в блок счетчиков, а в блок счетчиков поступает только первый номер. Одновременно второй номер сравнивается с остальными номерами, и совпадающие номера с вторым номером также блокируются для прохождения в блок счетчиков, и если второй номер не совпадает с первым номером, то второй номер также проходит на вход блока счетчиков. Одновременно аналогично сравниваются по порядку последующие номера, и только различные из них поступают в блок счетчиков. Вариант схемы фильтрации номеров приведен в источнике [Ромачева И.А., Третьяков А.В., Трушин С.А. Устройство цикловой синхронизации с мягкими решениями. Труды IX Российской научно-технической конференции «Новые информационные технологии в системах связи и управления». Калуга. 2010. С.334-335].

Синхроимпульс с выхода блока дешифраторов 18 поступает на вход распределителя 28. С целью сокращения записи номеров трансформированных слов каждый синхроимпульс получает соответствующий разрешающий строб 1 - строб 31, фиксирующий границу слова, с выходов схемы формирования наиболее вероятных векторов ошибок 5, соединения которых на рисунке полностью не показаны. Для максимального числа комбинаций многовариантного номера, который возможен при мягких решениях, каждый распределитель 28, 31 должен содержать соответствующее количество подраспределителей.

Схема каждого подраспределителя может быть построена, например, на основе D-триггера. В исходном состоянии все Q-выходы последовательно соединенных D-триггеров подраспределителя находятся в состоянии логического «0». При поступлении тактового сигнала подраспределителя на Q-выходе первого D-триггера формируется уровень логической «1», который через двухвходовую схему ИЛИ поступает на D-вход второго D-триггера и вход двухвходовой схемы И, второй вход которой соединен с выходом следующей схемы ИЛИ, один вход которой соединен с Q-выходом второго D-триггера. На вторые входы каждой схемы ИЛИ могут поступать сигналы логической «1», запрещающие запись новых значений номеров в соответствующие синхронизированные счетчики блока счетчиков 29, 31 и их перезапуск. Выход схемы И соединен с D-входом следующего D-триггера и входом следующей двухвходовой схемы И. После двухвходовых схем ИЛИ первого и последнего D-триггеров схемы подраспределителя двухвходовые схемы И отсутствуют.

С каждым тактовым сигналом подраспределителя происходит продвижение уровня логической «1» к Q-выходу последнего D-триггера. Когда все Q-выходы D-триггеров установятся в состояние логической «1», происходит общий сброс всех Q-выходов D-триггеров в состояние логического «0».

Второй вход каждой двухвходовой схемы ИЛИ предназначен для подачи на него уровня логической «1» для запрета формирования на выходе схемы ИЛИ перепада сигнала из логического «0» в логическую «1», разрешающего запись номеров в соответствующие счетчики в блоке счетчиков 29, 31 и запуск этих счетчиков. Схема аналогичного подраспределителя приведена в источнике [Системы и средства связи, телевидения и радиовещания, 2008, выпуск 1, 2, с.158, рис.3].

Выход распределителя 28 соединен с входом блока счетчиков 29, другие входы которого соединены с выходом схемы фильтрации номеров 27. Блок счетчиков 29 состоит из набора последовательно соединенных счетчиков двух типов. Коэффициент счета первого счетчика соответствует длине слова кода БЧХ, а второй счетчик считает количество этих слов до конца блока. Коэффициент счета этих двух счетчиков соответствует длине блока слов кода БЧХ. На тактовый вход блока счетчиков, не показанный на схеме, подается частота, соответствующая скорости приема информации из канала.

Блок счетчиков 29 работает следующим образом. По сигналу с выхода распределителя 28 с выхода схемы фильтрации номеров 27 во второй счетчик блока счетчиков 29 происходит запись номера этого слова кода БЧХ и одновременный запуск его первого счетчика. Когда первый счетчик досчитывает до конца, что соответствует длине слова кода БЧХ, формируется тактовый сигнал для второго счетчика и его значение увеличивается на единицу. Момент, когда второй счетчик досчитывает до конца, должен соответствовать нахождению конца блока слов кода БЧХ. Однако существует вероятность приема ложных слов кода БЧХ, то есть трансформированных слов, особенно в каналах с высоким уровнем помех. При запуске счетчиков трансформированным словом конец счета не будет соответствовать истинному концу блока слов кода БЧХ. Поэтому количество счетчиков в блоке счетчиков 29 должно рассчитываться с учетом возможного приема трансформированных слов. Учитывая, что вероятность трансформированных слов на несколько порядков меньше вероятности истинных слов и используется 31 вариант синхронизации для каждого слова в предлагаемом устройстве, то минимальное число счетчиков в каждом блоке счетчиков 8L, где L - пороговое значение числа слов для синхронизации блока.

Для уменьшения вероятности перезапуска счетчиков трансформированными словами при сохранении достоверности приема в предлагаемом устройстве, например, в блоке счетчиков 29 предусмотрено сравнение всех номеров счетчиков в каждом подраспределителе, а также их сравнение с номерами счетчиков всех остальных подраспределителей блока счетчиков 29. Во время синхронизации производится последовательная запись номеров в счетчики до конца длины подраспределителей, а затем для последующих записей номеров производится проверка синхронной работы счетчиков. Запись новых номеров ведется только в несинхронизированные счетчики, а в счетчики, у которых есть синхронизация между собой, запись новых номеров запрещена либо до конца их счета, либо до общего сброса всех счетчиков по концу блока или по сигналу начальной установки. В блоке счетчиков 29 на его выходах формируются сигналы об окончании блока слов кода БЧХ, которые поступают на вход блока порогового элемента 32.

На выходе блока порогового элемента 32 формируется истинный сигнал об окончании блока слов кода БЧХ. Характеристики мажоритарной схемы блока порогового элемента 32 выбираются таким образом, чтобы обеспечить высокую вероятность правильной цикловой синхронизации для конкретного канала. Например, для каскадного кода, внешним кодом которого является код PC (32, 16), а внутренним - код БЧХ (31, 16), число номеров равно тридцати двум, объем регистра синдрома, равный разности проверочных битов и битов в номере, соответствует десяти битам, что позволяет жестко исправлять до двух ошибок в каждом слове БЧХ (31, 21). Максимальное количество вариантов номеров для одного слова БЧХ при мягких решениях для предлагаемого устройства равно восьми, поэтому каждый распределитель содержит также восемь подраспределителей.

Для блока порогового элемента 32 предлагаемого устройства целесообразно выбрать мажоритарный элемент, который формирует сигнал об окончании блока информации при условии синхронизации шести и более счетчиков из сорока восьми, поэтому такой распределитель 28 может запустить даже при наличии трансформированных слов не более сорока восьми счетчиков.

Благодаря фильтрации номеров, стробированию запускающего импульса распределителя сигналом окончания слова, запрету записи новых номеров в синхронизированные счетчики в предлагаемом устройстве минимизируется число необходимых счетчиков в блоках счетчиков типа 29, что приводит к упрощению схемотехнического решения устройства.

При реализации декодирующего устройства важно обеспечить, чтобы вероятность правильной синхронизации устройства цикловой синхронизации была не менее вероятности правильного декодирования кода, а лучше превышала ее и была максимально близка к единице.

Схема жесткого определения границ блоков 16 работает следующим образом. По сигналу с выхода схемы определения последовательности 46 коммутатор 33 подключает соответствующие комбинации вариантов номера слова кода БЧХ с выхода блока сумматоров по модулю два 19. Коммутатор 33 может подключать одно или несколько значений номеров, соответствующих коротким последовательностям. Далее фильтр 34 на своем выходе формирует сигналы разрешения только для разных номеров. Для одинаковых номеров фильтр 34 на своем выходе формирует один сигнал разрешения. Распределитель 35 записывает номера и запускает схему счетчиков 36 при совпадении трех сигналов с выходов схем 10, 5 и 34. Для максимального числа комбинаций многовариантного номера распределитель 35 должен содержать соответствующее число подраспределителей. Построение схем подраспределителей распределителей 35 и 28 идентично. Выходы схемы счетчиков 36 соединены с входами блока порогового элемента 32 и схемы порогового элемента 37. На выходе блока порогового элемента 32 формируется сигнал об окончании блока для мягких и интегрированных мягких и жестких решений. На выходе схемы порогового элемента 37 формируется сигнал об окончании блока только для жестких решений. Сигналы с выходов блока порогового элемента 32 и схемы порогового элемента 37 поступают на входы сборки 38, выход которой является выходом схемы определения границ блоков 7. Сигналы с выходов схем определения границ блоков 7, 8, 9 поступают на входы сборки 11, на выходе которой формируется сигнал об окончании блока только для жестких решений, только для мягких решений и интегрированных мягких и жестких решений.

Схема счета последовательности номеров 10 предназначена только для жестких решений и работает следующим образом. Откорректированные номера слова кода БЧХ с выхода блока сумматоров по модулю два 19 поступают на вход блока регистров 39 и одновременно на вход схемы сравнения номеров 41 и на вход коммутатора номеров 33.

Блок регистров 39 выполнен в виде параллельных регистров сдвига, в каждый из которых записывается номер слова кода БЧХ с выхода блока сумматоров по модулю два 19. Число параллельных регистров равно числу вариантов корректирующих комбинаций для каждого номера слова БЧХ, синдром которого соответствует множеству {ri}. Для слов БЧХ, синдромы которых соответствуют комбинации d0 или множеству {di}, в каждый из параллельных регистров записывается одинаковое значение номеров.

Длина каждого из регистров сдвига блока регистров 39 равна длине слова кода БЧХ. На тактовый вход блока регистров 39, не показанный