Смеситель сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в структуре радиоприемных устройств ВЧ- и СВЧ-диапазонов. Технический результат заключается в уменьшении напряжения питания в сравнении с прототипом не менее чем на 1 В при использовании однофазного сигнала по каналу. Смеситель сигналов содержит перемножающую ячейку Гильберта, первый и второй выходные транзисторы канала «Y», первый и второй разделительные конденсаторы, с первого по третий токостабилизирующие двухполюсники, цепь нагрузки, первый и второй дополнительные транзисторы. 8 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может использоваться в структуре радиоприемных устройств ВЧ- и СВЧ-диапазонов.

В современных системах телекоммуникаций в качестве смесителей двух сигналов (СС) находят применение различные модификации перемножающей ячейки Джильберта [1-24] (термин «ячейка Джильберта» широко используется в микроэлектронике, см., например, патент №7054609 и обозначает «перемножающую» архитектуру на основе двух дифференциальных каскадов с перекрестным включением коллекторов входных транзисторов).

Особое место в рассматриваемом классе смесителей занимают схемы СС, у которых один из перемножающих сигналов подается в эмиттерные цепи транзисторов, образующих входной преобразователь «напряжение-ток» канала «Y» [25-31]. Эти СС характеризуются высокими диапазонами рабочих частот, так как у них используются усилители с общей базой.

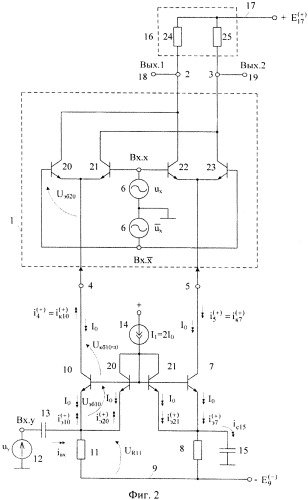

Ближайшим прототипом заявляемого устройства является аналоговый смеситель сигналов фиг.1, представленный в патенте фирмы Philips US 5825231 (данная архитектура присутствует также в патентах US 7514981, fig.6, EP 2235559 fig.3, US 4331929 fig.2 и др.). Он содержит перемножающую ячейку Гильберта (1) с первым 2 и вторым 3 противофазными токовыми выходами и первым 4 и вторым 5 противофазными токовыми входами, источник сигнала 6 канала «X» 6, связанный с базами транзисторов перемножающей ячейки Гильберт 1, первый 7 выходной транзистор канала «Y», коллектор которого соединен со вторым 5 токовым входом перемножающей ячейки Гильберга, а эмиттер через первый 8 токостабилизирующий двухполюсник связан с первой 9 шиной источника питания, второй 10 выходной транзистор канала «Y», эмиттер которого через второй 11 токостабилизирующнй двухполюсник связан с первой 9 шиной источника питания, источник сигнала канала «Y» 12, связанный с эмиттером второго 10 выходного транзистора канала «Y» через первый 13 разделительный конденсатор, третий 14 токостабилизирующий двухполюсник, связанный с базой второго 10 выходного транзистора капала «Y», второй 15 разделительный конденсатор, цепь нагрузки 16, включенную между второй 17 шиной источника питания и первым 2 и вторым 3 противофазными токовыми выходами перемножающей ячейки Гильберта, которые связаны с первым 18 и вторым 19 потенциальными выходами устройства, третью общую шину источника питания.

Существенный недостаток известного смесителя состоит в том, что он имеет повышенные значения напряжения отрицательного источника питания 9 , что не позволяет применять такую архитектуру в низковольтных IP-модулях и СФ-блоках с

Основная задача предлагаемого изобретения состоит в уменьшении напряжения питания в сравнении с прототипом не менее чем на 1 В при использовании однофазного сигнала по каналу «Y».

Поставленная задача решается тем, что в аналоговом смесителе двух сигналов, содержащем перемножающую ячейку Гильберта (1) с первым 2 и вторым 3 противофазными токовыми выходами и первым 4 и вторым 5 противофазными токовыми входами, источник сигнала 6 канала «X», связанный с базами транзисторов перемножающей ячейки Гильберта 1, первый 7 выходной транзистор канала «Y», коллектор которого соединен со вторым 5 токовым входом перемножающей ячейки Гильберта, а эмиттер через первый 8 токостабилизирующий двухполюсник связан с первой 9 шиной источника питания, второй 10 выходной транзистор канала «Y», эмиттер которого через второй 11 токостабилизирующий двухполюсник связан с первой 9 шиной источника питания, источник сигнала канала «Y» 12, связанный с эмиттером второго 10 выходного транзистора канала «Y» через первый 13 разделительный конденсатор, третий 14 токостабилизирующий двухполюсник, связанный с базой второго 10 выходного транзистора канала «Y», второй 15 разделительный конденсатор, цепь нагрузки 16, включенную между второй 17 шиной источника питания и первым 2 и вторым 3 противофазными токовыми выходами перемножающей ячейки Гильберт, которые связаны с первым 18 и вторым 19 потенциальными выходами устройства, третью общую шину источника питания, предусмотрены новые элементы и связи - коллектор второго 10 выходного транзистора канала «Y» соединен с первым 4 токовым входом перемножающей ячейки Гильберта, база второго 10 выходного транзистора канала «Y» соединена с базой первого 7 выходного транзистора канала «Y», а также базами первого 20 и второго 21 дополнительных транзисторов, которые соединены с коллекторами данных 20, 21 дополнительных транзисторов, причем эмиттер первого 20 дополнительного транзистора соединен с эмиттером второго 10 выходного транзистора канала «Y», эмиттер второго 21 дополнительного транзистора соединен с эмиттером первого 7 выходного транзистора капала «Y», а второй 15 разделительный конденсатор включен по переменному току между эмиттером второго 7 выходного транзистора канала «Y» и третьей общей шиной источника питания.

На фиг.1 представлена схема СС-прототипа, который содержит конкретное выполнение входной перемножающей ячейки Джильберта 1.

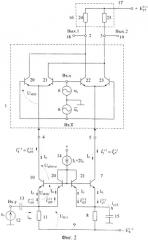

На фиг.2 представлена схема заявляемого СС в соответствии с формулой изобретения.

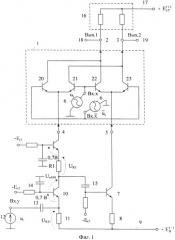

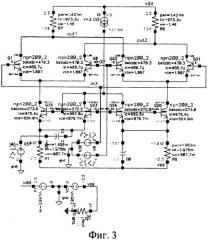

На фиг.3 представлена схема предлагаемого смесителя фиг.2 в среде Cadence на моделях SiGe интегральных транзисторов.

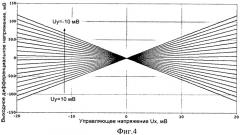

На фиг.4 приведена зависимость выходного дифференциального напряжения смесителя фиг.3 от напряжения ux по каналу «Х» при разных напряжениях Uy канала «Y».

На фиг.5 показана зависимость модуля коэффициента усиления но напряжению Ку смесителя фиг.3 от напряжения управления uy по каналу «Y».

На фиг.6 представлена осциллограмма выходного сигнала смесителя фиг.3, а на фиг.7 - спектр выходного сигнала смесителя-прототипа при fx=1 МГц, fy=10 кГц, ux=10 мВ, uy=10 мВ.

На фиг.8 показан спектр выходных сигналов заявляемого СС фиг.3 при fy=1 МГц, fx=10 кГц, ux=10 мВ, uy=10 мВ.

Заявляемый смеситель двух сигналов фиг.2 содержит перемножающую ячейку Гильберта (1) с первым 2 и вторым 3 противофазными токовыми выходами и первым 4 и вторым 5 противофазными токовыми входами, источник сигнала 6 канала «X» 6, связанный с базами транзисторов перемножающей ячейки Гильберта 1, первый 7 выходной транзистор канала «Y», коллектор которого соединен со вторым 5 токовым входом перемножающей ячейки Гильберта, а эмиттер через первый 8 токостабилизирующий двухполюсник связан с первой 9 шиной источника питания, второй 10 выходной транзистор канала «Y», эмиттер которого через второй 11 токостабилизирующий двухполюсник связан с первой 9 шиной источника питания, источник сигнала канала «Y» 12, связанный с эмиттером второго 10 выходного транзистора канала «Y» через первый 13 разделительный конденсатор, третий 14 токостабилизирующий двухполюсник, связанный с базой второго 10 выходного транзистора канала «Y», второй 15 разделительный конденсатор, цепь нагрузки 16, включенную между второй 17 шиной источника питания и первым 2 и вторым 3 противофазными токовыми выходами перемножающей ячейки Гильберта, которые связаны с первым 18 и вторым 19 потенциальными выходами устройства, третью общую шину источника питания, коллектор второго 10 выходного транзистора канала «Y» соединен с первым 4 токовым входом перемножающей ячейки Гильберта, база второго 10 выходного транзистора канала «Y» соединена с базой первого 7 выходного транзистора канала «Y», а также базами первого 20 и второго 21 дополнительных транзисторов, которые соединены с коллекторами данных 20, 21 дополнительных транзисторов, причем эмиттер первого 20 дополнительного транзистора соединен с эмиттером второго 10 выходного транзистора канала «Y», эмиттер второго 21 дополнительного транзистора соединен с эмиттером первого 7 выходного транзистора канала «Y», а второй 15 разделительный конденсатор включен по переменному току между эмиттером второго 7 выходного транзистора канала «Y» и третьей общей шиной источника питания.

На фиг.2 перемножающая ячейка Джильберта 1 реализована но классической схеме на транзисторах 20, 21, 22, 23. Цепь нагрузки 16 выполнена (в частном случае) на резисторах 24 и 25.

Рассмотрим работу СС фиг.2.

Синусоидальные напряжения первого смешиваемого сигнала ux (на входах Вх.х, канала «X») и второго смешиваемого сигнала uy (на входе Вх.у канала «Y») «перемножаются» традиционным образом в ячейке Джильберта 1.

Переменное входное напряжение канала uy для диапазона частот, когда можно пренебречь сопротивлением первого 13 и второго 15 разделительных конденсаторов, создает токи эмиттера транзисторов 20 и 21:

где rэ20=rэ21=rэ - сопротивления эмиттерных переходов транзисторов 20 и 21;

φт=26 мВ - температурный потенциал;

2I0 - статический ток третьего 14 токостабилизирующего двухполюсника.

Так как эмиттерно-базовые переходы транзисторов 20 и 10, а также 21 и 7 включены параллельно, коллекторные токи транзисторов 10 и 7, и соответственно, входные токи перемножающей ячейки Гильберта 1 будут противофазны. Это является необходимым условием качественного смещения сигналов.

Анализ фиг.4, а также фиг.5, 6, 7 и 8 показывает, что смеситель фиг.2 обеспечивает достаточно качественное преобразование сигналов ux и uy.

Для обеспечения работоспособности СС-прототипа минимально-возможное напряжение отрицательного источника питания находится из уравнения Кирхгофа:

В заявляемом СС фиг.2:

Таким образом, в предлагаемом устройстве минимальное напряжение питания отличается от напряжения питания СС-прототипа фиг.1 на величину:

В практических схемах с учетом реальных параметров элементов ΔE(-)≥1÷1.5 В, что весьма существенно для СС с низковольтным питанием.

Таким образом, заявляемый смеситель двух сигналов имеет существенные преимущества в сравнении с прототипом, а также другими СС с малым напряжением питания, использующим низковольтный однофазный вход по каналу «Y».

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US №2008/113644.

2. Патентная заявка US №2006/0232334, fig.1.

3. Патент US №4.965.528. fig.2.

4. Патент US №6.744.308.

5. Патент US №7.633328.

6. Патент US №7,110.740.

7. Патентная заявка US №2009/0085663, fig.2.

8. Патент US №7.514.981. fig.1.

9. Авт.св. СССР №642843.

10. Патент US №5.933.771, fig.2.

11. Патент US №6.016.079, fig.4.

12. Патент US №5.057,784.

13. Патент US №4.286.226.

14. Патентная заявка US №2008/0261552, fig.1.

15. Патент US №6.373.345. fig.2.

16. Патентная заявка US №2010/0164595, fig.2.

17. Патентная заявка US №2010/0141325.

18. Патент US №4.344.188, fig.1, fig.3.

19. Патент ЕР 1455441.

20. Патент US №7.812.775, fig.20. fig, 16.

21. Патент ЕР 2235559, fig.3.

22. Патент US №7.676.212, fig.2.

23. Патентная заявка US №2008/0180156, fig.1, fig.5.

24. Патент US №5,825.231, fig.1.

25. Патент US №5.825.231, fig.7.

26. Патент US №7.514.981, fig.6.

27. Патент US №4.331.929.

28. Патент EP №2235559, fig.3.

29. Патент US №7.514.481, fig.5.

30. Патентная заявка US №2006/0232334, fig.7.

31. Патент DE №10351115, fig.3.

Смеситель сигналов, содержащий перемножающую ячейку Гильберта (1) с первым (2) и вторым (3) противофазными токовыми выходами и первым (4) и вторым (5) противофазными токовыми входами, источник сигнала (6) канала «X» (6), связанный с базами транзисторов перемножающей ячейки Гильберта (1), первый (7) выходной транзистор канала «Y», коллектор которого соединен со вторым (5) токовым входом перемножающей ячейки Гильберта, а эмиттер через первый (8) токостабилизирующий двухполюсник связан с первой (9) шиной источника питания, второй (10) выходной транзистор канала «Y», эмиттер которого через второй (11) токостабилизирующий двухполюсник связан с первой (9) шиной источника питания, источник сигнала канала «Y» (12), связанный с эмиттером второго (10) выходного транзистора канала «Y» через первый (13) разделительный конденсатор, третий (14) токостабилизируюший двухполюсник, связанный с базой второго (10) выходного транзистора канала «Y», второй (15) разделительный конденсатор, цепь нагрузки (16), включенную между второй (17) шиной источника питания и первым (2) и вторым (3) противофазными токовыми выходами перемножающей ячейки Гильберта, которые связаны с первым (18) и вторым (19) потенциальными выходами устройства, третью общую шину источника питания, отличающийся тем, что коллектор второго (10) выходного транзистора канала «Y» соединен с первым (4) токовым входом перемножающей ячейки Гильберта, база второго (10) выходного транзистора канала «Y» соединена с базой первого (7) выходного транзистора канала «Y», а также базами первого (20) и второго (21) дополнительных транзисторов, которые соединены с коллекторами данных (20), (21) дополнительных тратнзисторов, причем эмиттер первого (20) дополнительного транзистора соединен с эмиттером второго (10) выходного транзистора канала «Y», эмиттер второго (21) дополнительного транзистора соединен с эмиттером первого (7) выходного транзистора канала «Y», а второй (15) разделительный конденсатор включен по переменному току между эмиттером второго (7) выходного транзистора канала «Y» и третьей общей шиной источника питания.