Операционный усилитель с парафазным выходом

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, драйверах дифференциальных линий связи, фильтрах, компараторах т.п.). Технический результат заключается в создании условий, при которых выходное статическое синфазное напряжение ОУ будет иметь высокую стабильность и близкое к нулю численное значение при нулевых входных сигналах. Операционный усилитель с парафазным выходом содержит первый и второй входные трехполюсники, первый и второй согласующие трехполюсники, первый и второй выходные трехполюсники, с первого по четвертый токостабилизирующие двухполюсники, первый и второй резисторы обратной связи. 2 з.п. ф-лы, 11 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, мостовых усилителях мощности, драйверах дифференциальных линий связи, фильтрах, компараторах т.п.).

Известны схемы классических дифференциальных операционных усилителей (ОУ) с парафазным выходом на основе входного каскода, которые стали основой многих серийных аналоговых микросхем (ОРА177, RC4805 и т.д.). ОУ данного класса широко применяются в структуре СВЧ-устройств [1-18], реализованных на базе SiGe-технологий. Это связано с возможностью построения на их основе активных RC-фильтров гигагерцового диапазона для современных и перспективных систем связи, драйверов дифференциальных линий связи между СФ-блоками A/d и D/a-классов и т.п. [19-21].

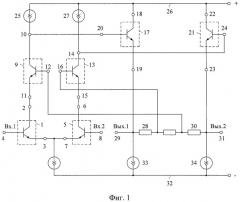

Ближайшим прототипом (фиг.1) заявляемого устройства является операционный усилитель, описанный в патенте US 5568092, fig.8. Кроме этого, данная архитектура присутствует во многих других патентах [1-18]. Он содержит первый 1 входной трехполюсник с коллекторным 2, эмиттерным 3 и базовым 4 входами, второй 5 входной трехполюсник с коллекторным 6, эмиттерным 7 и базовым 8 входами, первый 9 согласующий трехполюсник с коллекторным 10, эмиттерным 11 и базовым 12 входами, второй 13 согласующий трехполюсник с коллекторным 14, эмиттерным 15 и базовым 16 входами, первый 17 выходной трехполюсник с коллекторным 18, эмиттерным 19 и базовым 20 входами, второй 21 выходной трехполюсник с коллекторным 22, эмиттерным 23 и базовым 24 входами, первый 25 токостабилизирующий двухполюсник, включенный между коллекторным входом 10 первого 9 согласующего трехполюсника, связанным с базовым входом 20 первого 17 выходного трехполюсника и первой 26 шиной источника питания, второй 27 токостабилизирующий двухполюсник, включенный между коллекторным входом 14 второго 13 согласующего трехполюсника, связанным с базовым входом 24 второго 21 выходного трехполюсника и первой 26 шиной источника питания, первый 28 резистор обратной связи, включенный между эмиттерным входом 19 первого 17 выходного трехполюсника, связанным с первым 29 выходом устройства, и базовым входом 16 второго 13 согласующего трехполюсника, второй 30 резистор обратной связи, включенный между эмиттерным входом 23 второго 21 выходного трехполюсника, связанным со вторым 31 выходом устройства, и базовым входом 12 первого 9 согласующего трехполюсника, причем первый 29 выход устройства связан со второй 32 шиной источника питания через третий 33 токостабилизирующий двухполюсник, второй 31 выход устройства связан со второй 32 шиной источника питания через четвертый 34 токостабилизирующий двухполюсник, а коллекторные входы 18, 22 первого 17 и второго 21 выходных трехполюсников соединены с первой 26 шиной источника питания.

Основная цель предлагаемого изобретения состоит в создании условий, при которых выходное статическое синфазное напряжение ОУ будет иметь высокую стабильность и близкое к нулю численное значение при нулевых входных сигналах. Это значительно упрощает согласование парафазных выходов ОУ с последующими функциональными узлами различных многокаскадных устройств преобразования сигналов, позволяет обеспечить более эффективное использование напряжений питания ОУ - в этих схемах выходные переменные напряжения изменяются относительно общей шины.

Поставленная задача решается тем, что в операционном усилителе с парафазным выходом фиг.1, содержащем первый 1 входной трехполюсник с коллекторным 2, эмиттерным 3 и базовым 4 входами, второй 5 входной трехполюсник с коллекторным 6, эмиттерным 7 и базовым 8 входами, первый 9 согласующий трехполюсник с коллекторным 10, эмиттерным 11 и базовым 12 входами, второй 13 согласующий трехполюсник с коллекторным 14, эмиттерным 15 и базовым 16 входами, первый 17 выходной трехполюсник с коллекторным 18, эмиттерным 19 и базовым 20 входами, второй 21 выходной трехполюсник с коллекторным 22, эмиттерным 23 и базовым 24 входами, первый 25 токостабилизирующий двухполюсник, включенный между коллекторным входом 10 первого 9 согласующего трехполюсника, связанным с базовым входом 20 первого 17 выходного трехполюсника и первой 26 шиной источника питания, второй 27 токостабилизирующий двухполюсник, включенный между коллекторным входом 14 второго 13 согласующего трехполюсника, связанным с базовым входом 24 второго 21 выходного трехполюсника и первой 26 шиной источника питания, первый 28 резистор обратной связи, включенный между эмиттерным входом 19 первого 17 выходного трехполюсника, связанным с первым 29 выходом устройства, и базовым входом 16 второго 13 согласующего трехполюсника, второй 30 резистор обратной связи, включенный между эмиттерным входом 23 второго 21 выходного трехполюсника, связанным со вторым 31 выходом устройства, и базовым входом 12 первого 9 согласующего трехполюсника, причем первый 29 выход устройства связан со второй 32 шиной источника питания через третий 33 токостабилизирующий двухполюсник, второй 31 выход устройства связан со второй 32 шиной источника питания через четвертый 34 токостабилизирующий двухполюсник, а коллекторные входы 18, 22 первого 17 и второго 21 выходных трехполюсников соединены с первой 26 шиной источника питания, предусмотрены новые элементы и связи - эмиттерный вход 3 первого 1 входного трехполюсника соединен с эмиттерным входом 11 первого 9 согласующего трехполюсника, эмиттерный вход 7 второго 5 входного трехполюсника соединен с эмиттерным входом 15 второго 13 согласующего двухполюсника, коллекторные входы 2 и 6 первого 1 и второго 5 входных трехполюсников соединены со второй 32 шиной источника питания, причем базовые входы 12 и 16 первого 9 и второго 13 согласующих трехполюсников соединены друг с другом.

На чертеже фиг.1 показана схема ОУ-прототипа.

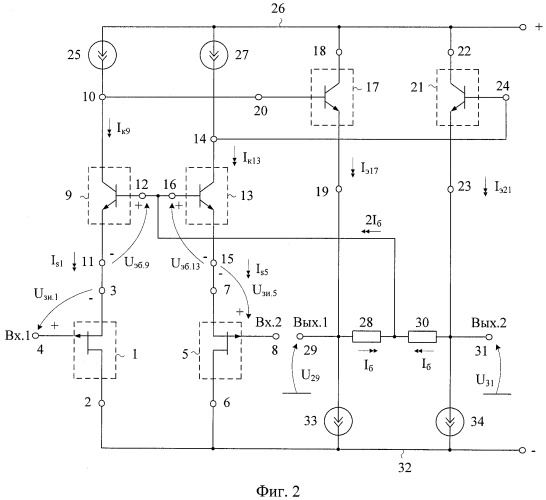

На чертеже фиг.2 показана схема заявляемого устройства в соответствии с п.1 формулы изобретения для случая, когда первый 1 и второй 5 входные трехполюсники реализованы на основе полевых транзисторов с управляющим p-n переходом, а первый 9 и второй 13 согласующие трехполюсники, а также первый 17 и второй 21 выходные трехполюсники выполнены в виде биполярных транзисторов одного типа проводимости.

На чертеже фиг.3, в соответствии с п.2 формулы изобретения, приведены частные варианты построения первого 1 и второго 5 входных трехполюсников, первого 9 и второго 13 согласующих трехполюсников, а также первого 17 и второго 21 выходных трехполюсников ОУ фиг.2.

На чертеже фиг.4, в соответствии с п.3 формулы изобретения, приведены примеры построения первого 1 и второго 5 входных трехполюсников, первого 9 и второго 13 согласующих трехполюсников, а также первого 17 и второго 21 выходных трехполюсников ОУ фиг.2.

Чертеж фиг.5 полностью соответствует п.3 формулы изобретения.

На чертеже фиг.6 приведена схема ОУ фиг.5 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов ФГУ НПП «Пульсар».

На чертеже фиг.7 приведена частотная зависимость коэффициента усиления по напряжению схемы ОУ фиг.6.

Чертеж фиг.8 характеризует зависимость выходных напряжений ОУ фиг.6 при синусоидальном входном сигнале.

На чертеже фиг.9 приведена схема ОУ фиг.2 в среде компьютерного моделирования PSpise на моделях интегральных транзисторов аналогового базового матричного кристалла АБМК_1_3 (НПО «Интеграл» г.Минск).

На чертеже фиг.10 приведена частотная зависимость коэффициента усиления по напряжению схемы ОУ фиг.9.

Чертеж фиг.11 характеризует зависимость выходных напряжений ОУ фиг.9 при синусоидальном входном сигнале.

Операционный усилитель с парафазным выходом фиг.2 содержит первый 1 входной трехполюсник с коллекторным 2, эмиттерным 3 и базовым 4 входами, второй 5 входной трехполюсник с коллекторным 6, эмиттерным 7 и базовым 8 входами, первый 9 согласующий трехполюсник с коллекторным 10, эмиттерным 11 и базовым 12 входами, второй 13 согласующий трехполюсник с коллекторным 14, эмиттерным 15 и базовым 16 входами, первый 17 выходной трехполюсник с коллекторным 18, эмиттерным 19 и базовым 20 входами, второй 21 выходной трехполюсник с коллекторным 22, эмиттерным 23 и базовым 24 входами, первый 25 токостабилизирующий двухполюсник, включенный между коллекторным входом 10 первого 9 согласующего трехполюсника, связанным с базовым входом 20 первого 17 выходного трехполюсника и первой 26 шиной источника питания, второй 27 токостабилизирующий двухполюсник, включенный между коллекторным входом 14 второго 13 согласующего трехполюсника, связанным с базовым входом 24 второго 21 выходного трехполюсника и первой 26 шиной источника питания, первый 28 резистор обратной связи, включенный между эмиттерным входом 19 первого 17 выходного трехполюсника, связанным с первым 29 выходом устройства, и базовым входом 16 второго 13 согласующего трехполюсника, второй 30 резистор обратной связи, включенный между эмиттерным входом 23 второго 21 выходного трехполюсника, связанным со вторым 31 выходом устройства, и базовым входом 12 первого 9 согласующего трехполюсника, причем первый 29 выход устройства связан со второй 32 шиной источника питания через третий 33 токостабилизирующий двухполюсник, второй 31 выход устройства связан со второй 32 шиной источника питания через четвертый 34 токостабилизирующий двухполюсник, а коллекторные входы 18, 22 первого 17 и второго 21 выходных трехполюсников соединены с первой 26 шиной источника питания. При этом эмиттерный вход 3 первого 1 входного трехполюсника соединен с эмиттерным входом 11 первого 9 согласующего трехполюсника, эмиттерный вход 7 второго 5 входного трехполюсника соединен с эмиттерным входом 15 второго 13 согласующего двухполюсника, коллекторные входы 2 и 6 первого 1 и второго 5 входных трехполюсников соединены со второй 32 шиной источника питания, причем базовые входы 12 и 16 первого 9 и второго 13 согласующих трехполюсников соединены друг с другом.

На чертежах фиг.3 и фиг.2, в соответствии с п.2 формулы изобретения, первый 1 и второй 5 входные трехполюсники реализованы на основе полевых транзисторов 35 и 36 с управляющим p-n переходом, а первый 9 и второй 13 согласующие трехполюсники, а также первый 17 и второй 21 выходные трехполюсники выполнены в виде биполярных транзисторов 37, 38, 39, 40 одного типа проводимости.

На чертеже фиг.4, а также фиг.5, в соответствии с п.3 формулы изобретения, первый 1 и второй 5 входные трехполюсники выполнены в виде биполярных транзисторов 41, 42 одного типа проводимости, первый 9, второй 13 согласующие транзисторы и первый 17 и второй 21 выходные трехполюсники реализованы на транзисторах 43, 44, 45, 46 другого типа проводимости, первый 29 выход устройства связан со второй 32 шиной источника питания через последовательно соединенные первую 47 цепь смещения потенциалов и третий 33 токостабилизирующий двухполюсник, а второй 31 выход устройства связан со второй 32 шиной источника питания через вторую 48 цепь смещения потенциалов и четвертый 34 токостабилизирующий двухполюсник, причем общий узел первой 47 цепи смещения потенциалов и третьего 33 токостабилизирующего двухполюсника соединен с третьим 49 выходом устройства, а общий узел второй 48 цепи смещения потенциалов и четвертого 34 токостабилизирующего двухполюсника соединен с четвертым 50 выходом устройства.

Рассмотрим работу ОУ фиг.2.

Статический режим по току транзисторов предлагаемого ОУ устанавливается токостабилизирующими двухполюсниками 25, 27, 33 и 34:

где I25, I27, I33, I34 - токи токостабилизирующих двухполюсников 25, 27, 33, 34;

Is1, Is5 - токи истоков транзисторов, образующих входные трехполюсники 1 и 5;

Iк13, Iк9 - токи коллектора транзисторов, образующих согласующие трехполюсники 9 и 13;

Iэ17, Iэ21 - токи эмиттера транзисторов, образующих выходные трехполюсники 17 и 21;

I0 - некоторое заданное значение опорного тока, например, 1 мА.

В соответствии со вторым законом Киргофа статические напряжения U29, U31 на выходах 29 и 31 ОУ фиг.2 при нулевых напряжениях на входах Вх.1, Вх.2 удовлетворяют условиям:

где Uэб.9=Uэб.13 - напряжения «эмиттер-база» транзисторов, образующих согласующие трехполюсники 9 и 13;

Uзи.1, Uзи.5 - напряжение затвор исток транзисторов, образующих входные трехполюсники 1 и 5;

R28, R30 - сопротивления резисторов 28 и 30;

Iб - ток базы транзисторов, образующих согласующие трехполюсники 9 и 13.

Ток истока Is полевых транзисторов, образующих входные трехполюсники 1 и 5, определяется в первом приближении формулой:

где Is - ток истока полевого транзистора;

Ic.max - максимальный ток полевого транзистора при Uзи=0;

Uзи - напряжение затвор-исток (0≤Uзи≤Uотс);

Uотс - напряжение отсечки полевого транзистора.

Для получения Uзи=Uэб.9=Uэб.13≈0,7 В, при котором U29≈0, U31≈0, необходимо, чтобы токи токостабилизирующих двухполюсников 25 и 27 удовлетворяли условию

Или

Если эти токи больше, чем , то выходные напряжения ОУ U29=U31 будут иметь положительное смещение относительно общей шины. Если , то эти напряжения U29≈U31 смещаются к отрицательной шине питания.

Если в схеме фиг.2 обеспечить Uзи.5=Uзи.1=Uэб.9=Uэб.13≈0,7 В за счет соответствующего выбора токов , то теоретическое значение U29=U31 с высокой точностью будет соответствовать нулевому уровню:

С учетом типовых численных значений Iб и R28=R30 в практических схемах ОУ из уравнения (6) можно сделать вывод о том, что в заявляемом ОУ статические выходные напряжения U29=U31 близки к единицам милливольт.

В зависимости от схемотехники трехполюсников 1, 5, 9, 13 можно установить и другие заданные величины статического выходного синфазного напряжения заявляемого ОУ.

Графики фиг.8 и фиг.11 показывают, что в схемах ОУ фиг.2 и фиг.5 синусоидальные выходные напряжения имеют нулевой уровень статического смещения относительно общей шины.

Таким образом, заявляемый операционный усилитель имеет малый нулевой уровень выходного синфазного напряжения. Это весьма существенно для его согласования с последующими функциональными узлами различных систем на кристалле, а также для получения более широкого диапазона изменения выходных противофазных напряжений.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US №7.737.783.

2. Патентная заявка US 2010/007419, fig.3.

3. Патент US №5.568.092, fig.1.

4. Патент US №6.100.759, fig.3.

5. Патентная заявка US 2002/0093380, fig.1.

6. Патентная заявка US 2009/0195312, fig.1.

7. Патент US №3.541.465, fig.3.

8. Патент US №5.500.623, fig.6.

9. Патентная заявка US 2005/0104661, fig.3.

10. Патент US №6.396.346, fig.3А.

11. Патент US №5.440.271, fig.1.

12. Патент US №5.510.745, fig.25.

13. Патент US №5.774.020, fig.2.

14. Патент US №6.262.628, fig.14b.

15. Патент US №6.011.431, fig.6.

16. Патент GB №1520085, fig.2.

17. Патентная заявка US 2006/0044064, fig.2.

18. Патентная заявка US 2006/0181347, fig.2.

19. Budyakov, A. Design of Fully Differential OpAmps for GHz Range Applications [Текст] / Budyakov A., Schmalz K., Prokopenko N., Scheytt C., Ostrovskyy P. // Проблемы современной аналоговой микросхемотехники: Сб. материалов VI Международного научно-практического семинара. В 3-х ч. Ч.1. Функциональные узлы аналоговых интегральных схем и сложных функциональных блоков / под ред. Н.Н.Прокопенко. - Шахты: Изд-во ЮРГУЭС, 2007. - С.106-110.

20. S.P.Voinigescu et al., "Design Methodology and Applications of SiGe BiCMOS Cascode Opamps with up to 37-GHz Unity Gain Bandwidth," IEEE CSICS, Techn. Digest, pp.283-286, Nov. 2005, фиг.2.

21. S.P.Voinigescu et al., "SiGe BiCMOS for Analog, High-Speed Digital and Millimetre-Wave Applications Beyond 50 GHz," IEEE BCTM, pp.1-8, Oct. 2006.

1. Операционный усилитель с парафазным выходом, содержащий первый (1) входной трехполюсник с коллекторным (2), эмиттерным (3) и базовым (4) входами, второй (5) входной трехполюсник с коллекторным (6), эмиттерным (7) и базовым (8) входами, первый (9) согласующий трехполюсник с коллекторным (10), эмиттерным (11) и базовым (12) входами, второй (13) согласующий трехполюсник с коллекторным (14), эмиттерным (15) и базовым (16) входами, первый (17) выходной трехполюсник с коллекторным (18), эмиттерным (19) и базовым (20) входами, второй (21) выходной трехполюсник с коллекторным (22), эмиттерным (23) и базовым (24) входами, первый (25) токостабилизирующий двухполюсник, включенный между коллекторным входом (10) первого (9) согласующего трехполюсника, связанным с базовым входом (20) первого (17) выходного трехполюсника и первой (26) шиной источника питания, второй (27) токостабилизирующий двухполюсник, включенный между коллекторным входом (14) второго (13) согласующего трехполюсника, связанным с базовым входом (24) второго (21) выходного трехполюсника и первой (26) шиной источника питания, первый (28) резистор обратной связи, включенный между эмиттерным входом (19) первого (17) выходного трехполюсника, связанным с первым (29) выходом устройства, и базовым входом (16) второго (13) согласующего трехполюсника, второй (30) резистор обратной связи, включенный между эмиттерным входом (23) второго (21) выходного трехполюсника, связанным со вторым (31) выходом устройства, и базовым входом (12) первого (9) согласующего трехполюсника, причем первый (29) выход устройства связан со второй (32) шиной источника питания через третий (33) токостабилизирующий двухполюсник, второй (31) выход устройства связан со второй (32) шиной источника питания через четвертый (34) токостабилизирующий двухполюсник, а коллекторные входы (18), (22) первого (17) и второго (21) выходных трехполюсников соединены с первой (26) шиной источника питания, отличающийся тем, что эмиттерный вход (3) первого (1) входного трехполюсника соединен с эмиттерным входом (11) первого (9) согласующего трехполюсника, эмиттерный вход (7) второго (5) входного трехполюсника соединен с эмиттерным входом (15) второго (13) согласующего двухполюсника, коллекторные входы (2) и (6) первого (1) и второго (5) входных трехполюсников соединены со второй (32) шиной источника питания, причем базовые входы (12) и (16) первого (9) и второго (13) согласующих трехполюсников соединены друг с другом.

2. Операционный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (1) и второй (5) входные трехполюсники реализованы на основе полевых транзисторов с управляющим р-n переходом, а первый (9) и второй (13) согласующие трехполюсники, а также первый (17) и второй (21) выходные трехполюсники выполнены в виде биполярных транзисторов одного типа проводимости.

3. Операционный усилитель с парафазным выходом по п.1, отличающийся тем, что первый (1) и второй (5) входные трехполюсники выполнены в виде биполярных транзисторов одного типа проводимости, первый (9), второй (13) согласующие транзисторы и первый (17) и второй (21) выходные трехполюсники реализованы на транзисторах другого типа проводимости, первый (29) выход устройства связан со второй (32) шиной источника питания через последовательно соединенные первую (47) цепь смещения потенциалов и третий (33) токостабилизирующий двухполюсник, а второй (31) выход устройства связан со второй (32) шиной источника питания через вторую (48) цепь смещения потенциалов и четвертый (34) токостабилизирующий двухполюсник, причем общий узел первой (47) цепи смещения потенциалов и третьего (33) токостабилизирующего двухполюсника соединен с третьим (49) выходом устройства, а общий узел второй (48) цепи смещения потенциалов и четвертого (34) токостабилизирующего двухполюсника соединен с четвертым (50) выходом устройства.