Асинхронный двоичный счетчик

Иллюстрации

Показать всеИзобретение относится к цифровой вычислительной технике. Техническим результатом является обеспечение решения комбинаторной задачи формирования всех возможных N-разрядных двоичных кодовых комбинаций, в которых произвольные К-разрядов (K≤N) имеют фиксированные значения. Устройство содержит последовательно подключенные идентичные счетные секции, каждая из которых содержит счетный триггер, схему управления для его параллельной загрузки и схему управления межразрядным переносом, состоящую из элемента ИЛИ, трех элементов И, элемента НЕ. 2 ил.

Реферат

Изобретение относится к цифровой вычислительной технике и предназначено для решения комбинаторной задачи формирования всех возможных N-разрядных двоичных кодовых комбинаций, в которых произвольные К-разрядов (К≤N) имеют фиксированные значения. Данная комбинаторная задача возникает, например, при восстановлении произвольной дизъюнктивной нормальной формы логической функции до ее совершенной дизъюнктивной нормальной формы.

Наиболее близким по технической сути является широко известный асинхронный двоичный счетчик, смотри, например [Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. - М.: Радио и связь, 1990. - 512 с.].

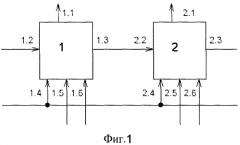

Данный асинхронный двоичный счетчик состоит из нескольких последовательно расположенных однотипных счетных секций, первые выходы которых являются выходом счетчика, вторые выходы предшествующих счетных секций соединены с первыми входами последующих счетных секций, первый вход первой счетной секции соединен со счетным входом счетчика, а второй выход последней счетной секции не подключен ни к одной из цепей, вторые входы счетных секций объединены между собой и подключены ко входу синхронизации параллельной загрузки счетчика, третьи входы счетных секций являются информационными входами параллельной загрузки счетчика, при этом каждая счетная секция содержит счетный триггер и схему управления для его параллельной загрузки.

Данный счетчик позволяет формировать возрастающую последовательность всех возможных N-разрядных двоичных чисел, начиная с произвольного начального числа D0, которое предварительно загружается в счетчик. При этом селекция N-разрядных двоичных кодовых комбинаций, в которых произвольные К-разрядов (К≤N) имеют фиксированные значения, может осуществляться только с помощью дополнительных внешних средств, обязательно включающих схему сравнения двух N-разрядных двоичных кодов.

Изобретение направлено на расширение функциональных возможностей асинхронного двоичного счетчика, за счет решения комбинаторной задачи формирования всех возможных N-разрядных двоичных кодовых комбинаций, в которых произвольные К-разрядов (К≤N) имеют фиксированные значения.

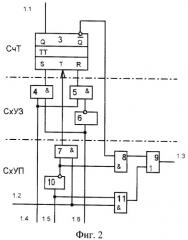

Это достигается тем, что в каждую счетную секцию 1.2 дополнительно вводится схема управления межразрядным переносом (СхУП), содержащая элемент ИЛИ 9, три элемента И 7, 8, 11 и элемент НЕ 10, вход которого соединен с четвертым входом счетной секции 1.5 и первым входом первого элемента И 11, второй вход которого подключен к первому входу счетной секции 1.2 и ко второму входу второго элемента И 7, выход которого подключен к счетному входу счетного триггера 3, первый вход второго элемента И 7 соединен с выходом элемента НЕ 10 и первым входом третьего элемента И 8, второй вход которого соединен с инверсным выходом счетного триггера 3, а выход третьего элемента И 8 соединен с первым входом элемента ИЛИ 9, второй вход которого соединен с выходом первого элемента И 11, а выход элемента ИЛИ 9 соединен со вторым выходом счетной секции 1.3, причем четвертые входы счетных секций 1.5 являются четвертыми входами счетчика для задания кода счетной маски.

На фиг.1 представлена структурная схема предлагаемого асинхронного двоичного счетчика, а на фиг.2 - функциональная схема счетной секции счетчика, состоящая из счетного триггера (СчТ), схемы управления загрузки (СхУЗ) и схемы управления межразрядным переносом (СхУП). Асинхронный двоичный счетчик работает следующим образом. На входы 1.5-2.5 счетчика подается двоичный код маски М={m1, … mJ, … mN}, определяющий номера разрядов счетчика, значения которых не должны изменяться при счете. Говоря иначе, код маски определяет фиксированные переменные x1, … xJ, … xN, которые формируются счетчиком на соответствующих его выходах 1.1-2.1. Если mJ=0 (J=от 1 до N), то счетчик реализует свой основной режим работы - формирует возрастающую последовательность всех возможных N-разрядных двоичных чисел, начиная с произвольного начального числа D0. Код числа D0={d1, … dJ, … dN} предварительно должен быть подан на входы 1.6-2.6 счетчика и записан в счетчик сигналом записи, который подается на вход 1.4 счетчика. Счетные импульсы подаются на вход 1.2 счетчика. Для формирования всех возможных N-разрядных двоичных кодовых комбинаций, в которых произвольные К-разрядов (К≤N) имеют фиксированные значения, соответствующие разряды в двоичном коде маски М должны быть установлены в 1, а кодом числа D0 задаются требуемые значения (0 или 1) соответствующих фиксированных переменных x1, … xJ, … xN. При этом, все свободные переменные (которые в процессе счета могут менять свои значения) предварительно должны иметь значение, равное 0, что так же реализуется с помощью задания исходного числа D0={d1, … dJ, … dN}.

Рассмотрим работу заявляемого асинхронного двоичного счетчика, число разрядов которого равно 4. Пусть требуется зафиксировать значения 2-го и 3-го разрядов счетчика, причем значение второго разряда должно быть 1 (т.е. x2=1), а третьего 0 (x3=0). Значения первого и четвертого разрядов изначально устанавливаются равными 0 (x1=x4=0). Для этих исходных данных необходимо: загрузить счетчик числом D0={0,1,0,0}; установить маску М={0,1,1,0}; подать на вход 1.2 счетчика счетные импульсы. В результате будет сформирована следующая последовательность кодов: 0100; 1100; 0101; 1101; 0100 …, которая при дальнейшем наличии счетных импульсов будет периодически повторяться с периодом, равным 2N-K.

Техническим результатом от использования заявляемого изобретения является дополнительная возможность простого решения комбинаторной задачи формирования всех возможных N-разрядных двоичных кодовых комбинаций, число которых равно 2N-K, и в которых произвольные К-разрядов (К≤N) имеют фиксированные значения.

Асинхронный двоичный счетчик, состоящий из нескольких последовательно расположенных идентичных счетных секций, первые выходы которых являются выходом счетчика, вторые выходы предшествующих счетных секций соединены с первыми входами последующих счетных секций, первый вход первой счетной секции соединен со счетным входом счетчика, а второй выход последней счетной секции не подключен ни к одной из цепей, вторые входы счетных секций объединены между собой и подключены ко входу синхронизации параллельной загрузки счетчика, третьи входы счетных секций являются информационными входами параллельной загрузки счетчика, при этом каждая счетная секция содержит счетный триггер и схему управления для его параллельной загрузки, отличающийся тем, что в каждую счетную секцию дополнительно введена схема управления межразрядным переносом, содержащая элемент ИЛИ, три элемента И и элемент НЕ, вход которого соединен с четвертым входом счетной секции и первым входом первого элемента И, второй вход которого подключен к первому входу счетной секции и ко второму входу второго элемента И, выход которого подключен к счетному входу счетного триггера, первый вход второго элемента И соединен с выходом элемента НЕ и первым входом третьего элемента И, второй вход которого соединен с инверсным выходом счетного триггера, а выход третьего элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход элемента ИЛИ соединен со вторым выходом счетной секции, причем четвертые входы счетных секций являются четвертыми входами счетчика для задания кода счетной маски.