Подложка активной матрицы, жидкокристаллическая панель, жидкокристаллическое дисплейное устройство, модуль жидкокристаллического дисплея и телевизионный приемник

Иллюстрации

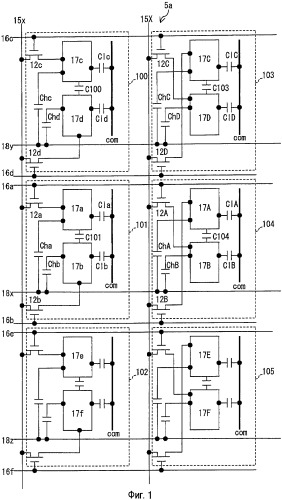

Показать всеПодложка активной матрицы содержит первую линию сигналов данных; первую-четвертую линии сигналов сканирования; первый-четвертый транзисторы; первый-четвертый пикселные электроды. Первый транзистор подключается к первой линии сигналов данных и первой линии сигналов сканирования, второй - к первой линии сигналов данных и второй линии сигналов сканирования, третий - к первой линии сигналов данных и третьей линии сигналов сканирования, а четвертый - к первой линии сигналов данных и четвертой линии сигналов сканирования. Первый и второй пикселные электроды располагаются в первой пикселной области, а третий и четвертый - во второй пикселной области, размещенной рядом с первой пикселной областью в направлении столбцов. Первый и второй пикселные электроды, а также третий и четвертый пикселные электроды подключаются друг к другу через разделительные конденсаторы. Технический результат - повышение качества отображения в жидкокристаллическом дисплейном устройстве с режимом разделения пикселов с емкостной связью. 3 н. и 22 з.п. ф-лы, 59 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к подложке активной матрицы, включающей в себя множество пикселных электродов в пикселной области, и к жидкокристаллическому дисплейному устройству (с режимом разделения пикселов), которое использует ее.

Уровень техники

В качестве меры для повышения зависимости показателей гамма от угла обзора в жидкокристаллических дисплейных устройствах (например, ограничения избыточной яркости и т.п. на экране) предложено жидкокристаллическое дисплейное устройство, которое управляет множеством субпикселов в пикселе так, чтобы иметь различную яркость, чтобы отображать полутон посредством модуляции по занимаемой площади этих субпикселов (режим разделения пикселов; например, см. патентный документ 1).

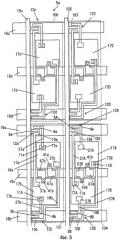

Как проиллюстрировано на Фиг.59, подложка активной матрицы, раскрытая в патентном документе 1, имеет пикселную область, предусмотренную между двумя смежными линиями 112 шины затвора; пикселный электрод 121a расположен на верхнем крае (в части, смежной с линией шины затвора) пикселной области, пикселный электрод 121b расположен посередине пикселной области; а пикселный электрод 121c расположен на нижнем крае (смежном со следующей смежной линией шины затвора) пикселной области. Пикселный электрод 121a и пикселный электрод 121c подключаются к отводному проводу 129 истока, который выдается из электрода 116s истока транзистора 116. Отводной провод 129 истока подключается к управляющему электроду 118; управляющий электрод 118 перекрывается посредством пикселного электрода 112b через изолирующий слой.

Средний пикселный электрод 121b имеет емкостную связь с пикселными электродами 121a и 121c (режим разделения пикселов с емкостной связью). В жидкокристаллическом дисплейном устройстве, которое использует эту подложку активной матрицы, субпикселы, соответствующие пикселным электродам 121a и 121c, выступают в качестве ярких субпикселов, а субпикселы, соответствующие пикселному электроду 121b, выступают в качестве темных субпикселов. Следовательно, полутон отображается посредством модуляции по занимаемой площади ярких субпикселов (2 субпикселов) и темного субпиксела (1 субпиксела).

Список библиографических ссылок

Патентный документ 1. Публикация заявки на патент (Япония), Tokukai, номер 2006-39290 (дата публикации: 9 февраля 2006 г.).

Сущность изобретения

Тем не менее, в случае если подложка активной матрицы, аналогичная проиллюстрированной на Фиг.59, применяется к жидкокристаллическому дисплейному устройству с MVA-режимом, считается, что один субпиксел включает в себя 1 (яркий или темный)*4=4 домена. Следовательно, остается запас для улучшения характеристик угла обзора.

Цель настоящего изобретения заключается в том, чтобы улучшать характеристики угла обзора в жидкокристаллическом дисплейном устройстве с режимом разделения пикселов с емкостной связью.

Жидкокристаллическое дисплейное устройство настоящего изобретения включает в себя: пикселные электроды; линии сигналов сканирования; и транзисторы, причем каждый из транзисторов подключается к одной из линий сигналов сканирования, при этом: два пикселных электрода расположены в соответствующей пикселной области таким образом, что два пикселных электрода подключаются друг к другу через конденсатор, пикселная область ассоциирована с двумя линиями сигналов сканирования, и один из транзисторов, который подключается к одной из двух линий сигналов сканирования, ассоциированных с пикселной областью, подключается к одному из двух пикселных электродов, расположенных в пикселной области, а другой из транзисторов, который подключается к другой из двух линий сигналов сканирования, ассоциированных с пикселной областью, подключается к другому из двух пикселных электродов, расположенных в пикселной области.

В жидкокристаллическом дисплейном устройстве, включающем в себя настоящую подложку активной матрицы, в предварительно определенных кадрах, одна из двух линий сигналов сканирования сканируется на предмет записи электрического потенциала сигнала в пикселный электрод, который подключается к одной из двух линий сигналов сканирования, через транзистор, подключенный к одной из двух линий сигналов сканирования, и в других кадрах, отличных от предварительно определенных кадров, другая из двух линий сигналов сканирования сканируется на предмет записи электрического потенциала сигнала в пикселный электрод, который подключается к другой из двух линий сигналов сканирования, через транзистор, подключенный к другой из двух линий сигналов сканирования. Это задает субпиксел как яркий субпиксел (в ходе полутонового отображения) в одном кадре и как темный субпиксел (в ходе полутонового отображения) в другом кадре. Как результат, улучшаются характеристики угла обзора жидкокристаллического дисплейного устройства.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что две линии сигналов сканирования, ассоциированные с пикселной областью, (i) расположены с каждой стороны пикселной области, или (ii) расположены так, что две линии сигналов сканирования перекрываются посредством любого края пикселной области.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что транзистор, который подключается к одному из двух пикселных электродов, расположенных в пикселной области, и транзистор, который подключается к другому из двух пикселных электродов, расположенных в пикселной области, подключаются к одной линии сигналов данных.

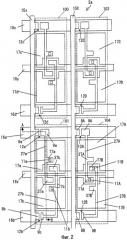

Настоящая подложка активной матрицы может конфигурироваться таким образом, что пикселная область дополнительно включает в себя: электрод разделительного конденсатора, электрически подключенный к одному из двух пикселных электродов, расположенных в пикселной области, причем другой из двух пикселных электродов, расположенных в пикселной области, перекрывает электрод разделительного конденсатора таким образом, что изолирующий слой размещается между другим из двух пикселных электродов и электродом разделительного конденсатора.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что пикселная область дополнительно включает в себя: два электрода разделительного конденсатора, причем один из двух электродов разделительного конденсатора электрически подключается к одному из двух пикселных электродов, расположенных в пикселной области, один из двух электродов разделительного конденсатора перекрывается посредством другого из двух пикселных электродов, расположенных в пикселной области, к которому сам один из двух электродов разделительного конденсатора электрически не подключается, причем другой из двух электродов разделительного конденсатора электрически подключается к другому из двух пикселных электродов, расположенных в пикселной области, другой из двух электродов разделительного конденсатора перекрывается посредством одного из двух пикселных электродов, расположенных в пикселной области, к которому сам другой из двух электродов разделительного конденсатора электрически не подключается, причем пикселные электроды перекрывают электроды разделительного конденсатора таким образом, что изолирующий слой размещается между ними.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что два пикселных электрода и электроды разделительного конденсатора электрически подключаются к соответствующему одному и другому из двух пикселных электродов, располагаемых таким образом, что плоская форма и плоская конфигурация пикселных электродов и электродов разделительного конденсатора при просмотре со стороны одной из двух линий сигналов сканирования является идентичной форме и конфигурации при просмотре со стороны другой из двух линий сигналов сканирования.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что пикселная область дополнительно включает в себя: провод накопительного конденсатора, при этом провод накопительного конденсатора формирует накопительную емкость с соответствующими электродами разделительного конденсатора.

Подложка активной матрицы может конфигурироваться таким образом, что, по меньшей мере, один из двух пикселных электродов, расположенных в пикселной области, формирует накопительную емкость с линией сигналов сканирования, ассоциированной с пикселной областью, размещаемой перед пикселной областью.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что две линии сигналов сканирования, ассоциированные с пикселной областью, расположены так, что две пикселных области, выровненные в направлении строк, ассоциированы с ней, причем каждая из двух пикселных областей включает в себя два пикселных электрода, выровненные в направлении столбцов, где направление строк - это направление, в котором идут линии сигналов сканирования, один из транзисторов, который подключается к одному из двух пикселных электродов, которые расположены рядом друг с другом в направлении строк, подключается к одной из двух линий сигналов сканирования, ассоциированных с двумя пикселными областями, а другой из транзисторов, который подключается к другому из двух пикселных электродов, которые расположены рядом друг с другом в направлении строк, подключается к другой из двух линий сигналов сканирования, ассоциированных с двумя пикселными областями.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что область, в которой токопроводящий электрод транзистора, подключенного к одному из двух пикселных электродов, расположенных в пикселной области, и токопроводящая часть, электрически подключенная к этому токопроводящему электроду, перекрывают линию сигналов сканирования, подключенную к этому транзистору, имеет размер, идентичный размеру области, в которой токопроводящий электрод транзистора, подключенного к другому из двух пикселных электродов, и токопроводящая часть, электрически подключенная к этому токопроводящему электроду, перекрывают линию сигналов сканирования, подключенную к этому транзистору.

Настоящая подложка активной матрицы включает в себя: пикселные электроды; линии сигналов сканирования; и транзисторы, причем каждый из транзисторов подключается к одной из линий сигналов сканирования, в котором: зазор между двумя смежными пикселными областями ассоциирован с соответствующей одной из линий сигналов сканирования, два пикселных электрода расположены в соответствующей пикселной области таким образом, что два пикселных электрода подключаются друг к другу через конденсатор, один из транзисторов, причем один из транзисторов подключается к одной из линий сигналов сканирования, которая ассоциирована с одним из зазоров с каждой стороны пикселной области, подключается к одному из двух пикселных электродов, расположенных в пикселной области, а другой из транзисторов, причем другой из транзисторов подключается к другой из линий сигналов сканирования, которая ассоциирована с другим из зазоров с каждой стороны пикселной области, подключается к другому из двух пикселных электродов, расположенных в пикселной области.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что транзистор, подключенный к одному из двух пикселных электродов, расположенных в пикселной области, и транзистор, подключенный к другому из двух пикселных электродов, расположенных в пикселной области, подключаются к одной линии сигналов данных.

Настоящее жидкокристаллическое дисплейное устройство включает в себя подложку активной матрицы, в которой в предварительно определенных кадрах одна из двух линий сигналов сканирования сканируется на предмет записи электрического потенциала сигнала в пикселный электрод, подключенный к одной из двух линий сигналов сканирования, через транзистор, подключенный к одной из двух линий сигналов сканирования, и в других кадрах, отличных от предварительно определенных кадров, другая из двух линий сигналов сканирования сканируется на предмет записи электрического потенциала сигнала в пикселный электрод, подключенный к другой из двух линий сигналов сканирования, через транзистор, подключенный к другой из двух линий сигналов сканирования.

Настоящее жидкокристаллическое дисплейное устройство включает в себя: подложку активной матрицы, в которой: в каждом из кадров линии сигналов сканирования последовательно сканируются на предмет записи электрического потенциала сигнала в соответствующие пикселные электроды, подключенные к линиям сигналов сканирования, через соответствующие транзисторы, причем линии сигналов сканирования сканируются в предварительно определенных кадрах в направлении, противоположном направлению сканирования кадров, отличных от предварительно определенных кадров.

Настоящее жидкокристаллическое дисплейное устройство может конфигурироваться таким образом, что предварительно определенные кадры, сканирующие одну из двух линий сигналов сканирования, включают в себя идентичное число (i) кадров, в которых электрический потенциал сигнала положительной полярности записан в пикселный электрод, и (ii) кадров, в которых электрический потенциал сигнала отрицательной полярности записан в пикселный электрод, и другие кадры, отличные от предварительно определенных кадров, сканирующих другую из двух линий сигналов сканирования, включают в себя идентичное число (i) кадров, в которых электрический потенциал сигнала положительной полярности записан в пикселный электрод, и (ii) кадров, в которых электрический потенциал сигнала отрицательной полярности записан в пикселный электрод.

Настоящее жидкокристаллическое дисплейное устройство может конфигурироваться таким образом, что линия сигналов сканирования, которая должна сканироваться, из двух линий сигналов сканирования, чередуется в расчете на один кадр, и полярность электрического потенциала сигнала, соответствующего идентичному пикселу, инвертируется в расчете на два кадра, или линия сигналов сканирования, которая должна сканироваться, из двух линий сигналов сканирования, чередуется в расчете на два последовательных кадра, и полярность электрического потенциала сигнала, соответствующего идентичному пикселу, инвертируется в расчете на один кадр.

Настоящее жидкокристаллическое дисплейное устройство может конфигурироваться таким образом, что после того, как один из двух пикселных электродов, расположенных в соответствующем пикселе, разряжается, электрический потенциал сигнала записывается в другой из двух пикселных электродов, расположенных в пикселе.

Настоящее жидкокристаллическое дисплейное устройство может конфигурироваться таким образом, что транзистор, подключенный к одному из двух пикселных электродов, расположенных в соответствующем пикселе, отключается в состоянии, в котором электрический потенциал общего электрода подается в два пикселных электрода, предусмотренные в пикселе, и после этого электрический потенциал сигнала записывается в другой из двух пикселных электродов, расположенных в пикселе.

Настоящее жидкокристаллическое дисплейное устройство может конфигурироваться таким образом, что в одном периоде горизонтального сканирования, транзистор, подключенный к одному из двух пикселных электродов, расположенных в пикселе, отключается в состоянии, в котором электрический потенциал общего электрода подается в два пикселных электрода, предусмотренные в пикселе, и после этого электрический потенциал сигнала записывается в другой из двух пикселных электродов, расположенных в пикселе.

Настоящее жидкокристаллическое дисплейное устройство может конфигурироваться таким образом, что жидкокристаллическое дисплейное устройство является обычным черным жидкокристаллическим дисплейным устройством, и после истечения от 1/2 периода вертикального сканирования до 4/5 периода вертикального сканирования после записи электрического потенциала сигнала в один из двух пикселных электродов, расположенных в пикселе, транзисторы, подключенные к пикселным электродам, расположенным в пикселной области, отключаются в состоянии, в котором электрический потенциал общего электрода подается в два пикселных электрода.

Настоящая подложка активной матрицы включает в себя: первую линию сигналов данных; первую-четвертую линии сигналов сканирования; первый-четвертый транзисторы, причем первый транзистор подключается к первой линии сигналов данных и первой линии сигналов сканирования, второй транзистор подключается к первой линии сигналов данных и второй линии сигналов сканирования, третий транзистор подключается к первой линии сигналов данных и третьей линии сигналов сканирования, а четвертый транзистор подключается к первой линии сигналов данных и четвертой линии сигналов сканирования; и первый-четвертый пикселные электроды, причем первый пикселный электрод и второй пикселный электрод располагаются в первой пикселной области, а третий пикселный электрод и четвертый пикселный электрод располагаются во второй пикселной области, размещенной рядом с первой пикселной областью в направлении столбцов, где направление столбцов - это направление, в котором идут первые линии сигналов данных, причем первый пикселный электрод и второй пикселный электрод подключаются друг к другу через конденсатор, и третий пикселный электрод и четвертый пикселный электрод подключаются друг к другу через конденсатор, один из первого транзистора и второго транзистора подключается к первому пикселному электроду, а другой из первого транзистора и второго транзистора подключается к второму пикселному электроду, и один из третьего транзистора и четвертого транзистора подключается к третьему пикселному электроду, а другой из третьего транзистора и четвертого транзистора подключается к четвертому пикселному электроду.

В жидкокристаллическом дисплейном устройстве, которое использует настоящую подложку активной матрицы, первая линия сигналов сканирования выбирается в одном кадре, и вторая линия сигналов сканирования выбирается в другом кадре. Это приводит к тому, что один пикселный электрод, включенный в один субпиксел, подключается к линии сигналов данных (через транзистор) в одном кадре, и приводит к тому, что один пикселный электрод имеет емкостную связь (через транзистор и другой пикселный электрод) с линией сигналов данных в другом кадре. Это дает возможность подачи электрического потенциала сигнала в пикселный электрод с учетом проходного напряжения в кадре, который подключается к линии сигналов данных, тем самым затрудняя приложение постоянного напряжения к жидкокристаллическому слою субпиксела (затрудняя возникновение зависания изображения субпиксела). Кроме того, субпиксел является ярким субпикселом в одном кадре и является темным субпикселом в другом кадре. Следовательно, можно задавать значение интегрирования во времени яркости в каждом субпикселе однородным по сравнению с конфигурацией, в которой субпиксел всегда является ярким субпикселом или всегда является темным субпикселом, тем самым повышая качество отображения.

Настоящая подложка активной матрицы дополнительно может включать в себя: пятую и шестую линии сигналов сканирования; пятый, и шестой транзисторы, причем пятый транзистор подключается к первой линии сигналов данных и пятой линии сигналов сканирования, а шестой транзистор подключается к первой линии сигналов данных и шестой линии сигналов сканирования; и пятый и шестой пикселные электроды, причем пятый пикселный электрод и шестой пикселный электрод предусмотрены в третьей пикселной области, расположенной рядом с первой пикселной областью в направлении столбцов, пятый пикселный электрод и шестой пикселный электрод подключаются друг к другу через конденсатор, причем третий пикселный электрод, четвертый пикселный электрод, первый пикселный электрод, второй пикселный электрод, пятый пикселный электрод и шестой пикселный электрод выравниваются в направлении столбцов в этом порядке, и причем первый пикселный электрод формирует накопительную емкость с четвертой линией сигналов сканирования, а второй пикселный электрод формирует накопительную емкость с пятой линией сигналов сканирования.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что первый пикселный электрод формирует накопительную емкость со второй линией сигналов сканирования, а второй пикселный электрод формирует накопительную емкость с первой линией сигналов сканирования.

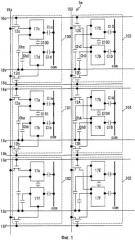

Настоящая подложка активной матрицы дополнительно может включать в себя: вторую линию сигналов данных; седьмой и восьмой транзисторы, причем седьмой транзистор подключается к второй линии сигналов данных и первой линии сигналов сканирования, а восьмой транзистор подключается к второй линии сигналов данных и второй линии сигналов сканирования; и причем седьмой и восьмой пикселные электроды располагаются в четвертой пикселной области, размещенной рядом с первой пикселной областью в направлении строк, седьмой, и восьмой пикселные электроды подключаются друг к другу через конденсатор, причем первый и второй пикселные электроды располагаются рядом друг с другом в направлении столбцов, и седьмой и восьмой пикселные электроды располагаются рядом друг с другом в направлении столбцов, а первый и седьмой пикселные электроды располагаются рядом друг с другом в направлении строк, и второй, и восьмой пикселные электроды располагаются рядом друг с другом в направлении строк, причем первый транзистор подключается к первому пикселному электроду, а второй транзистор подключается к второму пикселному электроду, и седьмой транзистор подключается к восьмому пикселному электроду, а восьмой транзистор подключается к седьмому пикселному электроду.

Настоящая подложка активной матрицы дополнительно может включать в себя: вторую линию сигналов данных; седьмой и восьмой транзисторы, причем седьмой транзистор подключается к второй линии сигналов данных и первой линии сигналов сканирования, а восьмой транзистор подключается к второй линии сигналов данных и второй линии сигналов сканирования; и седьмой, и восьмой пикселные электроды, причем седьмой и восьмой пикселные электроды предусмотрены в четвертой пикселной области, расположенной рядом с первой пикселной областью в направлении строк, седьмой и восьмой пикселные электроды подключаются друг к другу через конденсатор, причем первый и второй пикселные электроды располагаются рядом друг с другом в направлении столбцов, и седьмой, и восьмой пикселные электроды располагаются рядом друг с другом в направлении столбцов, а первый и седьмой пикселные электроды располагаются рядом друг с другом в направлении строк, и второй, и восьмой пикселные электроды располагаются рядом друг с другом в направлении строк, причем первый транзистор подключается к первому пикселному электроду, а второй транзистор подключается к второму пикселному электроду, и седьмой транзистор подключается к седьмому пикселному электроду, а восьмой транзистор подключается к восьмому пикселному электроду.

Настоящая подложка активной матрицы включает в себя: первую и вторую линии сигналов данных; первую и вторую линии сигналов сканирования; транзисторы; и первый-восьмой пикселные электроды, в которой: два из транзисторов подключаются к первой линии сигналов данных и первой линии сигналов сканирования, два из транзисторов подключаются к первой линии сигналов данных и второй линии сигналов сканирования, два из транзисторов подключаются к второй линии сигналов данных и первой линии сигналов сканирования, и два из транзисторов подключаются к второй линии сигналов данных и второй линии сигналов сканирования, первый и второй пикселные электроды расположены в первой пикселной области, третий и четвертый пикселные электроды расположены во второй пикселной области, размещаемой рядом с первой пикселной областью в направлении столбцов, пятый и шестой пикселные электроды расположены в третьей пикселной области, размещаемой рядом с первой пикселной областью в направлении столбцов, и седьмой, и восьмой пикселные электроды расположены в четвертой пикселной области, размещаемой рядом с первой пикселной областью в направлении строк, причем первый пикселный электрод и седьмой пикселный электрод располагаются рядом друг с другом в направлении строк, и второй пикселный электрод, и восьмой пикселный электрод располагаются рядом друг с другом в направлении строк, где направление строк - это направление, в котором идет первая линия сигналов данных, один из двух транзисторов, подключенных к первой линии сигналов данных и первой линии сигналов сканирования, подключаются к первому пикселному электроду, а другой из двух транзисторов, подключенных к первой линии сигналов данных и первой линии сигналов сканирования, подключается к четвертому пикселному электроду, один из двух транзисторов, подключенных к первой линии сигналов данных и второй линии сигналов сканирования, подключается к второму пикселному электроду, а другой из двух транзисторов, подключенных к первой линии сигналов данных и второй линии сигналов сканирования, подключается к пятому пикселному электроду, один из двух транзисторов, подключенных к второй линии сигналов данных и первой линии сигналов сканирования, подключается к восьмому пикселному электроду и одному из двух транзисторов, подключенных к второй линии сигналов данных, и вторая линия сигналов сканирования подключается к седьмому пикселному электроду.

В жидкокристаллическом дисплейном устройстве, которое использует настоящую подложку активной матрицы, первая линия сигналов сканирования и вторая линия сигналов сканирования выбираются в этом порядке в каждом из кадров первого периода, который включает в себя множество последовательных кадров, и вторая линия сигналов сканирования, и первая линия сигналов сканирования выбираются в этом порядке в каждом из кадров во второй период после первого периода, причем этот второй период включает в себя множество последовательных кадров. Это приводит к тому, что один пикселный электрод, включенный в один субпиксел, подключается к линии сигналов данных (через транзистор) в одном кадре, и приводит к тому, что один пикселный электрод имеет емкостную связь с линией сигналов данных (через транзистор и другой пикселный электрод) в другом кадре. Как результат, электрический потенциал сигнала подается в пикселный электрод с учетом проходного напряжения в кадре, который подключается к линии сигналов данных, тем самым затрудняя приложение постоянного напряжения к жидкокристаллическому слою субпиксела (затрудняя возникновение зависания изображения субпиксела). Кроме того, субпиксел является ярким субпикселом в одном кадре, тем не менее, является темным субпикселом в другом кадре. Следовательно, значение интегрирования во времени яркости в каждом субпикселе задано однородным по сравнению с конфигурацией, в которой субпиксел всегда является ярким субпикселом или всегда является темным субпикселом, тем самым повышая качество отображения.

Кроме того, для четырех пикселных электродов, которые включены в два пиксела, расположенные рядом друг с другом в направлении строк, два пикселных электрода, которые расположены по диагонали друг от друга (первый пикселный электрод и восьмой пикселный электрод или второй пикселный электрод и седьмой пикселный электрод), подключаются к одной линии сигналов сканирования. Следовательно, в кадрах, в которых один из двух субпикселов, которые находятся рядом друг с другом в направлении строк, является ярким субпикселом, другой из двух субпикселов является темным субпикселом. Как результат, можно сдерживать неоднородность (например, неоднородность с горизонтальными полосами) и неравномерность (ступенчатость) отображения по сравнению с конфигурацией, в которой яркие субпикселы находятся рядом друг с другом в направлении строк, и темные субпикселы находятся рядом друг с другом в направлении строк.

Настоящая подложка активной матрицы дополнительно может включать в себя провод накопительного конденсатора, при этом провод накопительного конденсатора формирует накопительную емкость с первым пикселным электродом и со вторым пикселным электродом.

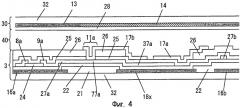

Настоящая подложка активной матрицы может конфигурироваться таким образом, что в случае, если подложка активной матрицы просматривается в плоскости, первый пикселный электрод расположен между первой линией сигналов сканирования и второй линией сигналов сканирования полностью или частично, причем частью первого пикселного электрода является первый пикселный электрод за исключением его краевых секций, а второй пикселный электрод расположен между первой линией сигналов сканирования и второй линией сигналов сканирования полностью или частично, причем частью второго пикселного электрода является второй пикселный электрод за исключением его краевых секций.

Настоящая подложка активной матрицы может конфигурироваться таким образом, что область, в которой токопроводящий электрод первого транзистора и токопроводящая часть, электрически подключенная к токопроводящему электроду первого транзистора, перекрывают первую линию сигналов сканирования, имеет размер, идентичный размеру области, в которой токопроводящий электрод второго транзистора и токопроводящая часть, электрически подключенная к токопроводящему электроду второго транзистора, перекрывают вторую линию сигналов сканирования.

Настоящая подложка активной матрицы может конфигурироваться так, что она дополнительно включает в себя электрод накопительного конденсатора, сформированный в слое, идентичном слою токопроводящих электродов первого и второго транзисторов, причем электрод накопительного конденсатора электрически подключается к одному из первого и второго пикселных электродов и перекрывает провод накопительного конденсатора таким образом, что изолирующий слой затвора размещается между электродами накопительного конденсатора и проводом накопительного конденсатора.

Настоящая подложка активной матрицы также может конфигурироваться так, что она дополнительно включает в себя электрод разделительного конденсатора, сформированный в слое, идентичном слою токопроводящих электродов первого и второго транзисторов, причем электрод разделительного конденсатора электрически подключается к одному из первого и второго пикселных электродов и перекрывается посредством другого из первого и второго пикселных электродов таким образом, что межслойный изолирующий слой размещается между электродом разделительного конденсатора и другим из первого и второго пикселных электродов.

Настоящая подложка активной матрицы может конфигурироваться так, что она дополнительно включает в себя электрод разделительного конденсатора, сформированный в слое, идентичном слою токопроводящих электродов первого и второго транзисторов, причем электрод разделительного конденсатора электрически подключается к одному из первого и второго пикселных электродов и перекрывается посредством другого из первого и второго пикселных электродов таким образом, что межслойный изолирующий слой размещается между электродом разделительного конденсатора и другим из первого и второго пикселных электродов, и дополнительно перекрывается посредством провода накопительного конденсатора таким образом, что изолирующий слой затвора размещается между электродом разделительного конденсатора и проводом накопительного конденсатора.

Настоящая подложка активной матрицы может конфигурироваться так, что она дополнительно включает в себя электрод накопительного конденсатора, сформированный в слое, идентичном слою токопроводящих электродов первого и второго транзисторов, причем электрод накопительного конденсатора электрически подключается к одному из первого и второго пикселных электродов и перекрывает любую из линий сигналов сканирования таким образом, что изолирующий слой затвора размещается между электродами накопительного конденсатора и любой из линий сигналов сканирования.

Настоящая подложка активной матрицы может конфигурироваться так, что она дополнительно включает в себя: первый электрод разделительного конденсатора, перекрываемый посредством второго пикселного электрода таким образом, что межслойный изолирующий слой размещается между первым электродом разделительного конденсатора и вторым пикселным электродом; и второй электрод разделительного конденсатора, перекрываемый посредством первого пикселного электрода таким образом, что межслойный изолирующий слой размещается между вторым электродом разделительного конденсатора и первым пикселным электродом, в которой: первый электрод разделительного конденсатора подключается к первому отводному проводу в идентичном слое, причем первый отводной провод выдается из токопроводящего электрода первого транзистора, первый отводной провод и первый пикселный электрод подключаются друг к другу через контактное окно, и второй электрод разделительного конденсатора подключается к второму отводному проводу в идентичном слое, причем второй отводной провод выдается из токопроводящего электрода второго транзистора, второй отводной провод и второй пикселный электрод подключаются друг к другу через контактное окно. В этом случае, когда подложка активной матрицы просматривается в плоскости, первый пикселный электрод расположен между первой линией сигналов сканирования и второй линией сигналов сканирования полностью или частично, причем частью первого пикселного электрода является первый пикселный электрод за исключением его краевых секций, а второй пикселный электрод расположен между первой линией сигналов сканирования и второй линией сигналов сканирования полностью или частично, причем частью второго пикселного электрода является второй пикселный электрод за исключением его краевых секций, и первый, и второй пикселные электроды, первый и второй электроды разделительного конденсатора, первый и второй отводные провода предусмотрены таким образом, что плоская форма и плоская конфигурация первого и второго пикселных электродов, первого и второго электродов разделительного конденсатора, первого и второго отводных проводов при просмотре со стороны первой линии сигналов сканирования является идентичной форме и конфигурации при просмотре со стороны второй линии сигналов сканирования.

Настоящая подложка активной матрицы может конфигурироваться так, что она дополнительно включает в себя первый электрод разделительного конденсатора, перекрываемый посредством второго пикселного электрода таким образом, что межслойный изолирующий слой размещается между первым электродом разделительного конденсатора и вторым пикселным электродом; и второй электрод разделительного конденсатора, перекрываемый посредством первого пикселного электрода таким образом, что межслойный изолирующий слой размещается между вторым электродом разделительного конденсатора и первым пикселным электродом, в которой: первый пикселный электрод подключается к токопроводящему электроду первого транзистора через контактное окно, и первый пикселный электрод подключается к первому электроду разделительного конденсатора через контактное окно, и второй пикселный электрод подключается к токопроводящему электроду второго транзистора через контактное окно, и второй пикселный электрод подключается к второму электроду разделительного конденсатора через контактное окно. В этом случае, когда подложка активной матрицы просматривается в плоскости, первый пикселный электрод расположен между первой линией сигналов сканирования и второй линией сигналов сканирования полностью или частично, причем частью первого пикселного электрода является первый пикселный электрод за исключением его краевых секций, а второй пикселный электрод расположен между первой линией сигналов сканирования и второй линией сигналов