Устройство для контроля и резервирования информационной системы

Иллюстрации

Показать всеИзобретение относится к автоматике и вычислительной технике и может быть использовано в высоконадежных вычислительных и управляющих системах различного назначения. Технический результат - повышение надежности функционирования. Устройство для контроля и резервирования информационной системы содержит три резервируемых блока, семь блоков элементов И, блок элементов ИЛИ, выходной регистр, три блока сравнения, блок реконфигурации, три триггера, блок определения сбоя, выходы устройства "Норма", "Снижение надежности" и "Одноканальная конфигурация", соединенные между собой так, как указано в материалах заявки. Устройство позволяет обеспечить проверку на сбой при появлении нескольких отказов. Обычно проверку на сбой можно осуществлять до трех или пяти раз. Если окажется, что после этого сбой повторяется, то считается, что устройство неисправно. 2 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в высоконадежных вычислительных и управляющих системах различного назначения.

Известно устройство для контроля и резервирования информационно-измерительной системы [SU, 1578723 А1, класс G06F 11/20. 1990.07.15.], содержащее выходной регистр, выход которого является информационным выходом устройства, регистр отказов, первый блок сравнения, коммутатор, блок синхронизации, первый и второй дешифраторы, первый элемент ИЛИ и регистр точного канала, информационный вход которого является первым информационным входом устройства, а вход запуска блока синхронизации соединен с одноименным входом устройства, блок формирования сигналов отказа, регистры первого-третьего грубых каналов, второй-шестой блоки сравнения, второй-четвертый элементы ИЛИ, блок усреднения и генератор констант, первый информационный выход которого соединен с входами уставки первого-третьего блоков сравнения, а второй информационный выход - с входами уставки четвертого-шестого блоков сравнения, подключенных выходами к соответствующим информационным входам второго дешифратора, вход блокировки которого соединен с выходом четвертого элемента ИЛИ, выход регистра точного канала подключен к первым информационным входам коммутатора и первого-третьего блоков сравнения, выход регистра первого грубого канала соединен с вторым информационным входом первого блока сравнения и с первыми информационными входами четвертого и пятого блоков сравнения и блока усреднения, выход регистра второго грубого канала соединен с вторыми информационными входами второго и четвертого блоков сравнения и блока усреднения и с первым информационным входом шестого блока сравнения. Выход регистра третьего грубого канала соединен с вторыми информационными входами третьего, пятого и шестого блоков сравнения и с третьим информационным входом блока усреднения, выходом подключенного к второму информационному входу коммутатора, выход которого соединен с информационным входом выходного регистра, выходы первого-третьего блоков сравнения подключены к первым входам соответственно первого-третьего элементов ИЛИ, соединенных выходами с соответствующими входами первого дешифратора, группа выходов младших разрядов которого подключена к первой группе информационных входов блока формирования сигналов отказов, а выход старшего разряда - к одному из информационных входов группы регистра-отказов и к первому входу четвертого элемента ИЛИ, группа выходов соответствующих младших разрядов второго дешифратора соединена с второй группой информационных входов блока формирования сигналов отказов, соединенного выходами с соответствующими информационными входами группы регистра отказов, первый-третий выходы которого соединены с вторыми входами первого-третьего элементов ИЛИ и с соответствующими управляющими входами блока усреднения, а четвертый выход - с третьими входами первого-третьего элементов ИЛИ, с вторым входом четвертого элемента ИЛИ, с входом блокировки первого дешифратора и с входом управления коммутатора, первый выход блока синхронизации подключен к синхровходам выходного регистра, регистра точного канала и регистров первого-третьего грубых каналов, второй выход - к входам синхронизации регистра отказов, а вход останова - к выходу старшего разряда второго дешифратора и к контрольному выходу устройства, причем информационные входы регистров первого-третьего грубых каналов соединены с вторым-четвертым информационными входами устройства соответственно.

Недостатком этого устройства является низкая надежность, обусловленная отказом функционирования всей системы при появлении второго отказа и невозможностью автоматического проведения процесса восстановления или перестройки структуры (реконфигурации).

Наиболее близким к заявляемому устройству является устройство для контроля и резервирования информационной системы [RU №2058679 С1, класс Н05К 10/00, 1996.04.20.] содержащее регистр отказов, три блока сравнения, подключенных выходами равенства к соответствующим входам дешифратора отказа, элемент ИЛИ и выходной регистр, группа выходов которого является информационным выходом устройства, первые группы информационных входов первого и второго блоков сравнения объединены и являются первым информационным входом устройства, служащим для получения выхода первого резервируемого блока, первая группа информационных входов третьего блока сравнения и вторая группа информационных входов первого блока сравнения объединены и являются вторым информационным входом устройства, служащим для подключения выхода второго резервируемого блока, вторые группы информационных входов второго и третьего блоков сравнения объединены и являются третьим информационным входом устройства, служащим для подключения выхода третьего резервируемого блока, таймерный блок, четыре блока элементов И, блок элементов ИЛИ, элемент И, мажоритарный элемент и Т-триггер отказа, подключенный входом к первому выходу дешифратора отказа, соединенного вторым, третьим и четвертым выходами с соответствующими информационными входами регистра отказов, подключенного первым, вторым и третьим разрядными входами к соответствующим входам элемента ИЛИ и первым входам соответственно первого, второго и третьего блоков элементов И, группы входов которых объединены соответственно с первой, второй и третьей группами информационных входов мажоритарного элемента и являются соответственно первым, вторым и третьим информационными входами устройства, группа выходов мажоритарного элемента соединена с группой входов четвертого блока элементов И, инверсный вход которого подключен к вторым входам первого, второго и третьего блоков элементов И, управляющему входу таймерного блока, прямому выходу Т-триггера и является выходом "Отсутствие резерва" устройства, группы выходов с первого по четвертый блоков элементов И соединены с соответствующими группами входов блока элемента ИЛИ, подключенного группой выходов к группе информационных входов выходного регистра, связанного синхронизирующим входом с выходом элемента И, подключенного первым инверсным входом к первому управляющему выходу таймерного блока, соединенного тактовым выходом с С-входом Т-триггера и синхронизирующим входом регистра отказов, а вторым управляющим выходом с третьими входами первого, второго и третьего блоков элементов И, тактовый выход таймерного блока является управляющим выходом устройства, служащим для подключения управляющих входов первого, второго и третьего резервируемых блоков, прямой вход элемента И и тактовый вход таймерного блока являются соответственно первым и вторым тактовыми входами устройства, первый и второй сигнальные выходы таймерного блока являются соответственно первым и вторым сигнальными выходами останова устройства, третий сигнальный выход таймерного блока является выходом "Одноканальная конфигурация" устройства, прямой выход элемента ИЛИ соединен с инверсным управляющим входом регистра отказов и является сигнальным выходом "Снижение надежности" устройства, инверсный выход элемента ИЛИ является выходом "Норма" устройства.

Недостатком этого устройства является низкая надежность функционирования, обусловленная отсутствием проверки на сбои при появлении второго отказа и сложностью исполнения схемы устройства.

Техническим результатом является повышение надежности функционирования, обусловленная введением проверки на сбои при появлении второго отказа и сокращение схемы устройства.

Технический результат достигается тем, что в устройство для контроля и резервирования информационной системы, содержащее три резервируемых блока, соединенные с информационным входом устройства, два блока элементов И первые входы которых соединены с выходами соответственно первого и второго резервируемых блока, блок элементов ИЛИ, входы которого соединены с выходами блоков элементов И, триггер, выходной регистр, выход которого соединен с информационным выходом устройства, три блока сравнения, выходы устройства "Норма", "Снижение надежности" и "Одноканальная конфигурация" и элемент И, первый вход которого соединен с тактовым входом устройства, отличающееся тем, что в него введены четыре блока элементов И, два триггера, блок определения сбоя и блок реконфигурации, с первого по третий входы которого соединены с выходами соответствующих блоков сравнения, первый выход блок реконфигурации соединен со вторыми входами первого блока элементов И, а второй выход соединен со вторыми входами второго блока элементов И, третий выход блока реконфигурации соединен с единичными входом первого триггера, нулевой вход которого соединен с единичным входом второго триггера и четвертым выходом блока реконфигурации, пятый выход которого соединен с нулевым входом второго триггера и единичным входом третьего триггера, нулевой вход которого соединен с шестым выходом блока реконфигурации и вторым входом блока определения сбоя, первый вход которого соединен с пятым выходом блока реконфигурации, первый выход блока определения сбоя соединен с вторым входом элемента И, второй выход блока определения сбоя соединен с вторыми входами третьего блока элементов И, первые входы которого соединены с выходами блока элементов ИЛИ, выходы третьего блока элементов И соединены с входами выходного регистра, выход первого триггера соединен с выходом "Норма" устройства, выход второго триггера соединен с выходом "Снижение надежности" устройства, выход третьего триггера соединен с выходом "Одноканальная конфигурация" устройства, выходы первого, второго и третьего резервируемых блока соединены каждый отдельно с первыми входами соответственно четвертого, пятого и шестого блоков элементов И, вторые входы которых объединены и соединены с выходом элемента И, выход четвертого блока элементов И соединен с первыми входами первого и третьего блоков сравнения, выход пятого блока элементов И соединен с вторыми входами первого и второго блоков сравнения, выход шестого блока элементов И соединен с первым входом второго блока сравнения и вторым входом третьего блока сравнения, выход элемента И соединен с объединенными тактовыми входами резервируемых блоков, причем блок определения сбоя содержит счетчик, дешифратор и инвертор, выход которого соединен с первым выходом блока, второй вход которого соединен с первым выходом дешифратора, второй выход которого соединен с входом инвертора, входы дешифратора соединены с выходами счетчика, счетный вход которого соединен с первым входом блока, второй вход которого соединен с входом установки в нулевое состояние счетчика, причем блок реконфигурации содержит четыре инвертора, четыре элемента И и четыре элемента ИЛИ, первый вход блока соединен с объединенными первыми входами первого элемента ИЛИ, первого, второго и четвертого элементов И и входом третьего инвертора, выход которого соединен с первым входом третьего элемента И, второй вход блока соединен с объединенными вторыми входами первого элемента ИЛИ, второго, третьего и четвертого элементов И и входом первого инвертора, выход которого соединен с вторым входом первого элемента И, третий вход блока соединен с объединенными третьими входами первого элемента ИЛИ, первого, третьего и четвертого элементов И и входом второго инвертора, выход которого соединен с третьим входом второго элемента И, выход первого элемента ИЛИ соединен с входом четвертого инвертора, выход которого соединен с третьим выходом блока и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и вторым входом четвертого элемента ИЛИ, третий вход которого соединен с выходом третьего элемента И и третьим входом второго элемента ИЛИ, выход которого соединен с первым выходом блока и первым входом третьего элемента ИЛИ, второй вход которого соединен с со вторым выходом блока, выходом первого элементов И и первым входом четвертого элемента ИЛИ, выход которого соединен с четвертым выходом блока, пятый выход которого соединен с выходом четвертого элементов И, выход третьего элемента ИЛИ соединен с шестым выходом блока.

Введение указанных дополнительных элементов и последовательности их соединения позволяет повысить надежность функционирования, обусловленная введением проверки на сбои при появлении второго отказа и сократить схему устройства.

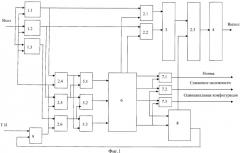

На фиг.1 представлена функциональная схема устройства.

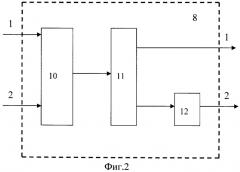

На фиг.2 представлена функциональная схема блока определения сбоя.

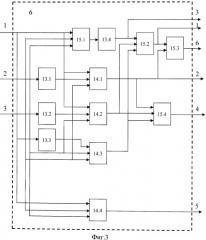

На фиг.3 представлена функциональная схема блока реконфигурации.

Устройство содержит (фиг.1) три резервируемых блока 1, шесть блоков элементов И 2, блок элементов ИЛИ 3, выходной регистр 4, три блока сравнения 5, блок реконфигурации 6, три триггера 7, блок определения сбоя 8 и элемент И.

Блок определения сбоя (фиг.2) содержит счетчик 10, дешифратор 11 и инвертор 12.

Блок реконфигурации (фиг.3) содержит четыре инвертора 13, четыре элемента И 14 и четыре элемента ИЛИ 15.

Устройство для контроля и резервирования информационной системы содержит три резервируемых блока 1.1-1.3, соединенные с информационным входом устройства, шесть блоков элементов И 2.1-2.6, первые входы первых двух блоков элементов И 2.1-2.2 соединены с выходами соответственно первого и второго резервируемых блока 1.1-1.2, блок элементов ИЛИ 3, входы которого соединены с выходами первых двух блоков элементов И 2.1-2.2, выходной регистр 4, выход которого соединен с информационным выходом устройства, три блока сравнения 5.1-5.3, блок реконфигурации 6, три триггера 7.1-7.3, блок определения сбоя 8, выходы устройства "Норма", "Снижение надежности" и "Одноканальная конфигурация" и элемент И 9, первый вход которого соединен с тактовым входом устройства, с первого по третий входы блока реконфигурации 6 соединены с выходами соответствующих блоков сравнения 5.1-5.3, первый выход блок реконфигурации 6 соединен со вторыми входами первого блока элементов И 2.1. а второй выход соединен со вторыми входами второго блока элементов И 2.2. третий выход блока реконфигурации 6 соединен с единичными входом первого 7.1 триггера, нулевой вход которого соединен с единичным входом второго 7.2 триггера и четвертым выходом блока реконфигурации 6, пятый выход которого соединен с нулевым входом второго 7.2 триггера и единичным входом третьего 7.3 триггера, нулевой вход которого соединен с шестым выходом блока реконфигурации 6 и вторым входом блока определения сбоя 8, первый вход которого соединен с пятым выходом блока реконфигурации 6, первый выход блока определения сбоя 8 соединен с вторым входом элемента И 9, второй выход блока определения сбоя 8 соединен с вторыми входами третьего блока элементов И 2.3, первые входы которого соединены с выходами блока элементов ИЛИ 3, выходы третьего блока элементов И 2.3 соединены с входами выходного регистра, выход первого триггера 7.1 соединен с выходом "Норма" устройства, выход второго триггера 7.2 соединен с выходом "Снижение надежности" устройства, выход третьего триггера 7.3 соединен с выходом "Одноканальная конфигурация" устройства, выходы первого 1.1, второго 1.2 и третьего 1.3 резервируемых блока соединены каждый отдельно с первыми входами соответственно четвертого 2.4, пятого 2.5 и шестого 2.6 блоков элементов И, вторые входы которых объединены и соединены с выходом элемента И 9, выход четвертого блока элементов И 2.4 соединен с первыми входами первого 5.1 и третьего 5.3 блоков сравнения, выход пятого блока элементов И 2.5 соединен с вторыми входами первого 5.1 и второго 5.2 блоков сравнения, выход шестого блока элементов И 2.6 соединен с первым входом второго блока сравнения 5.2 и вторым входом третьего блока сравнения 5.3, выход элемента И соединен с объединенными тактовыми входами резервируемых блоков, причем блок определения сбоя 8 содержит счетчик 10, дешифратор 11 и инвертор 12, выход которого соединен с первым выходом блока 8, второй вход которого соединен с первым выходом дешифратора 11, второй выход которого соединен с входом инвертора 12, входы дешифратора 11 соединены с выходами счетчика 10, счетный вход которого соединен с первым входом блока 8, второй вход которого соединен с входом установки в нулевое состояние счетчика 10, причем блок реконфигурации 6 содержит четыре инвертора 13.1-13.4, четыре элемента И 14.1-14.4 и четыре элемента ИЛИ 15.1-15.4, первый вход блока 6 соединен с объединенными первыми входами первого элемента ИЛИ 15.1, первого 14.1, второго 14.2 и четвертого 14.4 элементов И и входом третьего инвертора 13.3, выход которого соединен с первым входом третьего элемента И 14.3, второй вход блока 6 соединен с объединенными вторыми входами первого элемента ИЛИ 15.1, второго 14.2, третьего 14.3 и четвертого 14.4 элементов И и входом первого инвертора 13.1, выход которого соединен с вторым входом первого элемента И 14.1, третий вход блока 6 соединен с объединенными третьими входами первого элемента ИЛИ 15.1, первого 14.1, третьего 14.3 и четвертого 14.4 элементов И и входом второго инвертора 13.2, выход которого соединен с третьим входом второго элемента И 14.2, выход первого элемента ИЛИ 15.1 соединен с входом четвертого инвертора 13.4, выход которого соединен с третьим выходом блока 6 и первым входом второго элемента ИЛИ 15.2, второй вход которого соединен с выходом второго элемента И 14.2 и вторым входом четвертого элемента ИЛИ 15.4, третий вход которого соединен с выходом третьего элемента И 14.3 и третьим входом второго элемента ИЛИ 15.2, выход которого соединен с первым выходом блока 6 и первым входом третьего элемента ИЛИ 15.3, второй вход которого соединен с со вторым выходом блока 6, выходом первого элементов И 14.1 и первым входом четвертого элемента ИЛИ 15.4, выход которого соединен с четвертым выходом блока 6, пятый выход которого соединен с выходом четвертого элементов И 14.4, выход третьего элемента ИЛИ 15.3 соединен с шестым выходом блока 6.

Резервированное устройство работает следующим образом (фиг.1-фиг.3). В исходном состоянии все элементы памяти обнулены. Цепи установки в ноль элементов памяти (не показаны). Также не показаны элементы задержки сигналов, необходимые для обеспечении синхронизации работы устройства, параметры которых могут подбираться для каждого конкретного случая исполнении устройства. На информационный вход устройства подаются исходные данные для обработки в резервируемых блоках 5. На тактовый вход подаются синхроимпульсы. Величина продолжительности синхроимпульсов выбирается из расчета обеспечения переходных процессов при взаимодействии элементов схемы. При поступлении тактовых импульсов резервируемые блоки 1.1-1.3 производят обработку информации, поступающей на информационный вход. Обработанная информация с выходов первого 1.1, второго 1.2 и третьего 1.3 резервируемых блоков поступают на первые входы соответственно с четвертого по шестой (2.4-2.6) блока элементов И. По сигналу с выхода элемента И 9 обработанная информация поступает на входы блоков сравнения 5.1-5.3, которые производят сравнение результатов между собой (первый и второй, первый и третий, второй и третий). При этом возможны следующие варианты.

При первом варианте предполагается, что все три резервируемых блока 1.1-1.3 исправны. В этом случае с выходов всех трех блоков сравнения 5.1-5.3 будут выдаваться нулевые сигналы, которые поступают на соответствующие входы блока реконфигурации 6 (фиг.3). На всех входах первого элемента ИЛИ 15.1 блока будут нулевые сигналы. На выходе первого элемента ИЛИ 15.1 будет также нулевой сигнал, который поступает на вход четвертого инвертора 13.4. С выхода четвертого инвертора 13.4 уже единичный сигнал поступает на третий выход блока реконфигурации 6 и далее - на единичный вход первого триггера 7.1 (фиг.1), а с его выхода поступает на выход устройства как сигнал "Норма". Этот сигнал показывает, что все три резервируемых блока 1.1-1.3 исправны. Кроме того, единичный сигнал с выхода четвертого инвертора 13.4 (фиг.3) выдается на первый выход блока 6, и далее на вторые первого блока элементов И 2.1 (фиг.1). На первые входы первого блока элементов И 2.1 поступает обработанная информация с выхода первого резервируемого блока 1.1. Эта обработанная информация через открытые элементы И первого блока элементов И 2.1 поступает на входы блока элементов ИЛИ 3, а с их выходов - на первые входы третьего блока элементов И 2.3. Так как в начале работы все элементы памяти установлены в нулевое состояние, то и счетчик 10 блока определения сбоя 8 (фиг.2) находится в нулевом состоянии. Нулевые сигналы с выхода счетчика 10 подаются на входы дешифратора 11. В этом случае с первого выхода дешифратора на второй выход блока выдается единичный сигнал. По этому сигналу, поступающему на вторые входы третьего блока элементов И 2.3 (фиг.1), обработанная информация поступает на вход выходного регистра 4 и далее на выход устройства.

Так как все три резервируемых блока 1.1-1.3 исправны, то возможна передача обработанной информации на выход устройства с любого из резервируемых блоков 1. В данном варианте исполнения принято, что первый блок 1.1 является основным, а второй 1.2 и третий 1.3 - резервными.

При втором варианте предполагается, что первый резервируемый блок 1.1 неисправен. В этом случае с выходов первого 5.1 и третьего 5.3 блоков сравнения будут выдаваться единичные сигналы, а с выхода второго 5.2 блока сравнения будет выдаваться нулевой сигнал. Эти сигналы поступают на соответствующие входы блока реконфигурации 6 (фиг. 3). На первом и третьем входах первого элемента ИЛИ 15.1 блока будут поступать единичные сигналы. На выходе первого элемента ИЛИ 15.1 будет также единичный сигнал, который поступает на вход четвертого инвертора 13.4. С выхода четвертого инвертора 13.4 будет выдаваться нулевой сигнал. Единичные сигналы с первого и третьего входов блока поступают на первый и третий входы первого элемента И 14.1, а на его второй вход через первый инвертор 13.1 со второго входа блока поступает единичный сигнал. С выхода первого элемента И 14.1 единичный сигнал поступает на второй выход блока, а через третий 15.3 и четвертый 15.4 элементы ИЛИ - соответственно на шестой и четвертый выходы блока. Единичный сигнал со второго выхода блока реконфигурации 6 (фиг.1) поступает на вторые входы второго блока элементов И 2.2. На первые входы второго блока элементов И 2.2 поступает обработанная информация с выхода второго резервируемого блока 1.2. Эта обработанная информация через открытые элементы И первого блока элементов И 2.1 поступает на входы блока элементов ИЛИ 3, а с их выходов - на первые входы третьего блока элементов И 2.3. Так как на первый вход блока определения сбоя 8 (фиг.2) сигнал с пятого выхода блока реконфигурации 6 (фиг.1) не поступает, то счетчик 10 блока определения сбоя 8 (фиг. 2) находится в нулевом состоянии, с первого выхода дешифратора 11 на второй выход блока выдается единичный сигнал. По этому сигналу, поступающему на вторые входы третьего блока элементов И 2.3 (фиг.1), обработанная информация поступает на вход выходного регистра 4 и далее на выход устройства.

Кроме того, с выхода элемента И 14.1 единичный сигнал через четвертый элемент ИЛИ 15.4 блока реконфигурации 6 (фиг.3) поступает на четвертый выход блока реконфигурации 6 и далее на нулевой вход первого триггера 7.1 (фиг.1) и на единичный вход второго триггера 7.2. При этом сигнал "Норма" снимается, устанавливается сигнал "Снижение надежности". Этот сигнал показывает, что один из резервируемых блоков неисправен.

При третьем варианте предполагается, что второй резервируемый блок 1.2 неисправен. В этом случае с выходов первого 5.1 и второго 5.2 блоков сравнения будут выдаваться единичные сигналы, а с выхода третьего 5.3 блока сравнения будет выдаваться нулевой сигнал. Эти сигналы поступают на соответствующие входы блока реконфигурации 6 (фиг.3). На первом и втором входах первого элемента ИЛИ 15.1 блока будут единичные сигналы. На выходе первого элемента ИЛИ 15.1 будет также единичный сигнал, который поступает на вход четвертого инвертора 13.4. С выхода четвертого инвертора 13.4 будет выдаваться нулевой сигнал. Единичные сигналы с первого и второго входов блока поступают на первый и третий входы второго элемента И 14.2, а на его второй вход через второй инвертор 13.2 с третьего входа блока поступает единичный сигнал. С выхода второго элемента И 14.2 единичный сигнал поступает на второй вход второго элемента ИЛИ 15.2 и далее с его выхода - на первый выход блока. Кроме того, сигнал с выхода второго элемента ИЛИ 15.2 через третий 15.3 и четвертый 15.4 элементы ИЛИ поступает соответственно на шестой и четвертый выходы блока.

Единичный сигнал со первого выхода блока реконфигурации 6 (фиг.1) поступает на вторые входы первого блока элементов И 2.1, на первые входы которого поступает обработанная информация с выхода первого резервируемого блока 1.1. Эта обработанная информация через открытые элементы И первого блока элементов И 2.1 поступает на входы блока элементов ИЛИ 3, а с их выходов - на первые входы третьего блока элементов И 2.3. Так как на первый вход блока определения сбоя 8 (фиг.2) сигнал с пятого выхода блока реконфигурации 6 (фиг.1) не поступает, то счетчик 10 блока определения сбоя 8 (фиг.2) находится в нулевом состоянии. С первого выхода дешифратора 11 на второй выход блока выдается единичный сигнал. По этому сигналу, поступающему на вторые входы третьего блока элементов И 2.3 (фиг.1), обработанная информация поступает на вход выходного регистра 4 и далее на выход устройства.

С четвертого выхода блока реконфигурации 6 сигнал поступает на нулевой вход первого триггера 7.1 (фиг.1) и на единичный вход второго триггера 7.2. При этом сигнал "Норма" снимается, устанавливается сигнал "Снижение надежности". Этот сигнал показывает, что один из резервируемых блоков неисправен.

Если оказывается, что неисправен третий резервируемый блок 1.3, то устройство будет работать аналогично, как и при третьем варианте, за исключением того, что в блоке реконфигурации 6 (фиг.3) будут использоваться третий инвертор 13.3 и третий элемент И 14.3.

Если во время работы устройства откажут один за другим два резервируемых блока, то выходах всех трех блоков 5.1-5.3 сравнения формируются три единичных сигнала, которые фиксируют факт второго отказа. Это не позволяет определить номер отказавшего или исправного резервируемого блока. В этом случае на всех трех входах блока реконфигурации 6 (фиг.3) будут единичные сигналы, которые поступают на входы четвертого элемента И 14.4 и, с его выхода, - на пятый выход блока. С пятого выхода блока реконфигурации 6 сигнал поступает на нулевой вход второго триггера 7.2 (фиг.1) и на единичный вход третьего триггера 7.3. При этом сигнал "Норма" и сигнал "Снижение надежности" снимается, устанавливается сигнал "Одноканальная конфигурация". Этот сигнал показывает, что два резервируемых блока неисправны.

Однако в этом случае возможно произошел не отказ, а сбой в работе одного или двух резервируемых блока, работа которого может через определенное время восстановиться. И, если это так, то необязательно останавливать устройство, как предусмотрено в [SU, 1578723 А1, класс G06F 11/20. 1990.07.15], а произвести проверку на наличие сбоя. Для этого сигнал с пятого выхода блока реконфигурации 6 (фиг.1) поступает на первый вход блока определения сбоя 8 (фиг.2) и устанавливает значение счетчика равное единице. С первого выхода дешифратора 11 на второй выход блока выдается нулевой сигнал. Этот сигнал запрещает передачу обработанной информации на вход выходного регистра 4 и далее на выход устройства, так как она может оказаться неверной, но работа устройства не останавливается.

Если окажется сбой, то по одному из вышеизложенных вариантов на выходах блока реконфигурации 6 могут быть выданы единичные сигналы на первый или второй выходы, на третий или четвертый выходы и шестой выход, а с пятого выхода будет выдан нулевой сигнал. Это будет означать, что произошел сбой, устройство работает по варианту, когда неисправен только какой-либо один резервируемый блок. В этом случае единичный сигнал с шестого выхода блока реконфигурации 6 поступает на второй вход блока определения сбоя 8 (фиг.2) и установит счетчик 10 в нулевое состояние. С первого выхода дешифратора 11 на второй выход блока будет выдан единичный сигнал, разрешающий выдавать на выход устройства обрабатываемую информацию.

Если же окажется, что два резервируемых блока неисправны (сбой отсутствует), то в каждом цикле работы устройства с пятого выхода блока реконфигурации 6 на второй вход блока определения сбоя 8 (фиг.1, фиг.2) будет выдаваться единичный сигнал, по этому сигналу к значению счетчика 10 будет добавляться единица. Со второго выхода блока определения сбоя 8 будет выдаваться нулевой сигнал, запрещая выдачу информации на выход устройства.

Обычно практика показывает, что проверку на сбой можно осуществлять до трех или пяти раз. И если после этого сбой повторяется, то считается, что устройство неисправно.

В данном устройстве счетчик 10 считает до трех. Если значение счетчика 10 окажется равным трем, то со второго выхода другого дешифратора 11 блока определения сбоя 8 будет выдан единичный сигнал, который поступает на вход инвертора 12. С выхода инвертора 12 нулевой сигнал будет выдаваться на первый выход блока определения сбоя 8 и далее на второй вход элемента И 9 (фиг.1), останавливая работу устройства для проведения ремонта.

Таким образом, устройство позволяет обеспечить повышение надежности функционирования, обусловленное введением проверки на сбои при появлении второго отказа и сокращение схемы устройства.

1. Устройство для контроля и резервирования информационной системы, содержащее три резервируемых блока, соединенные с информационным входом устройства, два блока элементов И, первые входы которых соединены с выходами соответственно первого и второго резервируемых блока, блок элементов ИЛИ, входы которого соединены с выходами блоков элементов И, триггер, выходной регистр, выход которого соединен с информационным выходом устройства, три блока сравнения, выходы устройства "Норма", "Снижение надежности" и "Одноканальная конфигурация" и элемент И, первый вход которого соединен с тактовым входом устройства, отличающееся тем, что в него введены четыре блока элементов И, два триггера, блок определения сбоя и блок реконфигурации, с первого по третий входы которого соединены с выходами соответствующих блоков сравнения, первый выход блока реконфигурации соединен со вторыми входами первого блока элементов И, а второй выход соединен со вторыми входами второго блока элементов И, третий выход блока реконфигурации соединен с единичными входом первого триггера, нулевой вход которого соединен с единичным входом второго триггера и четвертым выходом блока реконфигурации, пятый выход которого соединен с нулевым входом второго триггера и единичным входом третьего триггера, нулевой вход которого соединен с шестым выходом блока реконфигурации и вторым входом блока определения сбоя, первый вход которого соединен с пятым выходом блока реконфигурации, первый выход блока определения сбоя соединен с вторым входом элемента И, второй выход блока определения сбоя соединен с вторыми входами третьего блока элементов И, первые входы которого соединены с выходами блока элементов ИЛИ, выходы третьего блока элементов И соединены с входами выходного регистра, выход первого триггера соединен с выходом "Норма" устройства, выход второго триггера соединен с выходом "Снижение надежности" устройства, выход третьего триггера соединен с выходом "Одноканальная конфигурация" устройства, выходы первого, второго и третьего резервируемых блоков соединены каждый отдельно с первыми входами соответственно четвертого, пятого и шестого блоков элементов И, вторые входы которых объединены и соединены с выходом элемента И, выход четвертого блока элементов И соединен с первыми входами первого и третьего блоков сравнения, выход пятого блока элементов И соединен с вторыми входами первого и второго блоков сравнения, выход шестого блока элементов И соединен с первым входом второго блока сравнения и вторым входом третьего блока сравнения, выход элемента И соединен с объединенными тактовыми входами резервируемых блоков.

2. Устройство по п.1, отличающееся тем, что блок определения сбоя содержит счетчик, дешифратор и инвертор, выход которого соединен с первым выходом блока, второй вход которого соединен с первым выходом дешифратора, второй выход которого соединен с входом инвертора, входы дешифратора соединены с выходами счетчика, счетный вход которого соединен с первым входом блока, второй вход которого соединен с входом установки в нулевое состояние счетчика.

3. Устройство по п.1, отличающееся тем, что блок реконфигурации содержит четыре инвертора, четыре элемента И и четыре элемента ИЛИ, первый вход блока соединен с объединенными первыми входами первого элемента ИЛИ, первого, второго и четвертого элементов И и входом третьего инвертора, выход которого соединен с первым входом третьего элемента И, второй вход блока соединен с объединенными вторыми входами первого элемента ИЛИ, второго, третьего и четвертого элементов И и входом первого инвертора, выход которого соединен с вторым входом первого элемента И, третий вход блока соединен с объединенными третьими входами первого элемента ИЛИ, первого, третьего и четвертого элементов И и входом второго инвертора, выход которого соединен с третьим входом второго элемента И, выход первого элемента ИЛИ соединен с входом четвертого инвертора, выход которого соединен с третьим выходом блока и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и вторым входом четвертого элемента ИЛИ, третий вход которого соединен с выходом третьего элемента И и третьим входом второго элемента ИЛИ, выход которого соединен с первым выходом блока и первым входом третьего элемента ИЛИ, второй вход которого соединен с вторым выходом блока, выходом первого элемента И и первым входом четвертого элемента ИЛИ, выход которого соединен с четвертым выходом блока, пятый выход которого соединен с выходом четвертого элемента И, выход третьего элемента ИЛИ соединен с шестым выходом блока.