Подложка с активной матрицей, устройство отображения, способ проверки подложки с активной матрицей и способ проверки устройства отображения

Иллюстрации

Показать всеПодложка с активной матрицей снабжена первыми проверочными токопроводящими дорожками (70, 75), выполненными с возможностью ввода контрольных сигналов на первые токопроводящие дорожки переключения, которые не являются смежными друг с другом, и на вторые токопроводящие дорожки переключения, которые не являются смежными друг с другом. Подложка снабжена также вторыми проверочными токопроводящими дорожками (72, 77), выполненными с возможностью ввода контрольных сигналов на первые токопроводящие дорожки переключения, которые не являются смежными друг с другом и не соединяются с первыми проверочными токопроводящими дорожками, и на вторые токопроводящие дорожки переключения, которые не являются смежными друг с другом и не соединяются с первыми проверочными токопроводящими дорожками. Технический результат - возможность надежного обнаружения короткого замыкания между смежными соединительными токопроводящими дорожками, сформированными на том же слое. 6 н. и 12 з.п. ф-лы, 9 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к подложке с активной матрицей, имеющей два и более слоев, с множеством первых соединительных токопроводящих дорожек, соответственно соединяющих множество первых токопроводящих дорожек, сформированных параллельно друг другу в области отображения, и множество первых выводов, расположенных в области расположения выводов, формирующейся на соответствующих слоях, к устройству отображения, способу проверки подложки с активной матрицей и способу проверки устройства отображения.

Предшествующий уровень техники

В последние годы жидкокристаллические панели широко использовались в разнообразных электронных устройствах, таких как мобильные телефоны, PDA, автомобильные навигационные системы и персональные компьютеры. Жидкокристаллические панели характеризуются малой толщиной, малым весом и энергоэффективностью. Что касается способов монтажа драйверов на такие жидкокристаллические панели, известен так называемый способ COG (кристалл на стекле), который включает в себя прямой монтаж драйвера на одну (подложку с активной матрицей) из пары подложек, располагающихся противоположно друг другу по всему жидкокристаллическому материалу (например, см. JP 2003-172944A, JP 2005-301308A, JP 2003-241217A, JP 2004-325956A, JP 2005-241988A, WO 2008/015808A). Использование этого способа COG предоставляет возможность изготовления жидкокристаллических панелей меньшей толщины, меньшего веса и большей яркости и с более высоким разрешением между токопроводящими дорожками и выводами.

Кроме того, количество вертикальных и горизонтальных пикселов экранов отображения жидкокристаллических панелей, используемых в компактных электронных устройствах, таких как мобильные телефоны и PDA, за последние годы перешло с 160×120 QQVGA и 176×144 QCIF (общий промежуточный формат с уменьшенным вчетверо разрешением) до 320×240 QVGA и, в том числе, до 640×480 VGA. Это привело к увеличению количества токопроводящих дорожек и выводов, которые должны формироваться на подложке с активной матрицей, составляющей жидкокристаллическую панель. Однако, учитывая потребность в жидкокристаллических панелях меньших размеров и более высокого разрешения, размер подложки с активной матрицей не может быть увеличен.

Ввиду этого, известна подложка с активной матрицей, на которой множество соединительных токопроводящих дорожек, соответственно соединяющих множество токопроводящих дорожек сканирования, сформированных в области отображения, и множество выводов сканирования, расположенных в области расположения выводов, формируются на двух и более слоях (многослойно) (например, см. JP 2004-53702A, JP 2005-91962A). В частности, предварительно заданное количество множества соединительных токопроводящих дорожек формируется на том же слое (первом слое), как и слой, на котором формируются токопроводящие дорожки сканирования, а оставшиеся соединительные токопроводящие дорожки формируются на слое (втором слое), отличном от слоя, на котором формируются токопроводящие дорожки сканирования. Следует отметить, что между соединительными токопроводящими дорожками, сформированными на первом слое, и соединительными токопроводящими дорожками, сформированными на втором слое, вставляется изоляционный материал. Это предоставляет возможность реализации жидкокристаллической панели меньших размеров и более высокого разрешения без увеличения размера подложки с активной матрицей, поскольку соединительные токопроводящие дорожки, сформированные на первом слое, и соединительные токопроводящие дорожки, сформированные на втором слое, могут быть сформированы на подложке с активной матрицей так, чтобы пересекаться друг с другом.

В частности, в связи с тем, что между соединительными токопроводящими дорожками, сформированными на первом слое, и соединительными токопроводящими дорожками, сформированными на втором слое, вставляется изоляционный материал, возникновение короткого замыкания (утечки) между соединительными токопроводящими дорожками, сформированными на первом слое, и соединительными токопроводящими дорожками, сформированными на втором слое, является маловероятным. Однако между смежными соединительными токопроводящими дорожками, сформированными на том же слое, может возникнуть короткое замыкание, вызванное засорением в процессе фотолитографии, травления остаточных материалов или подобного во время изготовления подложки с активной матрицей. В частности, в последние годы требовались жидкокристаллические панели меньших размеров и более высокого разрешения, как обсуждалось выше, повышающие вероятность возникновения короткого замыкания между смежными соединительными токопроводящими дорожками, сформированными на том же слое, поскольку расстояние между токопроводящими дорожками в последние годы сокращалось все больше и больше. Следовательно, возросла важность проверки на предмет короткого замыкания между соединительными токопроводящими дорожками в процессе проверки во время изготовления или подобного подложек с активной матрицей. То есть процесс монтажа драйвера на дефектную подложку с активной матрицей, на которой возникает короткое замыкание токопроводящих дорожек, приводит к материальным потерям и эксплуатационным расходам.

Однако, несмотря на повышающуюся важность проверки на предмет короткого замыкания между соединительными токопроводящими дорожками, механизм для обнаружения короткого замыкания между смежными соединительными токопроводящими дорожками, сформированными на том же слое, относительно каждого из множества слоев в подложке с активной матрицей, имеющей два и более слоев, не был установлен. В вышеупомянутых патентных документах (например, см. JP 2003-172944A, JP 2005-301308A, JP 2003-241217A, JP 2004-325956A, JP 2005-241988A, WO 2008/015808A, JP 2004-53702A, JP 2005-91962A) конфигурация для обнаружения короткого замыкания между смежными соединительными токопроводящими дорожками, сформированными на том же слое относительно каждого из множества слоев в подложке с активной матрицей, имеющей два и более слоев, раскрыта не была.

Существо изобретения

Настоящее изобретение было создано с учетом вышеупомянутых проблем. Задача настоящего изобретения заключается в обеспечении подложки с активной матрицей, устройства отображения, способа проверки подложки с активной матрицей и способа проверки устройства отображения, которые предоставляют возможность надежного обнаружения короткого замыкания между смежными соединительными токопроводящими дорожками, сформированными на том же слое, посредством использования простой конфигурации, относительно каждого из множества слоев.

Для решения вышеупомянутой задачи подложка с активной матрицей в настоящем изобретении включает в себя множество первых токопроводящих дорожек, сформированных параллельно друг другу в области отображения, множество вторых токопроводящих дорожек, сформированных параллельно друг другу так, чтобы пересекать множество первых токопроводящих дорожек в области отображения, множество первых выводов и множество вторых выводов, расположенных в области расположения выводов, множество первых соединительных токопроводящих дорожек, соответственно соединяющих множество первых токопроводящих дорожек и множество первых выводов, и множество вторых соединительных токопроводящих дорожек, соответственно соединяющих множество вторых токопроводящих дорожек и множество вторых выводов. Множество первых соединительных токопроводящих дорожек включает в себя множество третьих соединительных токопроводящих дорожек и множество четвертых соединительных токопроводящих дорожек, причем третьи соединительные токопроводящие дорожки формируются на том же слое, как и слой, на котором формируются первые токопроводящие дорожки, а, по меньшей мере, часть четвертых токопроводящих дорожек формируется на слое, отличном от слоя, на котором формируются первые токопроводящие дорожки с помещенным между ними изоляционным материалом, и подложка с активной матрицей включает в себя множество первых переключающих элементов, соответственно соединенных с множеством третьих соединительных токопроводящих дорожек, множество вторых переключающих элементов, соответственно соединенных с множеством четвертых соединительных токопроводящих дорожек, первую общую токопроводящую дорожку, соединенную с первыми переключающими элементами, которые не являются смежными друг с другом среди множества первых переключающих элементов, и со вторыми переключающими элементами, которые не являются смежными друг с другом среди множества вторых переключающих элементов, и вторую общую токопроводящую дорожку, соединенную с первыми переключающими элементами, которые не являются смежными друг с другом и не соединяются с первой общей токопроводящей дорожкой среди множества первых переключающих элементов, и со вторыми переключающими элементами, которые не являются смежными друг с другом и не соединяются с первой общей токопроводящей дорожкой среди множества вторых переключающих элементов.

В соответствии с подложкой с активной матрицей настоящего изобретения, контрольные сигналы могут быть введены на третьи соединительные токопроводящие дорожки через первые переключающие элементы посредством ввода взаимно независимых контрольных сигналов на первую общую токопроводящую дорожку и вторую общую токопроводящую дорожку, при поддержании первых переключающих элементов во включенном состоянии, в процессе проверки во время изготовления подложки с активной матрицей. То есть взаимно независимые контрольные сигналы могут быть введены на смежные третьи соединительные токопроводящие дорожки. Благодаря этому между смежными третьими соединительными токопроводящими дорожками может быть обнаружено короткое замыкание. Следует отметить, что третьи соединительные токопроводящие дорожки формируются на том же слое, как и слой, на котором формируются первые токопроводящие дорожки.

Кроме того, контрольные сигналы могут быть введены на четвертые соединительные токопроводящие дорожки через вторые переключающие элементы посредством ввода взаимно независимых контрольных сигналов на первую общую токопроводящую дорожку и вторую общую токопроводящую дорожку, при поддержании вторых переключающих элементов во включенном состоянии. То есть взаимно независимые контрольные сигналы могут быть введены на смежные четвертые соединительные токопроводящие дорожки. Благодаря этому между смежными четвертыми соединительными токопроводящими дорожками может быть обнаружено короткое замыкание. Следует отметить, что, по меньшей мере, часть четвертых соединительных токопроводящих дорожек формируется на слое, отличном от слоя, на котором формируются первые токопроводящие дорожки с помещенным между ними изоляционным материалом.

Кроме того, проверочные токопроводящие дорожки для проверки на предмет короткого замыкания между смежными третьими соединительными токопроводящими дорожками и проверочные токопроводящие дорожки для проверки на предмет короткого замыкания между смежными четвертыми соединительными токопроводящими дорожками совокупно являются первой общей токопроводящей дорожкой и второй общей токопроводящей дорожкой. Следовательно, количество проверочных токопроводящих дорожек, формирующихся на подложке с активной матрицей, может быть сокращено по сравнению со способом, в котором проверочные токопроводящие дорожки для проверки на предмет короткого замыкания между смежными третьими соединительными токопроводящими дорожками и проверочные токопроводящие дорожки для проверки на предмет короткого замыкания между смежными четвертыми соединительными токопроводящими дорожками соответственно конфигурируются в качестве дискретных проверочных токопроводящих дорожек. Кроме того, поскольку количество проверочных токопроводящих дорожек может быть сокращено, может быть упрощена система для ввода контрольных сигналов, а проверка может быть реализована с помощью простого устройства контроля.

В результате может быть реализована подложка с активной матрицей, которая предоставляет возможность надежного обнаружения короткого замыкания между смежными соединительными токопроводящими дорожками, сформированными на том же слое, посредством использования простой конфигурации относительно каждого из множества слоев.

Для достижения вышеупомянутой задачи устройство отображения в настоящем изобретении снабжается подложкой с активной матрицей в соответствии с настоящим изобретением. Следует отметить, что устройство отображения предпочтительно является жидкокристаллическим устройством отображения.

Для достижения вышеупомянутой цели способ проверки подложки с активной матрицей или устройства отображения в настоящем изобретении включает в себя процесс проверки третьих соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на первую общую токопроводящую дорожку и вторую общую токопроводящую дорожку, при поддержании первых переключающих элементов во включенном состоянии, и процесс проверки четвертых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на первую общую токопроводящую дорожку и вторую общую токопроводящую дорожку, при поддержании вторых переключающих элементов во включенном состоянии.

В соответствии со способом проверки подложки с активной матрицей или устройства отображения настоящего изобретения короткое замыкание на третьих соединительных токопроводящих дорожках, сформированных на том же слое, как и слой, на котором формируются первые токопроводящие дорожки, может быть обнаружено посредством ввода взаимно независимых контрольных сигналов на первую общую токопроводящую дорожку и вторую общую токопроводящую дорожку, при поддержании первых переключающих элементов во включенном состоянии. Кроме того, короткое замыкание на четвертых соединительных токопроводящих дорожках, по меньшей мере, часть которых формируется на слое, отличном от слоя, на котором формируются первые токопроводящие дорожки, может быть обнаружено посредством ввода взаимно независимых контрольных сигналов на первую общую токопроводящую дорожку и вторую общую токопроводящую дорожку, при поддержании вторых переключающих элементов во включенном состоянии. Следует отметить, что процесс проверки третьих соединительных токопроводящих дорожек может следовать до или после процесса проверки четвертых соединительных токопроводящих дорожек.

Как было описано выше, подложка с активной матрицей, устройство отображения и способ проверки подложки с активной матрицей настоящего изобретения достигают результата надежного обнаружения короткого замыкания между смежными соединительными токопроводящими дорожками, сформированными на том же слое, с помощью простой конфигурации относительно каждого из множества слоев.

Краткое описание чертежей

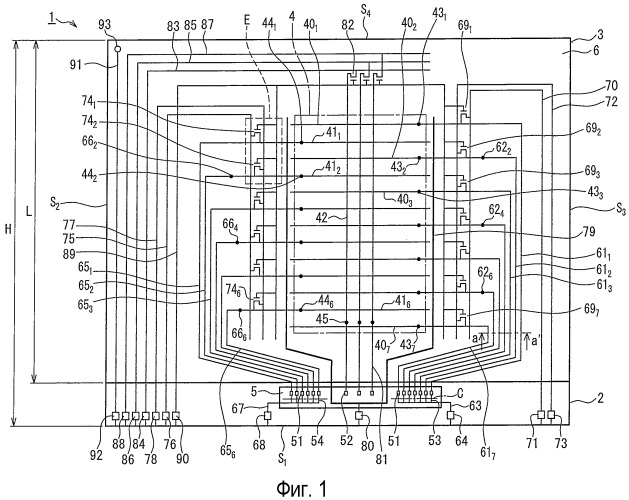

Фиг.1 изображает вид сверху, иллюстрирующий схематическую конфигурацию жидкокристаллической панели в соответствии с вариантом осуществления;

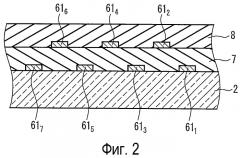

фиг.2 изображает поперечный разрез, выполненный вдоль штриховой линии a-a' на фиг.1;

фиг.3 изображает поперечный разрез, иллюстрирующий схематическую конфигурацию другой жидкокристаллической панели в соответствии с вариантом осуществления, в позиции, аналогичной изображенной на фиг 2;

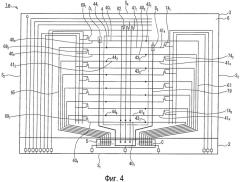

фиг.4 изображает вид сверху, иллюстрирующий схематическую конфигурацию другой жидкокристаллической панели в соответствии с вариантом осуществления;

фиг.5 изображает схему, иллюстрирующую увеличенный вид части E, изображенной на фиг.1;

фиг.6 изображает схему, иллюстрирующую часть другой подложки с активной матрицей в соответствии с вариантом осуществления, в позиции, аналогичной изображенной на фиг.5;

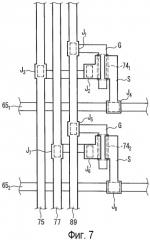

фиг.7 изображает иллюстративную схему, иллюстрирующую часть другой подложки с активной матрицей в соответствии с вариантом осуществления, в позиции, аналогичной изображенной на фиг.5;

фиг.8 изображает иллюстративную схему, иллюстрирующую часть другой подложки с активной матрицей в соответствии с вариантом осуществления, в позиции, аналогичной изображенной на фиг.5;

фиг.9 изображает иллюстративную схему, иллюстрирующую часть другой подложки с активной матрицей в соответствии с вариантом осуществления, в позиции, аналогичной изображенной на фиг.5.

Предпочтительный вариант осуществления изобретения

В варианте осуществления настоящего изобретения множество первых токопроводящих дорожек предпочтительно включает в себя множество третьих токопроводящих дорожек, каждая из которых имеет входной конец сигнала на одном конце, и множество четвертых токопроводящих дорожек, каждая из которых имеет входной конец сигнала на противоположном конце, причем третьи токопроводящие дорожки и четвертые токопроводящие дорожки формируются в области отображения поочередно, причем множество третьих соединительных токопроводящих дорожек предпочтительно включает в себя множество пятых соединительных токопроводящих дорожек, соответственно соединяющих множество первых выводов и входные концы третьих токопроводящих дорожек, которые не являются смежными друг с другом среди множества третьих токопроводящих дорожек, и множество шестых соединительных токопроводящих дорожек, соответственно соединяющих множество первых выводов и входные концы четвертых токопроводящих дорожек, которые не являются смежными друг с другом среди множества четвертых токопроводящих дорожек, причем множество четвертых соединительных токопроводящих дорожек предпочтительно включает в себя множество седьмых соединительных токопроводящих дорожек, соответственно соединяющих множество первых выводов и входные концы третьих токопроводящих дорожек, которые не являются смежными друг с другом и не соединяются с пятыми соединительными токопроводящими дорожками среди множества третьих токопроводящих дорожек, и множество восьмых соединительных токопроводящих дорожек, соответственно соединяющих множество первых выводов и входные концы четвертых токопроводящих дорожек, которые не являются смежными друг с другом и не соединяются с шестыми соединительными токопроводящими дорожками среди множества четвертых токопроводящих дорожек, причем первые переключающие элементы предпочтительно включают в себя множество третьих переключающих элементов, соответственно соединенных с множеством пятых соединительных токопроводящих дорожек, и множество четвертых переключающих элементов, соответственно соединенных с множеством шестых соединительных токопроводящих дорожек, причем вторые переключающие элементы предпочтительно включают в себя множество пятых переключающих элементов, соответственно соединенных с множеством седьмых соединительных токопроводящих дорожек, и множество шестых переключающих элементов, соответственно соединенных с множеством восьмых соединительных токопроводящих дорожек, причем первая общая токопроводящая дорожка предпочтительно включает в себя третью общую токопроводящую дорожку, соединенную с третьими переключающими элементами, которые не являются смежными друг с другом среди множества третьих переключающих элементов, и с пятыми переключающими элементами, которые не являются смежными друг с другом среди множества пятых переключающих элементов, и четвертую общую токопроводящую дорожку, соединенную с четвертыми переключающими элементами, которые не являются смежными друг с другом среди множества четвертых переключающих элементов, и с шестыми переключающими элементами, которые не являются смежными друг с другом среди множества шестых переключающих элементов, причем вторая общая токопроводящая дорожка предпочтительно включает в себя пятую общую токопроводящую дорожку, соединенную с третьими переключающими элементами, которые не являются смежными друг с другом и не соединяются с третьей общей токопроводящей дорожкой среди множества третьих переключающих элементов, и с пятыми переключающими элементами, которые не являются смежными друг с другом и не соединяются с третьей общей токопроводящей дорожкой среди множества пятых переключающих элементов, и шестую общую токопроводящую дорожку, соединенную с четвертыми переключающими элементами, которые не являются смежными друг с другом и не соединяются с четвертой общей токопроводящей дорожкой среди множества четвертых переключающих элементов, и с шестыми переключающими элементами, которые не являются смежными друг с другом и не соединяются с четвертой общей токопроводящей дорожкой среди множества шестых переключающих элементов.

В варианте осуществления настоящего изобретения множество третьих переключающих элементов и множество пятых переключающих элементов предпочтительно формируются в периферийной области токопроводящих дорожек, рядом с входными концами третьих токопроводящих дорожек, и множество четвертых переключающих элементов и множество шестых переключающих элементов предпочтительно формируются в периферийной области токопроводящих дорожек, рядом с входными концами четвертых токопроводящих дорожек.

В варианте осуществления настоящего изобретения третья общая токопроводящая дорожка предпочтительно формируется в периферийной области токопроводящих дорожек так, чтобы пересекать каждую из множества пятых соединительных токопроводящих дорожек и каждую из множества седьмых соединительных токопроводящих дорожек, причем пятая общая токопроводящая дорожка предпочтительно формируется в периферийной области токопроводящих дорожек так, чтобы пересекать каждую из множества пятых соединительных токопроводящих дорожек и каждую из множества седьмых соединительных токопроводящих дорожек, причем четвертая общая токопроводящая дорожка предпочтительно формируется в периферийной области токопроводящих дорожек так, чтобы пересекать каждую из множества шестых соединительных токопроводящих дорожек и каждую из множества восьмых соединительных токопроводящих дорожек, и шестая общая токопроводящая дорожка предпочтительно формируется в периферийной области токопроводящих дорожек так, чтобы пересекать каждую из множества шестых соединительных токопроводящих дорожек и каждую из множества восьмых соединительных токопроводящих дорожек.

В варианте осуществления настоящего изобретения третья общая токопроводящая дорожка и пятая общая токопроводящая дорожка предпочтительно являются смежными друг с другом, причем четвертая общая токопроводящая дорожка и шестая общая токопроводящая дорожка предпочтительно являются смежными друг с другом, причем, по меньшей мере, один из множества третьих переключающих элементов предпочтительно формируется между третьей общей токопроводящей дорожкой и пятой общей токопроводящей дорожкой, причем, по меньшей мере, один из множества пятых переключающих элементов предпочтительно формируется между третьей общей токопроводящей дорожкой и пятой общей токопроводящей дорожкой, причем, по меньшей мере, один из множества четвертых переключающих элементов предпочтительно формируется между четвертой общей токопроводящей дорожкой и шестой общей токопроводящей дорожкой, и, по меньшей мере, один из множества шестых переключающих элементов предпочтительно формируется между четвертой общей токопроводящей дорожкой и шестой общей токопроводящей дорожкой.

В варианте осуществления настоящего изобретения множество третьих переключающих элементов предпочтительно формируется между третьей общей токопроводящей дорожкой и пятой общей токопроводящей дорожкой, причем все множество пятых переключающих элементов предпочтительно формируется между третьей общей токопроводящей дорожкой и пятой общей токопроводящей дорожкой, причем все множество четвертых переключающих элементов предпочтительно формируется между четвертой общей токопроводящей дорожкой и шестой общей токопроводящей дорожкой, а все множество шестых переключающих элементов предпочтительно формируется между четвертой общей токопроводящей дорожкой и шестой общей токопроводящей дорожкой.

В варианте осуществления настоящего изобретения первая общая токопроводящая дорожка затвора, соединенная с электродом затвора каждого третьего переключающего элемента и каждого пятого переключающего элемента, предпочтительно формируется между третьей общей токопроводящей дорожкой и пятой общей токопроводящей дорожкой с помощью третьих переключающих элементов, формирующихся на обеих сторонах, помещая между ними первую общую токопроводящую дорожку затвора, и пятых переключающих элементов, формирующихся на обеих сторонах, помещая между ними первую общую токопроводящую дорожку затвора, а вторая общая токопроводящая дорожка затвора, соединенная с электродом затвора каждого четвертого переключающего элемента и каждого шестого переключающего элемента, предпочтительно формируется между четвертой общей токопроводящей дорожкой и шестой общей токопроводящей дорожкой с помощью четвертых переключающих элементов, формирующихся на обеих сторонах, помещая между ними вторую общую токопроводящую дорожку затвора, и шестых переключающих элементов, формирующихся на обеих сторонах, помещая между ними вторую общую токопроводящую дорожку затвора.

В варианте осуществления настоящего изобретения подложка с активной матрицей предпочтительно дополнительно включает в себя множество первых удлиненных токопроводящих дорожек, индивидуально проходящих от множества первых выводов, соответственно соединенных с множеством пятых соединительных токопроводящих дорожек, и множества первых выводов, соответственно соединенных с множеством седьмых соединительных токопроводящих дорожек, седьмую общую токопроводящую дорожку, соединенную с каждой из множества первых удлиненных токопроводящих дорожек, множество вторых удлиненных токопроводящих дорожек, индивидуально проходящих от множества первых выводов, соответственно соединенных с множеством шестых соединительных токопроводящих дорожек, и множества первых выводов, соответственно соединенных с множеством восьмых соединительных токопроводящих дорожек, и восьмую общую токопроводящую дорожку, соединенную с каждой из множества вторых удлиненных токопроводящих дорожек.

В варианте осуществления настоящего изобретения предпочтительно каждая из множества вторых токопроводящих дорожек имеет входной конец сигнала на одном конце, и подложка с активной матрицей предпочтительно дополнительно включает в себя множество седьмых переключающих элементов, соединенных с противоположным концом вторых токопроводящих дорожек, девятую общую токопроводящую дорожку, соединенную с седьмыми переключающими элементами, которые не являются смежными друг с другом среди множества седьмых переключающих элементов, и десятую общую токопроводящую дорожку, соединенную с седьмыми переключающими элементами, которые не являются смежными друг с другом и не соединяются с девятой общей токопроводящей дорожкой среди множества седьмых переключающих элементов.

В варианте осуществления настоящего изобретения множество первых токопроводящих дорожек предпочтительно включает в себя первую группу первых токопроводящих дорожек, смежных друг с другом, каждая из которых имеет входной конец сигнала на одном конце, и вторую группу первых токопроводящих дорожек, смежных друг с другом, каждая из которых имеет входной конец сигнала на противоположном конце, и множество первых соединительных токопроводящих дорожек предпочтительно соответственно соединяет множество первых выводов и входные концы первой группы первых токопроводящих дорожек, и соответственно соединяют множество первых выводов и входные концы второй группы первых токопроводящих дорожек.

В варианте осуществления настоящего изобретения первые токопроводящие дорожки предпочтительно являются токопроводящими дорожками сканирования, а вторые токопроводящие дорожки являются токопроводящими дорожками данных.

В варианте осуществления настоящего изобретения способ проверки подложки с активной матрицей, в соответствии с вариантом осуществления, или устройства отображения, снабженного подложкой с активной матрицей, в соответствии с вариантом осуществления, предпочтительно включает в себя процесс проверки пятых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на третью общую токопроводящую дорожку и пятую общую токопроводящую дорожку, при поддержании третьих переключающих элементов во включенном состоянии, процесс проверки седьмых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на третью общую токопроводящую дорожку и пятую общую токопроводящую дорожку, при поддержании пятых переключающих элементов во включенном состоянии, процесс проверки шестых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на четвертую общую токопроводящую дорожку и шестую общую токопроводящую дорожку, при поддержании четвертых переключающих элементов во включенном состоянии, и процесс проверки восьмых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на четвертую общую токопроводящую дорожку и шестую общую токопроводящую дорожку, при поддержании шестых переключающих элементов во включенном состоянии.

В варианте осуществления настоящего изобретения способ проверки подложки с активной матрицей, в соответствии с вариантом осуществления, или устройства отображения, снабженного подложкой с активной матрицей, в соответствии с вариантом осуществления, предпочтительно включает в себя процесс проверки третьих токопроводящих дорожек посредством ввода контрольного сигнала с седьмой общей токопроводящей дорожки, процесс проверки четвертых токопроводящих дорожек посредством ввода контрольного сигнала с восьмой общей токопроводящей дорожки, процесс отключения множества первых удлиненных токопроводящих дорожек и множества вторых удлиненных токопроводящих дорожек, процесс проверки пятых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на третью общую токопроводящую дорожку и пятую общую токопроводящую дорожку, при поддержании третьих переключающих элементов во включенном состоянии, процесс проверки седьмых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на третью общую токопроводящую дорожку и пятую общую токопроводящую дорожку, при поддержании пятых переключающих элементов во включенном состоянии, процесс проверки шестых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на четвертую общую токопроводящую дорожку и шестую общую токопроводящую дорожку, при поддержании четвертых переключающих элементов во включенном состоянии, и процесс проверки восьмых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на четвертую общую токопроводящую дорожку и шестую общую токопроводящую дорожку, при поддержании шестых переключающих элементов во включенном состоянии.

В варианте осуществления настоящего изобретения способ проверки подложки с активной матрицей, в соответствии с вариантом осуществления, или устройства отображения, снабженного подложкой с активной матрицей, в соответствии с вариантом осуществления, предпочтительно включает в себя процесс проверки третьих токопроводящих дорожек посредством ввода контрольного сигнала с седьмой общей токопроводящей дорожки, процесс проверки четвертых токопроводящих дорожек посредством ввода контрольного сигнала с восьмой общей токопроводящей дорожки, процесс проверки вторых токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на девятую общую токопроводящую дорожку и десятую общую токопроводящую дорожку, при поддержании седьмых переключающих элементов во включенном состоянии, процесс отключения множества первых удлиненных токопроводящих дорожек и множества вторых удлиненных токопроводящих дорожек, процесс проверки пятых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на третью общую токопроводящую дорожку и пятую общую токопроводящую дорожку, при поддержании третьих переключающих элементов во включенном состоянии, процесс проверки седьмых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на третью общую токопроводящую дорожку и пятую общую токопроводящую дорожку, при поддержании пятых переключающих элементов во включенном состоянии, процесс проверки шестых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на четвертую общую токопроводящую дорожку и шестую общую токопроводящую дорожку, при поддержании четвертых переключающих элементов во включенном состоянии, и процесс проверки восьмых соединительных токопроводящих дорожек посредством ввода взаимно независимых контрольных сигналов на четвертую общую токопроводящую дорожку и шестую общую токопроводящую дорожку, при поддержании шестых переключающих элементов во включенном состоянии.

Далее в настоящем документе вариант осуществления настоящего изобретения будет описываться со ссылкой на чертежи.

Однако, на нижеупомянутых в настоящем документе чертежах, в целях простоты описания, только основные элементы, требуемые для описания настоящего изобретения, среди составляющих элементов варианта осуществления настоящего изобретения, изображаются в упрощенной форме. Следовательно, подложка с активной матрицей, в соответствии с настоящим изобретением, может быть снабжена произвольными составляющими элементами, которые не изображаются на чертежах, упомянутых в настоящем описании. Кроме того, размерности на чертежах не предназначаются для точного представления фактических размерностей составляющих элементов или размерных пропорций элементов.

Вышеупомянутые с первой по десятую общие токопроводящие дорожки будут описаны в настоящем варианте осуществления в качестве с первой по десятую контрольных токопроводящих дорожек. Более того, вышеупомянутые первая и вторая общие токопроводящие дорожки затвора будут описаны в настоящем варианте осуществления в качестве первой и второй токопроводящих дорожек управления.

Фиг.1 является видом сверху, иллюстрирующим схематическую конфигурацию жидкокристаллической панели 1, в соответствии с настоящим вариантом осуществления. Как изображено на фиг.1, жидкокристаллическая панель 1 снабжена подложкой 2 с активной матрицей и противоположной подложкой 3, которая находится напротив подложки 2 с активной матрицей. Жидкокристаллический материал (не изображен) помещается и содержится между подложкой 2 с активной матрицей и противоположной подложкой 3. Следует отметить, что слой цветного фильтра, который включает в себя фильтры R (красного), G (зеленого) и В (синего) цветов и черную матрицу, которая препятствует проникновению света между этими цветными фильтрами, формируется на противоположной подложке 3, в соответствии с настоящим вариантом осуществления. Общие электроды формируются на слое цветного фильтра.

В данном случае жидкокристаллическая панель 1, в соответствии с настоящим вариантом осуществления, используется в электронном устройстве для мобильных терминалов, таких как, например, мобильный телефон, PDA (личный цифровой секретарь), PHS (персональная телефонная система) или HHT (малогабаритный пульт). Помимо электронного устройства для мобильных терминалов жидкокристаллическая панель 1, в соответствии с настоящим вариантом осуществления, также используется в электронном устройстве, таком как игровой терминал, автомобильная навигационная система, персональный компьютер, телевизор, видеокамера или цифровая камера. В данном