Рециркуляционный преобразователь время-код прогрессирующего типа

Иллюстрации

Показать всеИзобретение относится к информационно-измерительной технике и может быть использовано для преобразования одиночных временных интервалов наносекундного диапазона длительностей в цифровой код в информационно-измерительной, радиолокационной и другой аппаратуре. Изобретение направлено на повышение быстродействия преобразования, что обеспечивается за счет того, что рециркуляционный преобразователь время-код прогрессирующего типа содержит первую схему ИЛИ, первый вход которой соединен с первой входной клеммой преобразователя, выход подключен через первую линию задержки к первому входу второй схемы ИЛИ, а выход первой схемы ИЛИ соединен со вторым входом второй схемы ИЛИ, выход которой подключен к первому входу первой схемы И и к первому входу третьей схемы ИЛИ, второй вход которой соединен со вторым входом первой схемы И, а выход через вторую линию задержки - с первым входом второй схемы И, второй вход которой подключен к выходу RS-триггера, а выход - к первому входу третьей схемы И, к первому входу четвертой схемы И и к счетному входу счетного триггера, прямой выход которого соединен со вторым входом третьей схемы И, а соединен инверсный - со вторым входом четвертой схемы И, выход которой соединен со счетным входом счетчика импульсов и со вторым входом первой схемы ИЛИ, первый вход которой подключен к S-входу RS-триггера, R-вход которого соединен с выходом четвертой схемы ИЛИ, первый вход которой подключен к выходу первой схемы И, а второй вход к R-входу счетного триггера, к управляющему входу счетчика импульсов и ко второй входной клемме преобразователя, третья входная клемма которого соединена с третьим входом третьей схемы ИЛИ, а выход третьей схемы И через элемент задержки подключен ко второму входу третьей схемы ИЛИ. 2 ил.

Реферат

Изобретение относится к радиоэлектронике и может использоваться для преобразования одиночных временных интервалов (ВИ) наносекундного диапазона длительностей в цифровой код в информационно-измерительной, радиолокационной и другой аппаратуре.

Известен преобразователь-аналог, содержащий два раздельных контура рециркуляции, один для рециркуляции старт-импульса, а второй - стоп-импульса, преобразуемого ВИ [1].

Недостатком преобразователя аналога является низкое быстродействие преобразования.

Известен также преобразователь (прототип), имеющий один контур рециркуляции, образованный первой схемой ИЛИ, выход которой подключен через первую линию задержки к первому входу второй схемы ИЛИ и через вторую линию задержки ко второму вход второй схемы ИЛИ, выход которой соединен с первым входом первой схемы ИЛИ и через делитель импульсов со счетным входом счетчика импульсов, а клемма вход преобразователя подключена ко второму входу первой схемы ИЛИ [2].

Недостатком преобразователя является низкое быстродействие преобразования.

Целью предлагаемого изобретения является повышение быстродействия преобразования.

Поставленная цель достигается введением в преобразователь-прототип второго контура рециркуляции, объединенного с первым и использовании первого контура для рециркуляции стартового импульса, а второго - для рециркуляции стопового импульса преобразуемого ВИ.

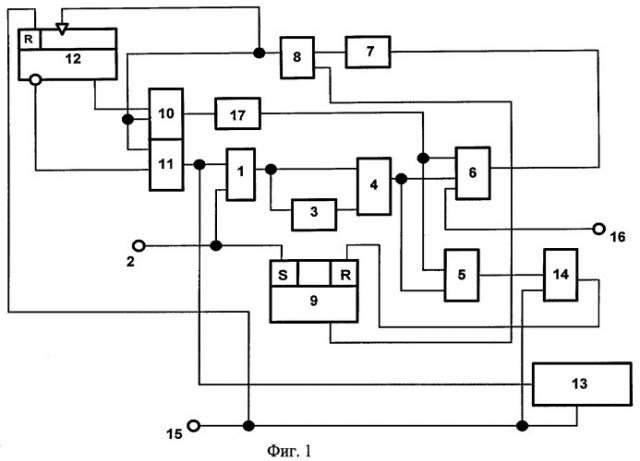

На фиг.1 приведена функциональная схема рециркуляционного преобразователя время-код (РПВК) прогрессирующего типа, а на фиг.2 - временные диаграммы его работы.

Рециркуляционный преобразователь время-код прогрессирующего типа содержит первую схему ИЛЦ(1) первый вход которой соединен с первой входной клеммой 2 преобразователя, а выход подключен через первую линию задержки 3 к первому входу второй схемы ИЛИ(4) выход первой схемы ИЛИ(1) соединен со вторым входом второй схемы ИЛИ(4), выход которой подключен к первому входу первой схемы И5, к первому входу третей схемы ИЛИ(6) второй вход которой соединен со вторым; входом первой схемы И(5) а выход через вторую линию задержки 7 - с первым входом второй схемы И(8) второй вход которой подключен к выходу RS-триггера 9, а выход - к первому входу третьей схемы И(10), к первому входу четвертой схемы И(11) и к счетному входу счетного триггера 12, прямой выход которого соединен со вторым входом третьей схемы И(10), а инверсный - со вторым входом четвертой схемы И(11), выход которой соединен со счетным входом счетчика импульсов 13 и со вторым входом первой схемы ИЛИ(1), первый вход которой подключен к S-входу RS-триггера 9, R-вход которого соединен с выходом четвертой схемы ИЛИ 14, первый вход которой подключен к выходу первой схемы И(5) а второй вход к R-входу счетного триггера 12, к управляющему входу счетчика импульсов 13 и ко второй входной клемме 15 преобразователя, третья входная клемма 16 которого соединена с третьим входом третьей схемы ИЛИ(6) а выход третьей схемы И(10) через элемент задержки 17 подключен ко второму входу третьей схемы ИЛИ(6)

Рассмотрим работу предлагаемого преобразователя.

Преобразователь имеет два совместных контура рециркуляции:

- первый контур образован логическими элементами: первой 1, второй 4 и третьей 6 схемами ИЛИ, второй 8 и четвертой 11 схемами И и аналоговыми элементами: первой 3 и второй 7 линиями задержки; а второй контур - логическими элементами: третьей схемой ИЛИ(6) второй 8 и третьей 10 схемами И, элементом задержки 17 и аналоговым элементом: второй линией задержки 7.

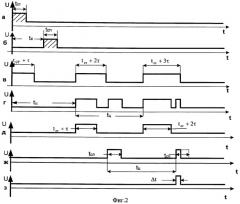

В первый контур рециркуляции через клемму 2 вводят старт-импульс и одновременно им же посредством RS-триггера и второй схемы И8 осуществляют открытие совмещенных контуров рециркуляции, а во второй контур посредством клеммы 16 вводят стоп-импульс, определяющие соответственно начало и конец преобразуемого временного интервала длительностью tx. Старт- и стоп-импульсы должны иметь калиброванные значения длительности tcт и tсп (см. Фиг.2а, б), причем tст>(tp1+τ), a tсп>(tp2+τ), где , , суммарное время переключения логических элементов соответственно первого и второго контуров рециркуляции, а τ - калиброванная величина длительности, представляет собой дискретность преобразования и задается временем задержки первой линии задержки 3.

В каждой из рециркуляции, имеющей период рециркуляции (время задержки tлз задается второй линией задержки 7), на выходе второй схемы ИЛИ4 (фиг.2в) старт-импульс имеет последовательно возрастающую (прогрессирующую) на значение τ длительность , i=1, 2, 3, …, Nt - порядковый номер рециркуляции.

В то же время стоп-импульс рециркулирует во втором контуре с периодом рециркуляции , но при этом его исходная длительность tсп остается неизменной. Для обеспечения условия необходимо, чтобы элемент задержки 17 обладал временем задержки tэз=t1+t4, a t10=t11 В каждой из рециркуляций импульсы и tсп объединяются третьей схемой ИЛИ(6), а затем после задержки на время ( - наибольшее значение длительности преобразуемого ВИ) во второй линии задержки 7 (см. фиг.2г) вновь разделяются посредством счетного триггера 12, работающего в режиме делителя импульсов с коэффициентом деления, равным двум, третьей 10 и четвертой 11 схем И (см. фиг.2, ж, д) и вводятся каждый в свой контур рециркуляции - импульсы через первую схему ИЛИ(1), а импульсы tсп через третью схему ИЛИ(6). Первая схема И5 фиксирует момент совпадения импульсов, рециркулирующих в первом и втором контурах, путем выделения на своем выходе импульса длительностью Δt (см. фиг.2з). Задним фронтом импульса Δt RS-триггер 9 переключается из состояния логическая единица в состояние логический ноль, вторая схема И8 закрывается и останавливает процесс рециркуляции в обоих контурах рециркуляции.

Счетчик импульсов 13 осуществляет подсчет числа импульсов рециркуляции nt в первом контуре рециркуляции с момента подачи в него старт-импульса, длительностью tст и до момента срабатывания RS-триггера 9. Область изменения числа рециркуляции nt∈[1;Nt], где .

Функция преобразования предлагаемого преобразователя имеет вид

tx=nt·τ+tcт

Полагая , где целое число m>1, то

Значение нетрудно определить в процессе настройки предлагаемого преобразователя как

где N* - цифровой результат определения значения tp.

Тогда выражение (1) предстает в виде

tx=(nt+m+N*)τ.

Перед началом преобразования сигналом начальной установки, подаваемого на вторую входную клемму 15 преобразователя, RS-триггер 9 и счетный триггер 12 по своим прямым выходам устанавливаются в состояние логического нуля, в счетчик импульсов 13 записывается число (m+N*). По окончании процесса преобразования в счетчике импульсов 13 будет записано число, равное (m+N*+nt), которое и представляет собой цифровой результат преобразования.

Время преобразования предлагаемого преобразователя описывается выражением

Тпр≥Nttц,

в то время как в случае преобразователя-прототипа

.

Следовательно, быстродействие предлагаемого преобразователя повышается в два раза.

Литература

1. Мелешко Е.А. Интегральные схемы в наносекундной ядерной электронике. Изд. 2-е доп., M.: Атомиздат, 1978, с.146-147, рис.3.15.

2. Авторское свидетельство СССР №654932, кл. G04F 10/00.

Рециркуляционный преобразователь время-код прогрессирующего типа, содержащий первую схему ИЛИ, первый вход которой соединен с первой входной клеммой преобразователя, а выход подключен через первую линию задержки к первому входу второй схемы ИЛИ; второю линию задержки и счетчик импульсов, отличающийся тем, что, с целью повышения быстродействия преобразования, выход первой схемы ИЛИ соединен со вторым входом второй схемы ИЛИ, выход которой подключен к первому входу первой схемы И и к первому входу третьей схемы ИЛИ, второй вход которой соединен со вторым входом первой схемы И, а выход через вторую линию задержки - с первым входом второй схемы И, второй вход которой подключен к выходу RS-триггера, а выход - к первому входу третьей схемы И, к первому входу четвертой схемы И и к счетному входу счетного триггера, прямой выход которого соединен со вторым входом третьей схемы И, а инверсный - со вторым входом четвертой схемы И, выход которой соединен со счетным входом счетчика импульсов и со вторым входом первой схемы ИЛИ, первый вход которой подключен к S-входу RS-триггера, R-вход которого соединен с выходом четвертой схемы ИЛИ, первый вход которой подключен к выходу первой схемы И, а второй вход к R-входу счетного триггера, к управляющему входу счетчика импульсов и ко второй входной клемме преобразователя, третья входная клемма которого соединена с третьим входом третьей схемы ИЛИ, а выход третьей схемы И через элемент задержки подключен ко второму входу третьей схемы ИЛИ.