Параллельный сумматор-вычитатель в троичной системе счисления на нейронах

Иллюстрации

Показать всеИзобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и производительных цифровых устройств суммирования вычитания чисел в троичной системе счисления в прямых кодах. Техническим результатом является снижение аппаратных затрат, упрощение комбинационной схемы, упрощение алгоритма работы устройства. Устройство содержит блок ввода и шифрации чисел, блок суммирования, блок регистра первого числа, блок регистра второго числа, блок регистра результата, блок управления. 18 ил., 10 табл.

Реферат

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и производительных цифровых устройств суммирования и вычитания чисел в троичной системе счисления в прямых кодах.

Известна "Схема цифрового сумматора" (заявка №99109089/09, от 04.07.1997, Бюл. №7 (1 ч.), 2001), позволяющая выполнять операцию сложения чисел в двоичной системе счисления.

Известно "Устройство для сложения" (заявка №4892584/24, от 19.12.1990, Бюл. №25, 1995), позволяющее складывать двоичные числа.

Известно "Устройство для вычисления модуля М-мерного вектора" (заявка 95104370/09, от 01.03.1995. Бюл №15, 1997), которое выполняет операции суммирования и вычитания над М-мерными векторами.

В качестве прототипа выбран "Параллельный сумматор-вычитатель на нейронах" (патент №2246752, Бюл №5, от 20.02.2005), который выполняет операции суммирования и вычитания чисел, представленных в двоичной системе счисления.

Задача заключалась в следующем:

1) увеличить диапазон представления чисел при выполнения операций сложения и вычитания,

2) упростить алгоритм блока управления,

3) повысить скорость операции суммирования чисел в прямых кодах,

4) выполнить операции суммирования и вычитания по закону сложения чисел в троичной системе счисления на двоичных элементах,

5) повысить надежность работы сумматора.

В представленном сумматоре-вычитателе происходит сложение и вычитание двоичных чисел по правилу выполнения арифметических операций в троичной системе счисления. Предлагаемый сумматор-вычитатель позволит значительно снизить аппаратные средства, что ведет к упрощению комбинационной схемы, а также значительно упростит алгоритм работы устройства.

Решение задачи осуществляется тем, что параллельный сумматор-вычитатель в троичной системе счисления на нейронах, содержащий блок суммирования, блок регистра результата, блок управления, отличающийся тем, что дополнительно введены: блок ввода и шифрации чисел, блок регистра первого числа, блок регистра второго числа, причем первый управляющий выход блока управления, на котором формируется сигнал синхронизирующего импульса первого двоичного триггера комбинационной схемы формирования сигнала перевода, соединен с первым управляющим входом блока ввода и шифрации чисел, второй управляющий выход блока управления, на котором формируется сигнал установки в нулевое состояние первого двоичного триггера комбинационной схемы формирования сигнала перевода, соединен со вторым управляющим входом блока ввода и шифрации чисел, третий управляющий выход блока управления, на котором формируется сигнал синхронизирующего импульса второго двоичного триггера комбинационной схемы формирования сигнала перевода, соединен с третьим управляющим входом блока ввода и шифрации чисел, четвертый управляющий выход блока управления, на котором формируется сигнал установки в нулевое состояние второго двоичного триггера комбинационной схемы формирования сигнала перевода, соединен с четвертым управляющим входом блока ввода и шифрации чисел, пятый управляющий выход блока управления, на котором формируется сигнал синхронизирующего импульса третьего двоичного триггера комбинационной схемы формирования сигнала перевода, соединен с пятым управляющим входом блока ввода и шифрации чисел, шестой управляющий выход блока управления, на котором формируется сигнал установки в нулевое состояние третьего двоичного триггера комбинационной схемы формирования сигнала перевода, соединен с шестым управляющим входом блока ввода и шифрации чисел, седьмой управляющий выход блока управления, на котором формируется сигнал установки в нулевое состояние двоичных триггеров блока ввода и шифрации чисел, соединен с седьмым управляющим входом блока ввода и шифрации чисел, информационный выход блока ввода и шифрации чисел, на котором формируются переведенный код входного числа, представленного в двоичном коде, передача входных двоичных кодов чисел осуществляется в параллельном режиме, соединен с первым информационным входом блока регистра первого числа и с первым информационным входом блока регистра второго числа, информационный выход блока регистра первого числа, на котором формируются переведенный код входного первого числа, представленного в двоичном коде, передача входных двоичных кодов первого числа осуществляется в параллельном режиме, соединен с первым информационным входом блока суммирования, информационный выход блока суммирования, на котором формируются результат суммы двоичных кодов входных чисел, представленного в двоичном коде, передача выходного двоичного кода суммы чисел осуществляется в параллельном режиме, соединен с первым информационным входом блока регистра результата, второй информационный вход блока регистра результата, на котором формируются сигналы установки в нулевое состояние двоичных триггеров, данный сигнал поступает параллельно на все входы установки в нулевое состояние триггеров и разрешающего для записи и хранения двоичных кодов в триггерах, данный сигнал поступает параллельно на все входы для разрешения записи в триггеры, соединен с первым информационным выходом блока управления, первый информационный вход блока управления, на котором формируются двоичные разряды суммы входных кодов чисел, передача данного информационного сигнала осуществляется в параллельном режиме, соединен информационным выходом блока регистра результата, второй информационный выход блока управления, на котором формируются сигналы установки в нулевое состояние двоичных триггеров, данный сигнал поступает параллельно на все входы установки в нулевое состояние триггеров и разрешающего для записи и хранения двоичных кодов в триггерах, данный сигнал поступает параллельно на все входы для разрешения записи в триггеры, соединен со вторым информационным входом блока регистра второго числа, информационный выход блока регистра второго числа, на котором формируются переведенный код входного второго числа, представленного в двоичном коде, передача входных двоичных кодов второго числа осуществляется в параллельном режиме, соединен со вторым информационным входом блока суммирования, третий информационный выход блока управления, на котором формируются сигналы установки в нулевое состояние двоичных триггеров, данный сигнал поступает параллельно на все входы установки в нулевое состояние триггеров и разрешающего для записи и хранения двоичных кодов в триггерах, данный сигнал поступает параллельно на все входы для разрешения записи в триггеры, соединен со вторым информационным входом блока регистра первого числа, первый и второй управляющие входы «СБРОС» и «ПУСК» блока управления являются внешними входами параллельного сумматора-вычитателя в троичной системе счисления на нейронах.

БВШЧ - блок ввода и шифрации чисел служит для ввода операндов и знака операции (+ или -), а также шифрации в троичную систему счисления чисел.

БСВ - блок суммирования служит для выполнения операций сложения и вычитания и коммутации входных чисел.

БРгПЧ - блок регистра первого числа служит для хранения двоичных разрядов первого числа.

БРгВЧ - блок регистра второго числа служит для хранения двоичных разрядов второго числа.

БРгР - блок регистра результата чисел служит для хранения кодовых разрядов результата - суммы чисел,

БУ - блок служит для управления устройством.

Троичные ЭВМ (компьютеры) обладают рядом преимуществ по сравнению с двоичными ЭВМ. Удельная натурально-логарифмическая плотность записи информации описывается уравнением y=(ln(х))/х, где x - основание системы счисления. Из уравнения следует, что наибольшей плотностью записи информации обладает система счисления с основанием, равным основанию натуральных логарифмов, то есть равным числу Эйлера (е=2,71…). Из целочисленных систем счисления наибольшей плотностью записи информации обладает троичная система счисления, поэтому при одинаковом числе аппаратных элементов - инверторов, троичные ЭВМ (компьютеры) имеют большую удельную емкость памяти и большую удельную производительность процессора, чем двоичные ЭВМ.

Троичная система счисления - позиционная целочисленная система счисления с основанием 3. Существует в двух вариантах: несимметричная (цифры 0, 1, 2) и симметричная (цифры -1, 0, 1). Троичная позиционная показательная несимметричная система счисления по затратам числа знаков наиболее экономична из позиционных показательных несимметричных систем счисления. Троичная система счисления использует три цифры - 0, 1 и 2, а также символы «+» и «-» для обозначения знака числа. Правила сложения чисел в троичной несимметричной системе счисления приведены в таблице 1. Для представления чисел в двоичной системе счисления необходимо каждое число из таблицы 1 закодировать двумя двоичными разрядами. Кодировка троичных чисел в двоичной системе счисления представлена в таблице 2. Для выполнения операций сложения и вычитания чисел в троичной системе счисления необходимо каждое десятичное число от 0 до 9 представить в коде 27-9-3-1, несимметричной троичной системе счисления. В таблице 3 представлены десятичные числа от 0 до 9 в двоично-десятичном коде 8-4-2-1 и в троичном коде 27-9-3-1. Черта над единицей в таблице 3 означает знак минус. Без черты на единицей означает знак плюс. Число пять в десятичной системе счисления будет представлено в троичной системе счисления как: 5=32-31-30. В таблице 4 каждый троичный разряд будет представлен двумя двоичными разрядами. Нуль будет иметь код нуль нуль 0 - 0 0, минус единица закодирована как нуль один - 1 - 0 1, плюс единица имеет код один нуль +1 - 1 0. Для кодирования цифр десятичной системы счисления достаточно задействовать три троичных разряда. Для хранения троичных чисел в сумматоре-вычитателе применяются двоичные RS триггеры таблица 4. При сложении чисел в троичной системе счисления необходимо учесть перенос из младшего разряда в старший. Складываются двоичные разряды по правилам сложения чисел в троичной системе счисления. Состояния 00, 01, 10 разрешены, код 11 запрещен. В таблице 5 представлены все возможные входные комбинации двух разрядных двоичных чисел A1A0 - первое двоичное число и В1В0 - второе двоичное число и все доступные коды переносов P01, Р00 из младших разрядов в старшие. Разряды A1, B1, P01 являются старшими, а А0, В0, Р00 младшими. Результатом сложения двух чисел A1A0 и B1B0 являются разряды суммы S1S0, соответственно старший и младший разряды суммы. Для получения доступных кодовых комбинаций в троичной системе счисления необходимо ввести коррекцию результата суммы: сложение с кодом 01 или 10. Окончательные разряды суммы с учетом коррекции представлены в таблице 5 как S11S10, старший и младший разряды результата соответственно. При сложении чисел необходимо определить разряды переносов в старшие разряды, в таблице 5 переносы представлены как Р11Р10 старший разряд и младший соответственно.

На фиг.1 изображена структурная схема сумматора-вычитателя.

На фиг.2 представлена структурная схема блока ввода и шифрации чисел.

На фиг.3 представлен вариант технической реализации блока ввода и шифрации чисел.

На фиг.4 изображены комбинационная схема формирования сигнала перевода и комбинационная схема перевода числа в код.

На фиг.5 изображена функциональная схема блока регистра первого числа.

На фиг.6 показана функциональна схема блока суммирования.

На фиг.7 представлен вариант технической реализации одноразрядного сумматора на нейронах.

На фиг.8 показаны принципиальные схемы сумматора младших разрядов, сумматора старших разрядов входных чисел, дешифратор, формирующий первый управляющий сигнал УС1, дешифратор, формирующий четвертый управляющий сигнал УС4, схема суммирования чисел младших разрядов суммы и коррекции, схема суммирования чисел старших разрядов суммы и коррекции.

На фиг.9 представлен вариант технической реализации дешифратора, формирующий второй управляющий сигнал УС2.

На фиг.10 представлен вариант технической реализации дешифратора, формирующий третий управляющий сигнал УС3.

На фиг.11 показана функциональна схема определения младшего разряда переноса, возникающего при суммировании двоичных разрядов входных чисел.

На фиг.12 показана функциональна схема определения старшего разряда переноса, возникающего при суммировании двоичных разрядов входных чисел.

На фиг.13 изображена функциональная схема блока регистра второго числа.

На фиг.14 представлен вариант технической реализации блока регистра результата.

На фиг.15 и 16 - содержательная ГСА работы сумматора-вычитателя.

На фиг.17 и 18 - размеченная ГСА работы устройства.

Параллельный сумматор-вычитатель на нейронах (фиг.1) содержит: блок ввода и шифрации чисел, блок суммирования, блок регистра первого числа, блок регистра второго числа, блок регистра результата, блок управления. В состав устройства входят: шифратор, комбинационная схема формирования сигнала перевода, комбинационная схема перевода числа в код, дешифраторы, двоичные триггеры, пороговые элементы, нейроны.

Для описания алгоритма работы блока 6 управления используются следующие идентификаторы.

1. КЧС - код числа.

2. КЧП - код входного числа переведенный.

3. ЗнРА - знаковый разряд первого числа А.

4. ЗнРВ - знаковый разряд второго числа В.

5. КО - код операции.

6. СН - сигнал синхронизации четвертого триггера Тр4 блока ввода и шифрации чисел.

7. ОБ - сигнал обнуления четвертого триггера Тр4 блока ввода и шифрации чисел.

8. СИН - сигнал синхронизации пятого триггера Тр5 блока ввода и шифрации чисел.

9. ОБН - сигнал обнуления пятого триггера Тр5 блока ввода и шифрации чисел.

10. СИ - сигнал синхронизации шестого триггера Тр6 блока ввода и шифрации чисел.

11. У0 - сигнал установки в нулевое состояние шестого триггера ТР6 блока ввода и шифрации чисел.

12. СПК - сигнал перевода кода.

13. КР0Ч…КРmЧ - кодовые разряды входных чисел.

14. КА0П…КАmП - кодовые разряда первого числа А преобразованные.

15. У0ТР - сигнал установки в нулевое состояние RS триггеров Тр1, Тр2, Тр3 шифратора ШД7.

16. УС0 - сигнал установки в нулевое состояния триггеров блока регистра первого числа.

17. РАЗ - сигнал разрешения записи информации в триггеры блока регистра первого числа.

18. УСТ0 - сигнал установки в нулевое состояния триггеров блока регистра второго числа.

19. РАЗЗ - сигнал разрешения записи информации в триггеры блока регистра второго числа.

20. УСН0 - сигнал установки в нулевое состояния триггеров блока регистра результата чисел.

21. РАЗП - сигнал разрешения записи информации в триггеры блока регистра результата чисел.

22. КВ0П…КВmП - кодовые разряда второго числа В преобразованные.

23. КР0П…КРmП - кодовые разряда результата преобразованные.

24. УС1, УС2, УС3, УС4 - управляющие сигналы с выходов дешифраторов DC1, DC2, DC3, DC4 соответственно.

25. СДШ - сигнал дешифраторов с выхода логической схемы ИЛИ.

26. А0…An - кодовые разряда первого числа А.

27. В0…Bn - кодовые разряда второго числа В.

28. СМ0…CMm - выходные кодовые разряды результата - суммы.

29. УП - информационный сигнал управления работой блока регистра результата, включающий в себя сигналы: обнуления, синхронизации, разрешения записи, хранения, выдачи.

30. ВПЧ - кодовая информация первого числа.

31. ВВЧ - кодовая информация второго числа.

32. СУП - информационный сигнал управления работой блока регистра второго числа.

33. СУ - информационный сигнал управления работой блока регистра первого числа.

34. А0…Ad - кодовые разряды первого числа.

35. В0…Bd - кодовые разряды второго числа.

36. Р00…Pn1 - кодовые разряды переносов чисел.

37. S0 - результат суммирования входных сигналов Р00, А0 и В0.

38. S1 - результат суммирования входных сигналов Р01, А1 и В1.

39. S10, S11 - кодовые разряды суммы входных сигналов блока суммирования СУМ1.

40. S0…Sz - кодовые разряды результата - суммы входных чисел.

41. i - счетчик, определяющий количество разрядов первого и второго входных чисел, старших и младших разрядов.

42. j - счетчик, определяющий количество переносов старшего и младшего разрядов.

43. k - счетчик, определяющий количество управляющих сигналов УС.

44. m - счетчик, определяющий текущий блок суммирования.

45. РЕЗ - входные кодовые разряды результата.

46. ПП - признак получения результата.

47. СБРОС - сигнал сброса (обнуления) всех комбинационных блоков и элементов памяти сумматора.

48. ПУСК - сигнал начало работы сумматора.

Работа алгоритма управления параллельного сумматора-вычитателя в троичной системе счисления на нейронах.

Содержательная граф-схема алгоритма ГСА приведена на фиг.15 и 16 и отражает работу устройства.

В блоке 2 алгоритма осуществляется подача сигнала установки в нулевое состояние - СБРОС на входы всех элементов устройства.

В блоке 3 алгоритма осуществляется подача внешнего сигнала ПУСК для работы устройства и установка его в единичное значение ПУСК:=1.

В блоке 4 алгоритма ПУСК по команде У0ТР=1 происходит параллельная подача сигнала установки в нулевое значение RS триггеров Тр1, Тр2, Тр3 на входы обнуления триггеров блока ввода и шифрации чисел, при этом триггеры устанавливаются в нулевое состояния, по команде Тр4=ОБ на вход R1 установки в нулевое состояние D триггера Тр4 подается единичный сигнал обнуления, устанавливая триггер Тр4 в нулевое состояние, по команде Тр5=ОБН на вход R2 установки в нулевое состояние D триггера Тр5 подается единичный сигнал обнуления, устанавливая триггер Тр5 в нулевое состояние, по команде Тр6=У0 на вход R3 установки в нулевое состояние D триггера Тр6 подается единичный сигнал обнуления, устанавливая триггер Тр6 в нулевое состояние, сигналы обнуления ОБ, ОБН, У0 подаются на входы D триггеров блока ввода и шифрации чисел.

В блоке 5 алгоритма анализируется признак ввода данных КЧС код числа. Если числовые данные не введены с клавиатуры, то осуществляется переход на блок 28 фигуры 16 - конечный блок. В обратном случае при наличии входных данных, работа устройства продолжается и происходит переход на блок 6 алгоритма.

В блоке 6 алгоритма по команде СН=1 происходит подача синхронизирующего импульса на синхровход D триггера Тр4 из блока управления, по команде СИН=1 происходит подача синхронизирующего импульса на синхровход D триггера Тр5 из блока управления, по команде СИ=1 происходит подача синхронизирующего импульса на синхровход D триггера Тр6 из блока управления.

В блоке 7 алгоритма по команде Тр4=ЗнРА в D триггер Тр4 блока ввода и шифрации чисел с клавиатуры пользователем вводится знаковый разряд первого числа ЗнРА, по команде Тр5=КО в D триггер Тр5 блока ввода и шифрации чисел аналогично вводится знаковый разряд кода операции КО, плюс или минус, по команде Тр6=ЗнРА в D триггер Тр6 блока ввода и шифрации чисел также вводится знаковый разряд второго числа ЗнРВ.

В блоке 8 алгоритма вычисляется сигнал перевода кода СПК по логической функции СПК=ЗнРА ИЛИ (КО ⊕ ЗнРВ). Если знаковый разряд первого числа ЗнРА равен единичному значению, то двоичные разряды первого числа переводятся в обратный код, кроме набора 00, при этом код 01 преобразуется в код 10, код 10 переводится в 01, двоичный набор 00 остается без изменения, так как состояние двоичного кода 11 является запрещенным в троичной системе счисления. В этом случае по логической операции ИЛИ сигнал перевода кода СПК будет равен единичному значению. По логической операции суммы по модулю два сигналов кода операции КО и знаковый разряд второго числа ЗнРВ определяется, переводить или не переводить знаковые разряды второго числа в обратный код. Если сигналы КО и ЗнРВ равны между собой, то по операции суммы по модулю два результат равен нулевому значению, в этом случае если выбрана операция вычитания и знаковый разряд второго числа равен единице, или выбрана операция суммирования и знаковый разряд второго числа равен нулевому значению. Знаковый разряд второго числа при этом равен нулевому значению, переводить прямые коды двоичных разрядов второго числа не надо. Если сигналы КО и ЗнРВ не равны между собой, то по операции суммы по модулю два результат равен единичному значению, в этом случае если выбрана операция вычитания и знаковый разряд второго числа равен нулю, или выбрана операция суммирования и знаковый разряд второго числа равен единице. Знаковый разряд второго числа при этом равен единичному значению, переводить прямые коды двоичных разрядов второго числа необходимо.

В блоке 9 алгоритма по команде КсхПЧК=КЧС на вход комбинационной схемы перевода числа в код КсхПЧК блока ввода и шифрации чисел поступает код входного числа КЧС для представления его в преобразованный двоичный код для выполнения операции сложения по правилам в троичной системе счисления, по команде КсхПЧК=СПК на вход комбинационной схемы перевода числа в код КсхПЧК блока ввода и шифрации чисел поступает управляющий сигнал перевода кода СПК в прямой код, если число положительное, или в обратный, если число отрицательное.

В блоках 10 и 11 алгоритма осуществляется запись первого входного числа в регистр блока регистра первого числа.

В блоке 10 алгоритма по команде БРгПЧ=СУ на входы регистра блока регистра первого числа БРгПЧ с выхода блока управления поступает информационный сигнал управления СУ. Управляющий сигнал состоит из управляющих сигналов УСО установки в нулевое состояние триггеров Тр7, Тр8,…Tpn и сигнал разрешения записи и хранения РАЗ информации в триггеры блока. Сигнал установки в нулевое состояние УС0 поступает параллельно на все входы обнуления триггеров и обнуляет их. Сигнал разрешения записи и хранения РАЗ информации также поступает параллельно на все синхровходы RS триггеров регистра блока, тем самым происходит разрешение записи и хранение информации в регистрах блока регистра первого числа.

В блоке 11 алгоритма по команде БРгПЧ=КЧП происходит подача информационных двоичных переведенных кодов КЧП на входы RS триггеров для записи и хранения числовых данных в регистрах блока регистра первого числа.

В блоках 12 и 13 алгоритма осуществляется запись второго входного числа в регистр блока регистра второго числа.

В блоке 12 алгоритма по команде БРгВЧ=УПР на входы регистра блока регистра второго числа БРгВЧ с выхода блока управления поступает информационный сигнал управления УПР. Информационный сигнал УПР состоит из управляющих сигналов У СТО установки в нулевое состояние триггеров Tpn+1, Tpn+2,… Tpt и сигнала разрешения записи и хранения РАЗЗ информации в триггеры блока. Сигнал установки в нулевое состояние УСТ0 поступает параллельно на все входы обнуления триггеров, и обнуляет триггеры. Сигнал разрешения записи и хранения РАЗЗ информации также поступает параллельно на все С синхровходы RS триггеров регистра блока, тем самым происходит разрешение записи, а затем хранение информации в регистрах блока регистра второго числа.

В блоке 13 алгоритма по команде БРгВЧ=КЧП происходит подача информационных двоичных переведенных кодов КЧП на входы RS триггеров для записи и хранения числовых данных в регистрах блока регистра второго числа.

В блоке 14 алгоритма по командам i=0; j=0; k=1; m=1 происходит присвоение начальных значений параметрам цикла, в котором происходит загрузка входных разрядов первого и второго чисел, а также переносов из младших разрядов сумматоров в старшие на входы блоков сумматора-вычитателя цифрового устройства. Количество разрядов входных чисел i равно нулевому значению i=0, количество переносов старших и младших разрядов j также принимает нулевое значение j=0, количество управляющих сигналов k первоначально принимает единичное значение k=1, количество блоков суммирования m в цикле также равно единице m=1, загрузка данными начинается с первого блока устройства.

В блоке 15 алгоритма анализируется соотношение m<=n, где m - текущее значение номера блока суммирования, a n - конечное число блоков суммирования. Если соотношение не выполняется, выход НЕТ блока, то осуществляется переход на блок 25 фигуры 16 алгоритма, где происходит запись окончательного результата в регистры блока регистра результата. По выходу ДА, если процесс загрузки данных в блоки сумматора продолжается, то осуществляется переход на блок 16 алгоритма.

В блоке 16 алгоритма по команде СУМ=Ai, Ai+1, Bi, Bi+1, Pj 0, Pj 1 происходит подача очередных младших и старших разрядов входных чисел, а также младших и старших разрядов переносов из младших разрядов в старшие. По выходу блока 16 алгоритма осуществляется переход на вход блока 17 фигуры 16 алгоритма.

В блоке 17 алгоритма по команде Si=Pj 0 ⊕ Ai ⊕ Bi вычисляется младший разряд суммы текущего блока сумматора-вычитателя. Младший разряд суммы вычисляется с помощью операции суммы по модулю два очередного младшего разряда переноса Pj 0 и очередных младших разрядов входных чисел Ai и Bi. Нулевое значение младший разряд принимает в случае четного количества единиц на входе сумматора по модулю два, единичное значение равно, если на входе нечетное количество единиц.

В блоке 18 алгоритма по команде Si+1=Pj 1 ⊕ Pi ⊕ Ai+1 ⊕ Bi+1 вычисляется старший разряд суммы текущего блока сумматора-вычитателя. Старший разряд суммы вычисляется с помощью операции суммы по модулю два очередного старшего разряда переноса Pj 1, переноса, возникающего из младших разрядов в старшие Pi при двухразрядном суммировании и очередных старших разрядов входных чисел Ai+1 и Bi+1. Нулевое значение младший разряд принимает в случае четного количества единиц на входе сумматора по модулю два, единичное значение равно, если на входе нечетное количество единиц.

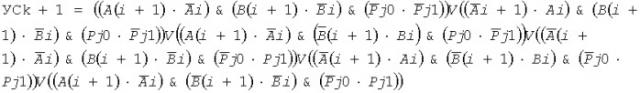

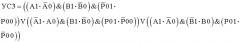

В блоке 19 алгоритма определяется управляющий сигнал УСk, равный УCk=(Pj 0 ⊕ Ai ⊕ Bi) & (Pj 1 ⊕ Pi ⊕ Ai+1 ⊕ Bi+1). Этот сигнал определяется с помощью логической функции И младшего и старшего разрядов суммы двоичных разрядов Si и Si+1. Управляющий сигнал определяет комбинацию двоичных разрядов 11, запрещенную в троичной системе счисления, и определяет коррекцию результата - плюс единицу в младший разряд окончательного результата согласно таблице 6. Управляющий сигнал УСk+1 определяется с помощью логической функции ИЛИ младших и старших разрядов входных чисел, а также младших и старших разрядов переносов. По команде

согласно таблице 8. Управляющий сигнал УCk+2 определяется с помощью логической функции ИЛИ младших и старших разрядов входных чисел, а так же младших и старших разрядов переносов. По команде

согласно таблице 9. Управляющий сигнал УCk+3 определяется с помощью логической функции И младших и старших разрядов входных чисел, а также младших и старших разрядов переносов. По команде согласно таблице 7.

В блоке 20 алгоритма по логической операции ИЛИ трех управляющих сигналов УCk, УCk+1, УCk+2 с выходов дешифраторов определяется сигнал СДШ дешифраторов. Сигнал СДШ дешифраторов равен единичному значению при равенстве единице, хотя бы одного из входных сигналов. Этот сигнал, равный единице, определяет коррекцию суммы.

В блоке 21 алгоритма по команде Sm 0=Si ⊕ СДШ с помощью операции суммы по модулю два определяется выходной младший разряд суммы текущего блока сумматора-вычитателя с учетом коррекции результата. Нулевое значение младший разряд принимает в случае четного количества единиц на входе сумматора по модулю два, единичное значение равно, если на входе нечетное количество единиц.

В блоке 22 алгоритма по команде Sm 1=Si+1 ⊕ Pi+1 ⊕ УCk+3 с помощью операции суммы по модулю два определяется выходной старший разряд суммы текущего блока сумматора-вычитателя. При сложении старшего разряда двоичных чисел, переноса из младших разрядов и управляющего сигнала с выхода дешифратора. Нулевое значение младший разряд принимает в случае четного количества единиц на входе сумматора по модулю два, единичное значение равно, если на входе нечетное количество единиц.

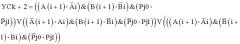

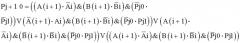

В блоке 23 алгоритма определяется младший разряд переноса в старший разряд Pj+1 0 по команде

Этот сигнал определяется с помощью логической функции ИЛИ младших и старших разрядов входных чисел Ai, Bi, Ai+1, Bi+1, а также младшего и старшего разрядов переноса из младшего разряда в старший Pj0, Pj1 согласно таблице 10. По команде определяется старший разряд переноса Pj+1 1 из младшего разряда в старший согласно таблице 10.

В блоке 24 алгоритма по команде i=i+2 происходит увеличение счетчика, определяющего количество разрядов первого и второго входных чисел, старших и младших разрядов на два, по команде j=j+1 происходит увеличение счетчика, определяющего количество переносов старшего и младшего разрядов на единицу, по команде k=k+4 выполняется увеличение счетчика, определяющего количество управляющих сигналов УС на четыре, по команде m=m+1 выполняется загрузка входных данных на вход очередного блока суммирования, при этом количество блоков m увеличивается на единицу. По выходу из блока 24 алгоритма осуществляется переход на блок 15 фигуры 15 алгоритма.

В блоке 25 алгоритма по команде БРгР=УП на входы регистра блока регистра результата БРгР с выхода блока управления поступает информационный сигнал управления УП. Управляющий сигнал состоит из управляющих сигналов УСН0 установки в нулевое состояние триггеров Tpt+1, Tpt+2,… Tps и сигнал разрешения записи и хранения РАЗП информации в триггеры блока. Сигнал установки в нулевое состояние УСН0 поступает параллельно на все входы обнуления триггеров и обнуляет их. Сигнал разрешения записи и хранения РАЗП информации также поступает параллельно на все синхровходы RS триггеров регистра блока, тем самым происходит разрешение записи и хранение информации в регистрах блока регистра результата.

В блоке 26 алгоритма по команде БРгР=РЕЗ происходит подача информационных двоичных кодов РЕЗ результата на входы RS триггеров для записи и хранения окончательного результата суммы чисел в регистрах блока регистра результата.

В блоке 27 алгоритма по команде БУ=СУМ происходит подача суммы чисел на входы блока управления для записи и хранения окончательного результата суммы чисел в регистрах блока управления.

Блок 28 алгоритма является конечным.

Работа параллельного сумматора-вычитателя на нейронах заключается в следующем.

Внешние управляющие сигналы "СБРОС" и "ПУСК" поступают в блок 6 управления. Троичный несимметричный код 0, 1, 2 обеспечивает оптимальное построение арифметики чисел. Знаком числа оказывается цифра старшего из его значащих (ненулевых) разрядов. Знак плюс будет представлен как код старшей цифры числа 10, знак минус как 01. Проблемы чисел со знаком, не имеющей в двоичном коде совершенного решения, в троичном несимметричном коде просто нет, чем и обусловлены его принципиальные преимущества. Для сложения чисел со знаками нет необходимости применять дополнительный или обратный коды чисел. Операция сложения выполняется в прямом коде. Знак числа эта кодовая комбинация двоичных разрядов 10 или 01 старшей цифры числа.

Блок 1 ввода и шифрации чисел содержит шифратор (обычная стандартная клавиатура) ШФ7, комбинационную схему перевода числа в код КСхПЧК8, комбинационную схему формирования сигнала перевода КСхФСП9 (фиг.2). Этот блок позволяет вводить двоичные числа, знаковые разряды чисел и код операции. С выхода шифратора формируется двоичный код троичных чисел со своими знаками. Выходными управляющими сигналами шифратора ШФ7 являются: код операции КО, если код операции равен нулевому значению, то выполняется операция суммирования, в случае равным единичному значению, то выполняется операция вычитания, знаковый разряд первого числа ЗнРА, если знаковый разряд числа равен нулевому значению, то число будет представлено в прямом коде, если этот сигнал равен единичному значению, то двоичные разряды троичного числа будут представлены в обратном коде, знаковый разряд второго числа ЗнРВ, если знаковый разряд числа равен нулевому значению, то число будет представлено в прямом коде, если этот сигнал равен единичному значению, то двоичные разряды троичного числа будут представлены в обратном коде. Эти сигналы устанавливаются пользователем при вводе чисел с клавиатуры. Управляющие сигналы: знаковый разряд первого числа ЗнРА, знаковый разряд второго числа ЗнРВ и код операции КО с выхода шифратора ШД7 поступают на вход комбинационной схемы формирования сигнала перевода КСхФСП9. Информационный сигнал код числа КЧС с выхода шифратора ШД7 поступает на вход комбинационной схемы перевода числа в код КСхПЧК8. Управляющий сигнал перевода кода СПК с выхода комбинационной схемы формирования сигнала перевода КСхФСП9 поступает на вход комбинационной схемы перевода числа в код КСхПЧК8. Внешним управляющим сигналом блока 1 ввода и шифрации чисел является сигнал установки в нулевое состояние RS триггеров УОТР, который поступает с выхода блока 6 управления. Сигнал УОТР устанавливает в нулевое значение RS триггеры: Тр1, Тр2, Тр3 шифратора ШД7. На вход комбинационной схемы формирования сигнала перевода КСхФСП9 с выхода блока 6 управления поступают управляющие сигналы: сигнал синхронизации СН четвертого триггера Тр4, сигнал обнуления ОБ четвертого триггера Тр4, сигнал синхронизации СИН пятого триггера Тр5, сигнал обнуления ОБН пятого триггера Тр5, сигнал синхронизации СИ шестого триггера Тр6, сигнал обнуления У 0 шестого триггера Тр6. Выходным информационным сигналом блока ввода и шифрации чисел является сигнал кода входного числа переведенный КПЧ (фиг.2).

Шифратор ШД7 содержит стандартную клавиатуру, с помощью которой вводятся входные числа и код операции, и систему логических элементов ИЛИ, выполненных на микросхемах DD 10, DD 11, DD 12, DD 13, DD 14. Три двоичных RS триггера Тр1, Тр2, Тр3, выполненных на микросхемах DD15, DD16, DD17, а также логические элементы И, выполненные на микросхемах DD18, DD19, DD20, каждый логический элемент И имеет первый инверсный вход, второй прямой вход входят в состав блока 1 ввода и шифрации чисел (фиг.3). Внешний управляющий сигнал установки в нулевое состояние RS триггеров Тр1, Тр2, Тр3 - У0ТР поступает с выхода блока 6 управления. Сигнал обнуления триггеров У0ТР параллельно поступает на входы R0 обнуления RS триггеров Тр1, Тр2, Тр3 блока 1 ввода и шифрации чисел, триггеры при этом устанавливаются в нулевое состояния. При вводе десятичного числа происходит коммутация одной из кнопок клавиатуры ШД7. На выходах логических элементов ИЛИ формируются двоичные коды, соответствующие номеру нажатой кнопки. В RS триггеры блока будут записаны двоичные коды десятичных цифр. Прямые выходы каждого RS триггера Qt поступают на вторые прямые входы логических схем И. На первые инверсные входы схем И поступают одновременно сигналы, которые приходят на R входы триггеров с выходов логических элементов ИЛИ. Выходной сигнал А0 равен входному двоичному разряду, выходной сигнал А1 равен логической функции . Выходной сигнал А2 равен входному двоичному разряду, выходной сигнал A3 равен . Выходной сигнал А4 равен входному двоичному разряду, выходной сигнал А5 равен . Выходные разряды А0 и A1 представляют собой кодовые разряды младшего троичного разряда числа, каждое троичное число представлено двумя двоичными разрядами. Выходные разряды А2 и A3 представляют собой кодовые разряды очередного троичного разряда числа. Выходные разряды А4 и А5 представляют собой кодовые разряды старшего троичного разряда числа. Выходным информационным сигналом блока 1 ввода и шифрации чисел является информационный сигнал кода числа КЧС (фиг.3).

В состав блока 1 ввода и шифрации чисел входят: комбинационная схема 8 перевода числа в код КСхПЧК и комбинационная схема 9 формирования сигнала перевода КСхФСП (фиг.4). Комбинационная схема 8 перевода числа в код КСхПЧК содержит систему логических элементов И, выполненных на микросхемах DD28, DD29, DD30, DD31, систему логических элементов сумматоров по мод