Вычислительная открытая развиваемая асинхронная модульная система

Иллюстрации

Показать всеИзобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания высокопроизводительных, быстродействующих вычислительных систем. Техническим результатом является повышение надежности работы вычислительной модульной системы и расширение функциональных возможностей в части передачи заданий от арифметико-символьного процессора к вычислительным модулям; записи результатов с использованием интерфейсных каналов процессор-модуль и модуль-модуль, применения элементов пороговой логики. Вычислительная открытая развиваемая асинхронная модульная система содержит арифметико-символьный процессор, систему коммутации процессор-модуль, специализированные вычислительные модули, систему коммутации модуль-модуль, блок периферийных устройств, блок управления, оперативные запоминающие устройства, двоичные счетчики, пороговые элементы, шинные формирователи, двоичные сумматоры. 18 ил.

Реферат

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания высокопроизводительных, быстродействующих вычислительных систем, выполняющих основные арифметические, символьные и логические операции: суммирование, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой, осуществляющих поисковые функции и операции замены, выполняющих логические операции - инверсию, конъюнкцию, дизъюнкцию и исключающую ИЛИ, а также операции, выполняющиеся специализированными вычислительными модулями, и функции коммутации.

Известен "Сумматор-вычитатель старшими разрядами вперед на нейронах" (з-ка RU №2205444 27.05.2003 г.), выполняющий операции суммирование и вычитание двоичных чисел в прямых кодах старшими разрядами вперед.

Известно "Поисковое устройство произвольных вхождений" (з-ка RU, №2209465 от 27.07.2003 г.), осуществляющая поиск произвольных вхождений в обрабатываемых словах.

Известно "Устройство поиска и замены произвольных вхождений в словах текста" (з-ка RU, №2250493 19.04.2005 г.), которое выполняет функцию поиска и замены произвольных вхождений в словах текста.

Известен "Параллельный сумматор-вычитатель на нейронах" (з-ка RU №2246752 от 20.02.2005 г.), который выполняет операции суммирование и вычитание двоичных чисел.

Известно "Устройство выполнения логических операций" (з-ка RU, №2288500 от 27.11.2006 г.), которое выполняет логические операции: инверсию, конъюнкцию, дизъюнкцию и исключающую ИЛИ.

Известен "Арифметический вычислитель" (з-ка RU, №2292580 27.01.2007 г.), выполняющий основные арифметические операции: сложение, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой.

В качестве прототипа выбран "Арифметико-символьный процессор" (з-ка RU №2316047 от 27.01.2008 г.), который выполняет основные арифметические операции: сложение, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой, осуществляющий поисковые функции и операции замены, а также выполняет логические операции: инверсия, конъюнкция, дизъюнкция и исключающая ИЛИ.

Задача заключалась в следующем:

1) расширить функциональные возможности вычислительной системы;

2) повысить надежность работы вычислительной модульной системы.

В представленной вычислительной системе выполняются основные арифметические операции: сложение, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой, осуществляются поисковые функции и операции замены, выполняются логические операции - инверсия, конъюнкция, дизъюнкция и исключающие ИЛИ, осуществляется распределение ресурсов со многими параметрами, решается задача сортировки данных без применения операции копарации, выполняется ускоренное умножение чисел с примененм пороговых элементов и нейронов, осуществляется операция сортировка слов с применением ассоциативного запоминающего устройства, параллельная система выполняет операции поиска и замены в различных режимах обработки символьной информации, а также выполняется передача заданий и результатов с использованием интерфейсных каналов процессор-модуль и модуль-модуль. Предлагаемая вычислительная открытая развиваемая асинхронная модульная система позволит расширить функциональные возможности устройства.

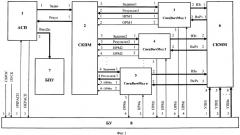

Решение задачи осуществляется тем, что вычислительная открытая развиваемая асинхронная модульная система, содержащая арифметико-символьный процессор, блок управления, отличающаяся тем, что дополнительно введены: система коммутации процессор-модуль, первый специализированный вычислительный модуль, второй специализированный вычислительный модуль, n-й специализированный вычислительный модуль, система коммутации модуль-модуль, блок периферийных устройств, причем управляющий выход арифметико-символьного процессора соединен с третьим управляющим входом блока управления, первый управляющий выход которого соединен с управляющим входом арифметико-символьного процессора, первый информационный выход которого соединен с первым информационным входом системы коммутации процессор-модуль, первый информационный выход которой соединен с информационным входом арифметико-символьного процессора, второй информационный выход которого соединен с информационным входом блока периферийных устройств, второй информационный выход системы коммутации процессор-модуль соединен с первым информационным входом первого специализированного вычислительного модуля, первый информационный выход которого соединен со вторым информационным входом системы коммутации процессор-модуль, первый управляющий вход которой соединен с первым управляющим выходом первого специализированного вычислительного модуля, второй управляющий выход которого соединен со вторым управляющим входом системы коммутации процессор-модуль, третий информационный выход которой соединен с первым информационным входом второго специализированного вычислительного модуля, первый информационный выход которого соединен с третьим информационным входом системы коммутации процессор-модуль, третий управляющий вход которой соединен с первым управляющим выходом второго специализированного вычислительного модуля, второй управляющий выход которого соединен с четвертым управляющим входом системы коммутации процессор-модуль, четвертый информационный выход, которой соединен с первым информационным входом n-го специализированного вычислительного модуля, первый информационный выход которого соединен с четвертым информационным входом системы коммутации процессор-модуль, пятый управляющий вход которой соединен с первым управляющим выходом n-го специализированного вычислительного модуля, второй управляющий выход, которого соединен с шестым управляющим входом системы коммутации процессор-модуль, второй информационный выход первого специализированного вычислительного модуля соединен с первым информационным входом системы коммутации модуль-модуль, первый информационный выход, которой соединен со вторым информационным входом первого специализированного вычислительного модуля, третий управляющий выход которого соединен с шестым управляющим входом блока управления, четвертый управляющий выход которого соединен с управляющим входом первого специализированного вычислительного модуля, второй информационный выход второго специализированного вычислительного модуля соединен со вторым информационным входом системы коммутации модуль-модуль, второй информационный выход которой соединен со вторым информационным входом второго специализированного вычислительного модуля, третий управляющий выход, которого соединен с пятым управляющим входом блока управления, третий управляющий выход которого соединен с управляющим входом второго специализированного вычислительного модуля, второй информационный выход n-го специализированного вычислительного модуля соединен с третьим информационным входом системы коммутации модуль-модуль, третий информационный выход которой соединен со вторым информационным входом n-ого специализированного вычислительного модуля, третий управляющий выход которого соединен с четвертым управляющим входом блока управления, второй управляющий выход, которого соединен с управляющим входом n-го специализированного вычислительного модуля, первый, второй и третий информационные выходы блока управления соединены соответственно с четвертым, пятым и шестым информационными входами системы коммутации модуль-модуль, первый и второй управляющие входы СБРОС и ПУСК блока управления являются внешними входами вычислительной открытой развиваемой асинхронной модульной системы.

Вычислительную открытую развиваемую асинхронную модульную систему (ВОРАМС) можно представить как иерархию универсальной ЭВМ, систему специализированных вычислительных модулей и гибкую подсистему интерфейсных каналов параллельной передачи информации между устройствами. В представленной системе отдельное устройство имеет собственные средства обработки, оперативное запоминающее устройство для хранения данных, локальную коммутацию и автономный блок управления, становится самостоятельным, функционально полным вычислительным модулем. В вычислительной системе предложены неоднородные модули, в которых явно выражена функциональная специализация устройств. Универсальная вычислительная машина, реализующая любой алгоритм, не может конкурировать со специализированными вычислительными модулями при решении определенных задач. Специализированные модули эффективно решают задачи по обработке и сортировке массивов, упорядочения данных, распределения ресурсов между локализованными центрами, ускоренное выполнение арифметические операции. В связи с этим поле их применения, безусловно, будет расширяться. Вычислительные специализированные процессоры не менее чем на порядок дешевле равномощного универсального устройства.

Основным принципом развития в архитектуре вычислительных систем является распараллеливание и совмещение процессов разных типов. Одновременно увеличивается число решаюших модулей. В связи с этим возникает проблева организации коммутации и обменов между процессором и устройствами, а также функцианальное соединение между вычислительными модулями.

ВОРАМС - открытая развиваемая система совместимых функциональных модулей, которая способна к статической и динамической реконфигурации. Она может быть адаптирована к использованию в различных областях применения. Система имеет параллельную структуру за счет использование интерфейсных каналов соединения процессора и вычислительных модулей, характеризуется также асинхронностью работы составляющих ее устройст, имеет упорядоченную спецификацию модулей и интерфейсов [1, 2].

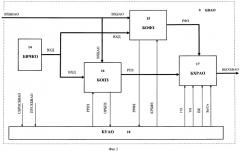

Вычислительная открытая развиваемая асинхронная модульная система ВОРАМС (фиг.1) содержит: арифметико-символьный процессор, систему коммутации, обеспечивающую соединение процессора и специализированных вычислительных модулей, специализированные вычислительные модули, систему коммутации, выполняющую функцию интерфейсного соединения между специализированными вычислительными модулями системы, блок периферийных устройств, блок управления.

АСП - арифметико-символьный процессор, который выполняет основные арифметические операции: сложение, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой, осуществляющий поисковые функции и операции замены, а также выполняет логические операции - инверсия, конъюнкция, дизъюнкция и исключающая ИЛИ.

СКПМ - система коммутации процессор-модуль служит для соединения процессора и специализированных вычислительных модулей системы.

СпецВычМод1 - первый специализированный модуль, выполняющий функции поиска и замены вхождений в обрабатывающих словах, а также специализированные операции символьной обработки.

СпецВычМод2 - второй специализированный модуль, выполняющий функции сортировки слов.

СпецВычМодn - n-е специализированные модули, выполняющие арифметические, логические операции, операции сортировки символов, задачи распределения ресурсов.

СКММ - система коммутации модуль-модуль служит для соединения между собой специализированных вычислительных модулей системы.

БПУ - блок периферийных устроств служит для выполнения операций чтения, записи, сканирования, передачи, печати и т.д. входной и выходной информации.

БУ - блок служит для управления вычислительной системой.

В арифметико-символьном процессоре выполняются основные арифметические операции: сложение, вычитание, умножение и деление чисел в прямых кодах с фиксированной и плавающей запятой, осуществляются поисковые функции и операции замены, а также выполняются логические операции - инверсия, конъюнкция, дизъюнкция и исключающая ИЛИ. Предлагаемый арифметико-символьный процессор позволит расширить функциональные возможности устройства, повысить надежность работы процессора, упростит алгоритм работы устройства.

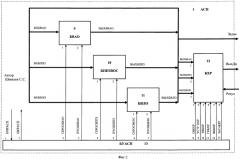

Арифметико-символьный процессор (фиг.2) содержит: блок выполнения арифметических операций, блок параллельного поиска и замены в обрабатываемых словах, блок выполнения логических операций, блок хранения результатов, блок управления арифметико-символьного процессора [5].

БВАО - блок выполнения арифметических операций служит для выполнения операций с фиксированной и плавающей запятой.

БППЗВОС - блок параллельного поиска и замены в обрабатываемых словах служит для выполнения поисковых операций и функции замены.

БВЛО - блок выполнения логических операций служит для выполнения логических операций: конъюнкция, дизъюнкция, инверсия, исключающее ИЛИ.

БХР - блок хранения результатов служит для записи и хранения результатов выполнения арифметических, поисковых и логических операций.

БУАСП - блок служит для управления арифметико-символьным процессором.

Существуют специфические задачи обработки символьной информации, т.е. текстов. Тексты имеют очень большие объемы, измеряемые гигабайтами. Тексты имеют сложную внутреннюю структурную организацию: лексическую, морфологическую и синтаксическую. Отсюда вытекают специфические задачи лексикографического, морфологического и синтаксического анализа и т.д. В системы числовой обработки вводятся процессоры быстрого преобразования данных. Арифметические операции выполняются в параллельном режиме, в форматах с фиксированной и плавающей запятой. Доля символьной информации в общем потоке информации составляет более 80%. Доля числовой информации в общем потоке информации составляет всего 10-15%. Для увеличения производительности универсальные системы обработки символьной информации, а также системы обработки числовых данных и выполнения логических операций расширяются специализированными процессорами.

Блок выполнения арифметических операций БВАО

Арифметические операции двоичных чисел в блоке выполняются в параллельном режиме, в формате с фиксированной и плавающей запятой в прямых кодах (фиг.3).

БВЧКО - блок ввода чисел служит для ввода операндов и знака операции, значений логических переменных.

БОФЗ - блок выполнения операций с фиксированной запятой в прямом коде служит для выполнения основных арифметических операций в формате с фиксированной запятой.

БОПЗ - блок выполнения операций с плавающей запятой в прямом коде служит для выполнения основных арифметических операций в формате с плавающей запятой.

БХРАО - блок хранения результатов арифметических операций служит для записи и хранения в нем результатов выполнения арифметических операций.

БУАО - блок арифметических операций служит для управления устройством выполнения арифметических операций.

В современных ЭВМ операция вычитания выполняется с применением дополнительного или обратного кода. При вводе отрицательного числа осуществляется перевод его в дополнительный или обратный код. Полученный результат также анализируется. Если получен отрицательный результат, то осуществляется перевод в дополнительный или обратный код. Если получен положительный результат, то перевода в коды не происходит. По этому алгоритму результат можно получить только после анализа знакового разряда результата. В случае ввода двух отрицательных чисел необходимо перевести оба числа в коды. Результат в этом случае также переводится в дополнительный или обратный код [3].

Известен алгоритм сложения чисел в прямых кодах. Этот алгоритм позволяет сразу получить правильный результат в прямом коде. В этом случае необходимо применить операцию вычитания чисел. Для этого используется комбинационная схема вычитателя чисел в прямых кодах.

Для получения суммы двух чисел возможны два случая:

1) слагаемые имеют одинаковые знаки;

2) слагаемые имеют разные знаки.

Алгоритм получения суммы двух чисел с одинаковыми знаками определяется следующим образом:

Алгоритм первый:

1) сложить два числа;

2) сумме присвоить знак одного из слагаемых.

Алгоритм получения суммы двух чисел с разными знаками определяется следующем образом:

1) сравниваются знаки слагаемых, и если они одинаковы, то выполняется сложение по первому алгоритму;

2) если знаки слагаемых разные, то сравниваются числа по абсолютной величине;

3) если есть необходимость переставить числа местами, чтобы вычитать из большего меньшее;

4) произвести вычитание двух чисел;

5) результату присвоить знак большего слагаемого.

Этот алгоритм позволяет получить сумму или разность чисел в прямых кодах. В арифметическом вычислителе не происходит сравнения чисел, если числа имеют разные знаки, в нем применена операция вычитания из первого числа второго. Если формируется заем из знакового разряда, то в этом случае от меньшего числа вычитается большее. Числа в этом случае с помощью коммутатора меняются местами на входе нейронов сумматора-вычитателя. На втором такте от второго большего числа вычитается первое меньшее. Если заема не образуется, то от большего первого числа вычитается меньшее второе. Менять местами числа на входе нейронов не нужно.

Операция умножения выполняется в прямом коде умножением младшими разрядами множителя со сдвигом суммы частичных произведений влево. Знак произведения определяется путем сложения знаковых цифр сомножителей по модулю два.

Операция деления выполняется по алгоритму деление чисел без восстановления остатков. Для определения следующей цифры частного необходимо сдвинуть текущий остаток влево на один разряд, а затем алгебраически прибавить к нему модуль делителя, которому приписывается знак, противоположный знаку текущего остатка. Знак остатка определяет следующую цифру частного: если остаток положительный, то в частном записывается 1, если отрицательный, то записывается 0. Операция сдвигов и алгебраических сложений повторяется до тех пор, пока в частном не получится требуемое количество цифр. Знак частного определяется путем сложения знаковых цифр делимого и делителя по модулю два. По таким алгоритмам выполняются основные арифметические операции с фиксированной запятой [3, 4].

Числа в формате с плавающей запятой представляются в виде: знака порядка, значения порядка, знака мантиссы, мантиссы. При выполнении основных арифметических операций в формате с плавающей запятой необходимо выполнять операции над порядками, затем над мантиссами чисел.

Операции сложения, вычитания чисел, представленных в формате с плавающей запятой, выполняются по следующему алгоритму:

1) осуществляется сравнение порядков путем вычитания их как целых чисел;

2) производится выравнивание мантиссы числа с меньшим порядком в сторону числа с большим порядком;

3) производится алгебраическое сложение или вычитание мантисс чисел;

4) в случае получения левой или правой денормализации мантиссы производится нормализация результата. Нормализация осуществляется с помощью операций сдвига вправо на один разряд и серии сдвигов влево до получения значащей цифры после запятой.

Операция умножения чисел с плавающей запятой выполняется в следующей последовательности:

1) находится знак произведения при помощи операции суммы по модулю два знаковых разрядов мантисс чисел;

2) выполняется сложение порядков сомножителей;

3) находится произведение мантисс сомножителей по алгоритму произведения чисел с фиксированной запятой, т.е. умножением младшими разрядами множителя со сдвигом суммы частичных произведений влево;

4) при получении денормализации осуществляется нормализация результата путем сдвига произведения влево до получения значащей цифры после запятой.

Операция деления чисел в формате с плавающей запятой выполняется по следующему алгоритму:

1) определяется знак частного с помощью операции суммы по модулю два знаковых разрядов мантисс делимого и делителя;

2) вычитаются порядки чисел по правилам вычитания операндов с фиксированной запятой. Из порядка делимого вычитается порядок делителя. При возникновении денормализации результата выполняется операции сдвига, тем самым осуществляется нормализация результата;

3) находится частное мантисс делимого и делителя по алгоритму деление чисел без восстановления остатков в формате чисел с фиксированной запятой. Для определения следующей цифры частного необходимо сдвинуть текущий остаток влево на один разряд, а затем алгебраически прибавить к нему модуль делителя, которому приписывается знак, противоположный знаку текущего остатка. Знак остатка определяет следующую цифру частного: если остаток положительный, то в частном записывается 1, если отрицательный, то записывается 0. Операция сдвигов и алгебраических сложений повторяется до тех пор, пока в частном не получится требуемое количество цифр;

4) нормализация частного при помощи операций сдвига.

На фиг.2 изображена структурная схема арифметико-символьного процессора.

На фиг.3 изображена структурная схема блока выполнения арифметических операций.

На фиг.4 представлен вариант технической реализации блока ввода чисел и кода операций.

На фиг.5 представлен вариант технической реализации блока операций, выполняющий вычисления с фиксированной запятой.

На фиг.6 представлен вариант технической реализации блока операций, выполняющий вычисления с плавающей запятой.

Блок выполнения арифметических операций (фиг.2) содержит: блок ввода чисел, блок операций с фиксированной запятой, блок операций с плавающей запятой, блок хранения результата, блок управления арифметическими операциями, пороговые элементы, нейроны.

Для описания алгоритма работы блоков 13 управления работой арифметико-символьного процессора и блока 18 управления выполнения арифметическими операциями используются следующие идентификаторы:

1. ОКРАСП - сигнал окончания работы арифметико-символьного процессора.

2. НЧРАСП - сигнал начало работы арифметико-символьного процессора.

3. СБРОСБВАО - сигнал сброса в нулевое состояние всех элементов памяти блока выполнения арифметичеких операций.

4. ПУСКБВАО - сигнал пуска работы блока выполнения арифметических операций.

5. СБРОСБППЗ - сигнал сброса в нулевое состояние всех элементов памяти блока параллельного поиска и замены.

6. ПУСКБППЗ - сигнал пуска работы блока параллельного поиска и замены.

7. СБРОСБВЛО - сигнал сброса в нулевое состояние всех элементов памяти блока выполнения логических операций.

8. ПУСКБВЛО - сигнал пуска работы блока выполнения логических операций.

9. ВХБВАО - входной информационный сигнал блока выполнения арифметических операций.

10. ВХБППЗ - входной информационный сигнал блока параллельного поиска и замены.

11. ВХБВЛО - входной информационный сигнал блока выполнения логических операций.

12. ВЫХБВАО - выходной информационный сигнал блока выполнения арифметических операций.

13. ВЫХБППЗ - выходной информационный сигнал блока параллельного поиска и замены.

14. ВЫХБВЛО - выходной информационный сигнал блока выполнения логических операций.

15. Резул - результат операций арифметико-символьного процессора, входной информационный сигнал блока хранения результатов.

16. ВыхДн - выходной информационный сигнал блока хранения результатов из ОЗУ блока.

17. УС"0"БХР - установка в нулевое значение триггеров блока хранения результатов.

18. ОББХР - сигнал обнуления триггеров блока хранения результатов.

19. ТИБХР - тактовые импульсы блока хранения результатов.

20. ГНБХР - генератор прямоугольных импульсов блока хранения результатов.

21. ВКБХР - сигнал выбора кристала ОЗУ блока хранения результатов.

22. Зп/СчБХР - сигнал записи/считывания информации из ОЗУ блока хранения результатов.

23. БВЧКО - блок ввода чисел и кода операции.

24. БОФЗ - блок выполнения операций с фиксированной запятой.

25. БОПЗ - блок выполнения операций с плавающей запятой.

26. БХР - блок хранения результатов.

27. БУАСП - блок управления арифметико-символьным процессором.

28. БРгПЧ - блок регистра первого числа.

29. БСВ - блок сумматора-вычитателя.

30. БРгВЧ - блок регистра второго числа.

31. БФЗР - блок формирования знакового разряда.

32. БРгРЕЗ - блок регистра результата.

33. ВХЧ - входные числа.

34. ЗРПЧ - знаковый разряд первого числа.

35. ЗРВЧ - знаковый разряд второго числа.

36. ЗЗР - знаковый разряда большего по модулю числа.

37. ЗРРЗ - знаковый разряд результата.

38. РЕЗ - окончательный результат.

39. ПЧ - первое число.

40. ВЧ - второе число.

41. ОСТ - остаток при делении.

42. ПДЧ - признак дробной части при делении.

43. ЦДЧ - целая и дробная часть результата при делении.

44. УПР - сигналы управления в блок регистра результата.

45. СУП - сигналы управления (обнуление, синхронизация, разрешение записи, сдвига) блока регистра второго числа.

46. УП - сигналы управления блока регистра первого числа (обнуление, синхронизация, разрешение записи).

47. РФЗ - результат с фиксированной запятой.

48. РМН - разряд множителя при умножении.

49. КОП - код операции (СУМ, ВЫЧ, ДЕЛ, УМН).

50. УМН - операция умножение.

51. ДЕЛ - операция деление.

52. ЗрОСТ - знаковый разряд остатка при делении чисел.

53. ППР - признак пустого регистра второго числа.

54. ВХД - выходные данные блока ввода чисел и кода операции.

55. РПЗ - результат с плавающей запятой.

56. РРФЗ - разрешение работы блока с фиксированной запятой.

57. КРБФЗ - конец работы блока с фиксированной запятой.

58. РРПЗ - разрешение работы блока с плавающей запятой.

59. КРБФЗ - конец работы блока с фиксированной запятой.

60. ОРБПЗ - окончание работы блока с плавающей запятой.

61. ГИ - генератор прямоугольных импульсов.

62. ТИ - тактовые импульсы.

63. ВК - сигнал выбора кристалла.

64. Зп/Сч - сигнал записи/считывания информации из ОЗУ.

65. ВХЧМН - входные числа мантисс в арифметике с плавающей запятой.

66. ВХЧПР - входные порядки чисел с плавающей запятой.

67. СНМН - сигнал нормализации мантиссы.

68. РПЗПР - результат с плавающей запятой порядков.

69. РПЗМН - результат с мантисс с плавающей запятой.

70. СВ - признак операций суммирование или вычитание.

71. БУОФЗ - блок управления операциями с фиксированной запятой.

72. БУАО - блок управления устройством для выполнения арифметических операций.

73. БХРАО - блок хранения результатов арифметических операций.

74. БОПРПЗ - блок выполнения операций порядков с плавающей запятой.

75. БОМПЗ - блок выполнения операций с плавающей запятой.

Работа блока выполнения арифметических операций заключается в следующем.

Внешние управляющие сигналы СБРОСАСП и ПУСКАСП поступают в блок 5 управления арифметико-символьного процессора.

Предлагаемый блок выполнения арифметических операций выполняет операции: суммирование, вычитание, умножение и деление в параллельном формате. Определяется перенос в старшие разряды при суммировании, который необходимо учитывать при сложении чисел. Вычисляется заем из старших разрядов в младшие при вычитании. Умножение выполнятся младшими разрядами множителя со сдвигом суммы частичных произведений влево. Операция деление осуществляется по алгоритму деление чисел без восстановление остатков.

Арифметико-символьный процессор содержит: блок выполнения арифметических операций БВАО, блок параллельного поиска и замены в обрабатываемых словах БППЗОС, блок выполнения логических операций БВЛО, блок хранения результатов БХР, блок управления арифметико-символьного процессора БУАСП (фиг.2). БВАО - блок выполнения арифметических операций служит для выполнения операций с фиксированной и плавающей запятой. БППЗОС - блок параллельного поиска и замены служит для выполнения поисковых операций и функции замены в обрабатываемых словах. БВЛО - блок выполнения логических операций служит для выполнения логических операций: конъюнкция, дизъюнкция, инверсия, ИСКЛЮЧАЮЩЕЕ ИЛИ. БХР - блок хранения результатов служит для записи и хранения результатов выполнения арифметических, поисковых и логических операций. БУАСП - блок служит для управления устройством. Выходные информационные сигналы блоков: ВЫХБВАО - выходной информационный сигнал блока выполнения арифметических операций, ВЫХБППЗ - выходной информационный сигнал блока параллельного поиска и замены, ВЫХБВЛО - выходной информационный сигнал блока выполнения логических операций по замкнутой шине подаются на входы каждого блока арифметико-символьного процессора. Циклическая передача информации обеспечивает выполнение сложных задач по выполнению арифметических операций, операций поиска и замены, а также логических операций. Результаты выполнения каждого блока поступают также на входы блока хранения результатов БХР. Входным информационным сигналом Резул является результат выполнения операций специализированных вычислительных модулей, который поступает на вход блока хранения результатов. Выходной информационный сигнал Задан является выходом из кольцевой информационной шины, а также заданием для выполнения операций на специализированных вычислительных модулях системы. Выходной информационный сигнал ВыхДн - выходная информация является выходом блока хранения результатов (фиг.2).

Блок 9 выполнения арифметических операций БВАО содержит: блок ввода чисел и кода операций БВЧКО, блок операций с фиксированной запятой БОФЗ, блок операций с плавающей запятой БОПЗ, блок хранения результата арифметических операций БХРАО, блок управления арифметическими операциями БУАО (фиг.3). Входным информационным сигналом является сигнал ВХБВАО - входной информационный сигнал блока выполнения арифметических операций. Выходной информационный сигнал ВЫХБВАО - результат арифметических операций - является выходным сигналом блока выполнения арифметических операций.

Блок 14 ввода чисел и кода операций БВЧКО содержит шифратор (обычная стандартная клавиатура) ШФ и дешифратор ДШКОП (фиг.3, 4). Этот блок позволяет вводить двоичные числа и дешифрировать код операций, т.е. распознать, какую операцию необходимо выполнить блоку выполнения арифметических операций - сложение, вычитание, умножение, деление. С выхода шифратора формируется двоичный код чисел со своими знаками: ЗpiПЧ, ЗpiBЧ, ЗРПЧ, ЗРВЧ в виде информационного сигнала ВХЧ. Двоичные разряды с выхода шифратора поступают на вход регистров первого и второго числа. С выхода дешифратора кода операций ДШКОП (фиг.4) формируется информационный сигнал КОП - код операций, который поступает на вход блока формирования знакового разряда БФЗР (фиг.5). В зависимости от кода операции блок выполнения арифметических операций выполняет соответствующую арифметическую операцию. Выходным информационным сигналом блока 14 БВЧКО является сигнал ВХД - выходные данные.

Блок 15 операций с фиксированной запятой БОФЗ содержит: блок 21 формирования знакового разряда результата - БФЗР, блок 22 регистра первого числа - БРгПЧ, блок 23 сумматора-вычитателя - БСВ, блок 24 регистра второго числа - БРгВЧ, блок 25 регистра результата - БРгРЕЗ, блок 26 управления операциями с фиксированной запятой - БУОФЗ (фиг.3, 5). Основная функция этого блока заключается в вычислении результата и формировании знакового разряда результата при выполнении операций умножения и деления, а также определения типа операций: сложение или вычитание. На информационные входы блоков 22 и 24 регистров первого и второго числа поступают входные операнды ВХЧ из блока 14 ввода чисел (фиг.3, 4,5). В случае выполнения операций умножения или деления этот блок по операции суммы по модулю два определяет знаковый разряд результата - ЗРРЗ, поступающий на вход блока 25 регистра результата ЗРРЗ=ЗРПЧ ⊕ ЗРВЧ, где ЗРПЧ - знаковый разряд первого числа, ЗРВЧ - знаковый разряд второго числа. Если блок выполнения арифметических операций выполнял операции сложения или вычитания, то знаковый разряд результата ЗЗР формируется в блоке 23 сумматора-вычитателя и поступает на вход блока 21 формирования знакового разряда. На управляющие входы блоков 22, 24, 25 регистра первого числа, второго числа, результата из блока 26 управления операциями с фиксированной запятой поступают соответственно информационные сигналы: УП на блок 22 регистра первого числа, СУП на блок 24 регистра второго числа, УПР на блок 25 регистра результата. По приходу сигналов осуществляется обнуление регистров этих блоков, синхронизация по записи информации, а также сигналы сдвига в блоки регистров первого и второго числа. На входы блока 23 сумматора-вычитателя поступают двоичные коды чисел ПЧ - первое число и ВЧ - второе число для выполнения операций сложения, вычитания, умножения и деления. На вход блока 23 сумматора-вычитателя из блока 21 формирования знакового разряда поступают управляющие сигналы: СВ - суммирование-вычитание для управления по выполнению операций суммирование или вычитание и УМН - умножение для выполнения операции произведение чисел. Из блока 23 сумматора-вычитателя выходной управляющий сигнал ЗрОСТ - знаковый разряд остатка - поступает на вход блока 21 формирования знакового разряда и на вход блока 25 регистра результата для определения признака операции - сигнала СВ и очередной цифры частного при выполнении операции деление. Выходным управляющим сигналом блока 23 сумматора-вычитателя является сигнал ЗЗР - знаковый разряд, который поступает на вход блока 21 для формирования окончательного знака результата. Выходной сигнал блока 23 сумматора-вычитателя ОСТ - остаток - поступает на вход блока 22 регистра первого числа, формирование этого сигнала необходимо при выполнении операции деления. Выходной информационный сигнал РЕЗ является результатом операций, который поступает на вход блока 25 регистра результата. Выходным информационным сигналом блока 25 регистра результата является сигнал РФЗ - результат с фиксированной запятой. С входа блока 22 регистра первого числа на вход блока 26 управления операциями с фиксированной запятой поступает управляющий сигнал ПДЧ - признак дробной части при делении, который является признаком конца целой части двоичного первого числа. При поступлении этого сигнала на блок управления необходимо установить знак, отделяющий целую часть числа от дробной в блоке 25 регистра результата. На вход блока 25 регистра результата поступает с выхода блока 26 управления операциями с фиксированной запятой признак целой и дробной части результата при делении - ЦДЧ, который формирует позицию, отделяющую целую часть от дробной (точку или запятую). На вход блока 21 формирования знакового разряда поступает информационный сигнал КОП - код операции сложения, вычитания, умножения и деления, этот сигнал поступает на вход блока 26 управления операциями с фиксированной запятой для анализа и генерации соответствующих управляющих сигналов, поступающих на входы блоков. С выхода блока 24 регистра второго числа выходит управляющий сигнал РМН, соответствующий значению двоичного разряда второго числа при выполнении операции умножения вычислителем, который поступает на вход блока 22 регистра первого числа. При РМН, равном нулю, происходит сдвиг двоичного числа блока 22 регистра первого числа на один разряд влево, если сигнал РМН равен единице, то блок 23 суммирования-вычитания принимает значение из блока 22 регистра первого числа. Выходной управляющий сигнал ППР - признак пустого регистра - поступает на вход блока 26 управления операциями с фиксированной запятой. Этот сигнал принимает значение единицы, если в регистре второго числа имеется хотя бы один двоичный разряд, равный единице. Внешними входными сигналами блока 26 управления операциями с фиксированной запятой являются управляющие сигналы: РРБФЗ - разрешения работы блока операций с фиксированной запятой и КРБФЗ - конец работы блока операций с фиксированной запятой (фиг.5).

Блок 16 операций с плавающей запятой БОПЗ выполняет арифметические операции с плавающей запятой как с порядками, так и мантиссами двоичных чисел (фиг.3, 6). Этот блок состоит из двух блоков: 1) блока 27 определения операций порядков с плавающей запятой - БОПРПЗ, в котором выполняются арифметические операции над порядками двоичных чисел, 2) блока 28 определения операций мантисс с плавающей запятой - БОМПЗ, в котором выполняют