Способ и устройство для канального кодирования и декодирования в системе связи, в которой используются коды контроля четности с низкой плотностью

Иллюстрации

Показать всеИзобретение относится к системе связи, использующей коды Контроля Четности с Низкой Плотностью (Low-Density Parity-Check, LDPC), и, в частности, к устройству и способу канального кодирования/декодирования для генерации LDPC-кодов с разными длинами кодового слова и разными скоростями кодирования из LDPC-кода, заданного в модуляции высшего порядка. Техническим результатом является повышение производительности канального кодирования/декодирования в системе связи, где применяются LDPC-коды. Указанный результат достигается тем, что в способе кодирования определяют схему модуляции для передачи символа; определяют шаблон сокращения с учетом определенной схемы модуляции; группируют столбцы, соответствующие информационному слову в матрице контроля четности LDPC-кода в множество групп столбцов; упорядочивают группы столбцов; определяют диапазон результирующего информационного слова, который желательно получить посредством сокращения информационного слова; на основании диапазона результирующего информационного слова выполняют сокращение группы столбцов за группой столбцов в упорядоченных группах столбцов информационного слова согласно определенному шаблону сокращения; и выполняют LDPC-кодирование сокращенного информационного слова. 13 н. и 24 з.п. ф-лы, 18 ил., 3 табл.

Реферат

Область техники

Настоящее изобретение относится в общем к системе связи, использующей коды Контроля Четности с Низкой Плотностью (Low-Density Parity-Check, LDPC), и, в частности, к устройству и способу канального кодирования/декодирования для генерации LDPC-кодов с разными длинами кодового слова и разными скоростями кодирования из LDPC-кода, заданного в модуляции высшего порядка.

Уровень техники

В системах беспроводной связи производительность линии значительно ухудшается из-за различных шумов в каналах, явления замирания и Межсимвольных Помех (Inter-Symbol Interference, ISI). Следовательно, чтобы предоставить высокоскоростные системы цифровой связи, которые требуют большой пропускной способности и высокой надежности, например, для систем мобильной связи следующего поколения, систем цифрового вещания и портативного Интернета, важно разработать технологии для преодоления канальных шумов, замирания и ISI. В последнее время проводятся обширные исследования в области кодов с коррекцией ошибок, которые рассматриваются как способ для повышения надежности связи посредством эффективного восстановления искаженной информации.

LDPC-код, который представляет собой некоторый вид кода с коррекцией ошибок, обычно определяется матрицей контроля четности, и он может быть выражен, используя двудольный граф, который называют графом Таннера. Термин "двудольный граф" обозначает граф, у которого вершины, составляющие граф, разделены на два разных типа, и LDPC-код представляется как двудольный граф, состоящий из вершин, некоторые из которых называются переменными узлами, а другие называются контрольными узлами. Переменные узлы взаимно-однозначно сопоставляются кодированным битам.

Фиг.1 представляет собой иллюстрацию примера матрицы H1 контроля четности LDPC-кода, содержащей 4 строки и 8 столбцов.

Ссылаясь на Фиг.1, поскольку количество столбцов составляет 8, матрица H1 контроля четности является LDPC-кодом, который генерирует кодовое слово длиной 8, и столбцы сопоставляются 8 кодированным битам.

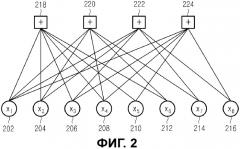

Фиг.2 представляет собой иллюстрацию графа Таннера, соответствующего матрице H1 контроля четности с Фиг.1.

Ссылаясь на Фиг.2, граф Таннера для LDPC-кода включает в себя 8 переменных узлов x1 (202), x2 (204), x3 (206), x4 (208), x5 (210), x6 (212), x7 (214) и x8 (216), а также 4 контрольных узла 218, 220, 222 и 224. i-й столбец и j-я строка матрицы H1 контроля четности LDPC-кода сопоставляются переменному узлу xi и j-му контрольному узлу, соответственно. Кроме того, величина 1, то есть ненулевая величина в точке, где пересекаются i-й столбец и j-я строка в матрице H1 контроля четности LDPC-кода, указывает, что существует ребро между переменным узлом x1 и j-м контрольным узлом в графе Таннера с Фиг.2.

В графе Таннера для LDPC-кода степень переменного узла и контрольного узла указывает количество ребер, присоединенных к каждому соответствующему узлу, и эта степень равна количеству ненулевых элементов в столбце или строке, соответствующей подходящему узлу в матрице контроля четности LDPC-кода. Например, ссылаясь на Фиг.2, степени переменных узлов x1 (202), x2 (204), x3 (206), x4 (208), x5 (210), x6 (212), x7 (214) и x8 (216) равны 4, 3, 3, 3, 2, 2, 2 и 2, соответственно, а степени контрольных узлов 218, 220, 222 и 224 равны 6, 5, 5 и 5, соответственно. Кроме того, количества ненулевых элементов в столбцах матрицы H1 контроля четности с Фиг.1, которые соответствуют переменным узлам с Фиг.2, совпадают с их степенями 4, 3, 3, 3, 2, 2, 2 и 2, а количества ненулевых элементов в строках матрицы H1 контроля четности с Фиг.1, которые соответствуют контрольным узлам с Фиг.2, совпадают с их степенями 6, 5, 5 и 5.

Чтобы выразить распределение степени для узлов LDPC-кода, отношение количества переменных узлов со степенью i к общему количеству переменных узлов определяется как fi, а отношение количества контрольных узлов со степенью j к общему количеству контрольных узлов определяется как gj. Например, для LDPC-кода, соответствующего Фиг.1 и 2, f2=4/8, f3=3/8, f4=1/8 и fi=0 для i≠2, 3, 4, и g5=3/4, g6=1/4 и gj=0 для j≠5, 6. Когда длина LDPC-кода определена как N, то есть количество столбцов равно N, и когда количество строк определено как N/2, плотность ненулевых элементов во всей матрице контроля четности с вышеупомянутым распределением степени вычисляется согласно Уравнению (1).

В Уравнении (1) по мере увеличения N плотность элементов "1" в матрице контроля четности уменьшается. В целом для LDPC-кода, поскольку длина N кодового слова обратно пропорциональна плотности ненулевых элементов, LDPC-код с большим значением N имеет очень низкую плотность ненулевых элементов. Термин "низкая плотность" в названии LDPC-кода берет начало из вышеупомянутой связи.

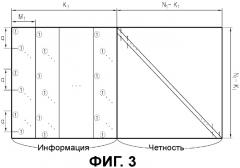

Фиг.3 представляет собой схематическую иллюстрацию LDPC-кода, применяемого в качестве стандартного способа во 2-м Поколении Спутниковой Передачи - Цифрового Видео Вещания (Digital Video Broadcasting-Satellite Transmission 2nd Generation, DVB-S2), который является одним из Европейских стандартов цифрового вещания.

На Фиг.3, N 1 и K 1 обозначают длину кодового слова и длину информации (или длину информационного слова) LDPC-кода, соответственно, а (N 1 -K 1 ) предоставляет длину контроля по четности. Кроме того, целые M1 и q удовлетворяют равенству q=(N1-K1)/M1. Предпочтительно, величина K1/M1 является целой. Ссылаясь на Фиг.3, структура части контроля четности, то есть с K-го столба по (N 1-1)-й столбец в матрице контроля четности имеет двойную диагональную форму. Следовательно, что касается распределения степени по столбцам, соответствующим части контроля четности, то все столбцы имеют степень "2", за исключением последнего столба, который имеет степень "1".

В матрице контроля четности, структура информационной части, то есть с 0-го столбца по (K 1-1)-й столбец, формируется с применением следующих правил.

Правило 1: Генерируется всего K 1 /M 1 групп столбцов посредством группирования K 1 столбцов, соответствующих информационному слову в матрице контроля четности, во множество групп, каждая из которых включает в себя M 1 столбцов. Способ для формирования столбцов в каждой группе определяется нижеизложенным Правилом 2.

Правило 2: Сначала определяются позиции элементов "1" в каждом 0-м столбце в i-й группе столбцов (где i=1,…, K 1 /M 1 ). Степень 0-го столбца в каждой i-й группе столбцов обозначается как D i, если позициями столбцов с 1 являются ,,…, , то позиции (k=1, 2,…, D i) строк с 1 определяются согласно Уравнению (2) в j-м столбце (где j=1,2,…, M 1-1) в i-й группе столбцов.

(2)

Из вышеизложенных правил следует, что степени всех столбцов из i-й группы столбцов равны D i. Для лучшего понимания структуры DVB-S2 LDPC-кода, который хранит информацию о матрице контроля четности согласно вышеупомянутым правилам, ниже приведено подробное описание одного примера.

Для подробного примера для N 1=30, K 1=15, M 1=5 и q=3, три последовательности для информации о позициях строк с элементами "1" для 0-х столбцов в 3 группах столбцов могут быть выражены следующим образом. Так, эти последовательности называются "последовательностями позиций с весовым коэффициентом 1".

Что касается последовательности позиций с весовым коэффициентом 1 для 0-х столбцов в каждой группе столбцов, то для каждой группы столбцов только соответствующие последовательности позиций могут быть выражены следующим образом. Например:

0 1 2

0 11 13

0 10 14.

Иначе говоря, i-я последовательность позиций с весовым коэффициентом 1 в i-й линии последовательно представляет информацию о позициях строк с элементом "1" для i-й группы столбцов.

Можно сгенерировать LDPC-код с концепцией, соответствующей DVB-S2 LDPC-коду, иллюстрированному Фиг.4, посредством формирования матрицы контроля четности посредством информации, соответствующей упомянутому подробному примеру и Правилам 1 и 2.

Известно, что DVB-S2 LDPC-код, созданный согласно Правилу 1 и Правилу 2, может быть эффективно закодирован посредством структурной формы. Ниже в качестве примера описаны последовательные этапы процесса выполнения LDPC-кодирования, используя матрицу контроля четности на основе DVB-S2.

В следующем описании DVB-S2 LDPC-код с N 1=16200, K 1 =10800, M 1=360 и q=15 подвергается процессу кодирования. Для удобства информационные биты с длиной K i представлены как , а биты четности с длиной (N 1 -K 1 ) представлены как .

Этап 1: LDPC-код инициализирует биты четности следующим образом:

Этап 2: LDPC-кодер считывает информацию по строке, где элемент "1" расположен в группе столбцов из 0-й последовательности позиций с весовым коэффициентом 1 среди сохраненных последовательностей, указывающих матрицу контроля четности.

0 2084 1613 1548 1286 1460 3196 4297 2481 3369 3451 4620 2622

LDPC-кодер обновляет конкретные биты p x четности согласно Уравнению (3), используя считанную информацию и первый информационный бит i 0 . Здесь, x представляет собой величину для k = 1,2,…,13.

В Уравнении (3), p x = p x ⊕i 0 также может быть выражено как p x ←⊕i 0 , где ⊕ представляет бинарное суммирование.

Этап 3: LDPC-кодер определяет значение по Уравнению (4) для следующих 359 информационных битов im (где m=1, 2,…, 359) после i 0 .

В Уравнении (4), x представляет собой величину для (k = 1, 2,…, 13). Следует отметить, что Уравнение (4) следует той же концепции, что и Уравнение (2).

Далее, LDPC-кодер выполняет операцию, похожую на Уравнение (3), используя величину, полученную в Уравнении (4). То есть LDPC-кодер обновляет биты четности для i m. Например, для m=1, то есть для i 1 LDPC-кодер обновляет биты четности как задано в Уравнении (5).

В Уравнении (5) q=15. LDPC-кодер аналогичным образом выполняет вышеописанный процесс для m=1, 2,…, 359.

Этап 4: Как и на Этапе 2, LDPC-кодер считывает информацию 1-й последовательности (k=1, 2,…, 13) позиций с весовым коэффициентом 1 для 361-го информационного бита i 360 и обновляет конкретный p x, где величина x равна . LDPC-кодер обновляет , m=361, 362,…, 719, посредством аналогичного применения Уравнения (4) к следующим 359 информационным битам i 361, i 362,…, i 719 после i 360.

Этап 5: LDPC-кодер повторяет Этапы 2, 3 и 4 для всех групп, каждая из которых имеет 360 информационных битов.

Этап 6: LDPC-кодер определяет биты четности, используя Уравнение (6).

(6)

Биты p i четности в Уравнении (6) были подвергнуты LDPC-кодированию.

Как описано выше, DVB-S2 выполняет кодирование, как описано на Этапах 1-6.

Раскрытие изобретения

Техническая проблема

Для применения LDPC-кода к действительной системе связи этот LDPC-код должен быть разработан так, чтобы подходить под запрошенную скорость передачи данных в системе связи. В частности, LDPC-коды с разными длинами кодовых слов необходимы для поддержки разных скоростей передачи данных согласно системным требованиям в адаптивных системах связи, применяющих Гибридный Автоматический Запрос Повторной Передачи (Hybrid Automatic Retransmission Request, HARQ) и Адаптивную Модуляцию и Кодирование (Adaptive Modulation and Coding, AMC), а также и в других системах связи, поддерживающих разные службы вещания.

Тем не менее, как описано выше, LDPC-код, используемый в системе DVB-S2, имеет только два типа длины кодового слова из-за ограниченного применения, и каждый тип LDPC-кода использует независимую матрицу контроля четности. Соответственно, в области техники существует давно ощущаемая необходимость в способе поддержки разных длин кодового слова, чтобы повысить расширяемость и гибкость системы. Так, в системе DVB-S2 для передачи информации сигнализации требуется передача данных объемом от сотен до тысяч битов. Тем не менее, поскольку для длины DVB-S2 LDPC-кода доступно только два варианта - 16200 и 64800, все же есть необходимость в поддержке разных длин кодовых слов. Тем не менее, поскольку хранение независимых матриц контроля четности для каждой длины кодового слова LDPC-кода может сократить общую эффективность памяти, также существует необходимость в схеме, обеспечивающей эффективную поддержку разных длин кодового слова из заданной существующей матрицы контроля четности, без необходимости в новой матрице контроля четности.

Отмечено, что надежности битов, включенных в символы модуляции высшего порядка, различаются, когда в системе связи, требующей LDPC-коды с разными длинами кодового слова, используется модуляция высшего порядка, в отличие от случаев, когда модуляция высшего порядка применяется в системе связи, в которой используется только Двоичная Фазовая Манипуляция (Binary Phase Shift Keying, BPSK) или Квадратурная Фазовая Манипуляция (Quadrature Phase Shift Keying, QPSK).

Для демонстрации различия надежности в модуляции высшего порядка ниже предоставлено описание сигнальных совокупностей для Квадратурной Амплитудной Модуляции (Quadrature Amplitude Modulation, QAM), которая представляет собой модуляцию высшего порядка, обычно используемую в системах связи. QAM-модулированный символ включает в себя действительную часть и мнимую часть, и разные символы модуляции могут быть сгенерированы посредством дифференциации амплитуды и знаков их действительных и мнимых частей. QAM описана вместе с QPSK-модуляцией, чтобы более ясно предоставить детали характеристик QAM.

Фиг.5(a) представляет собой схематическую иллюстрацию сигнальной совокупности для обычной QPSK-модуляции.

Ссылаясь на Фиг.5(a), y0 определяет знак действительной части, тогда как y1 определяет знак мнимой части. То есть знак действительной части будет плюсом (+) для y0=0 и минусом (-) для y0=1. Кроме того, знак мнимой части будет плюсом (+) для y1=0 и минусом (-) для y1=1. Поскольку y0 и y1 равны в терминах вероятности возникновения ошибки, поскольку они представляют собой биты индикации знака, которые указывают соответствующие знаки действительной части и мнимой части, надежности битов (y0, y1), соответствующих одному сигналу модуляции, равны при QPSK-модуляции. Для y0,q и y1,q второй нижний индекс q указывает q-й вывод битов, включенных в сигнал модуляции.

Фиг.5(b) представляет собой схематическую иллюстрацию сигнальной совокупности для обычной 16-QAM-модуляции.

Ссылаясь на Фиг.5(b), (y0, y1, y2, y3) соответствуют битам одного сигнала модуляции. В частности, биты y0 и y2 определяют знак и амплитуду действительной части, соответственно, тогда как биты y1 и y3 определяют знак и амплитуду мнимой части, соответственно. То есть y0 и y1 определяют знаки действительной части и мнимой части сигнала модуляции, а y2 и y3 определяют амплитуды действительной части и мнимой части сигнала модуляции. Поскольку различить знак модулированного сигнала проще, чем различить амплитуду модулированного сигнала, y2 и y3 выше, чем y0 и y1 по вероятности возникновения ошибки. Следовательно, в терминах вероятности отсутствия ошибок (то есть надежностей) битов: y0 = y1 > y2 = y3. То есть биты (y0, y1, y2, y3), включенные в сигнал QAM-модуляции, в отличие от сигнала QPSK-модуляции имеют разные надежности.

При 16-QAM-модуляции среди 4 битов, образующих сигнал, 2 бита определяют знаки действительной части и мнимой части сигнала, а остальные 2 бита требуются только для определения амплитуды действительной части и мнимой части сигнала. Таким образом, порядки (y0, y1, y2, y3) и роль каждого бита подвержены изменению.

Фиг.5(c) представляет собой схематическую иллюстрацию сигнальной совокупности для обычной 64-QAM-модуляции.

Среди (y0, y1, y2, y3, y4, y5), которые соответствуют битам одного сигнала модуляции, биты y0, y2 и y4 определяют амплитуду и знак действительной части, а биты y1, y3 и y5 определяют амплитуду и знак мнимой части. Так, y0 и y1 определяют знаки действительной части и мнимой части, соответственно, а комбинация y2 и y4 и комбинация y3 и y5 определяют амплитуду действительной части и мнимой части, соответственно. Как описано выше, поскольку различить знаки модулированного сигнала легче, чем различить амплитуды модулированного сигнала, надежности y0 и y1 выше, чем надежности y2, y3, y4 и y5.

Биты y2 и y3 определяются в зависимости от того, больше или меньше ли амплитуда модулированного символа чем 4, а биты y4 и y5 определяются согласно тому, ближе ли амплитуды модулированного символа к значению 4 или значению 0, где значение 2 располагается между ними, или к значению 4 или значению 8, где значение 6 располагается между ними. Соответственно, диапазон, в котором величина определяется посредством y2 и y3 составляет 4, тогда как диапазон для y4 и y5 составляет 2. Следовательно, y2 и y3 выше по надежности, чем y4 и y5. Следовательно, в терминах вероятности отсутствия ошибок (то есть надежностей) битов y0=y1 > y2=y3 > y4=y5.

При 64-QAM-модуляции среди 6 битов, образующих сигнал, 2 бита определяют знаки действительной части и мнимой части сигнала, а остальные 4 бита требуются только для определения амплитуды действительной части и мнимой части сигнала. Таким образом, порядки (y0, y1, y2, y3, y4, y5) и роль каждого бита подвержены изменению. Даже в сигнальной совокупности при 256-QAM или выше роли и надежности битов, образующих сигнал модуляции, отличаются, как описано выше. Соответственно, подробное описание этого случая опущено.

Резюмируя, можно отметить, что при BPSK или QPSK-модуляции нет необходимости рассматривать схему модуляции, когда определяются шаблоны сокращения или прокалывания, поскольку надежности битов, включенных в символ, равны, то также равны надежности битов кодового слова LDPC, которое было подвергнуто сокращению или прокалыванию. Тем не менее, при модуляции высшего порядка, такой как 16-QAM, 64-QAM и 256-QAM, поскольку роли и надежности битов, включенных в символ, отличаются, когда определяется схема модуляции и схема сопоставления сигнальной совокупности/бита (сопоставления бита по сигнальной совокупности), надежности каждого бита в кодовом слове LDPC, после того как оно подвергается сокращению или прокалыванию, может отличаться от надежности кодового слова LDPC, до того как оно было подвергнуто сокращению или прокалыванию.

Следовательно, существует необходимость в устройстве и способе для генерации LDPC-кода с использованием сокращения или прокалывания с учетом модуляции высшего порядка.

Техническое решение

Соответственно, настоящее изобретение было сделано с целью решения, по меньшей мере, упомянутых проблем и/или недостатков и обеспечения, по меньшей мере, нижеописанных преимуществ. Соответственно, одной целью настоящего изобретения является предоставление способа и устройства канального кодирования/декодирования для генерации из заданного LDPC-кода нового LDPC-кода с другой длиной кодового слова посредством применения сокращения или прокалывания, которое определяется с учетом модуляции высшего уровня в системе связи, и для кодирования и декодирования канала с использованием сгенерированного LDPC-кода в системе связи.

Еще одной целью настоящего изобретения является предоставление способа и устройства канального кодирования/декодирования для обеспечения оптимальной производительности относительно структуры DVB-S2 в системе связи, где применяются LDPC-коды.

Согласно одному аспекту настоящего изобретения предоставлен способ для кодирования канала в системе связи, в которой используется код Контроля Четности с Низкой Плотностью (LDPC), в котором определяют схему модуляции для символа, группируют столбцы, соответствующие информационному слову в матрице контроля частности LDPC-кода, во множество групп столбцов, упорядочивают эти группы столбцов, определяют диапазон информационного слова, который должен быть получен посредством сокращения, выполняют сокращение группы столбцов за группой столбцов над группой столбцов в порядке согласно шаблону сокращения, определенному с учетом определенной схемы модуляции на основании диапазона информационного слова, и сокращенное информационное слово подвергают LDPC-кодированию.

Согласно еще одному аспекту настоящего изобретения предоставлено устройство для кодирования канала в системе связи, в которой применяется код Контроля Четности с Низкой Плотностью (LDPC). Это устройство включает в себя блок извлечения матрицы контроля четности для определения схемы модуляции передачи символа, для группирования столбцов, соответствующих информационному слову в матрице контроля четности LDPC-кода, во множество групп столбцов, и для упорядочивания этих групп столбцов, блок применения шаблона сокращения для определения диапазона информационного слова, которое требуется получить посредством сокращения, и на основании диапазона информационного слова для выполнения сокращения группы столбцов за группой столбцов в порядке согласно шаблону сокращения, определенному с учетом определенной схемы модуляции, и LDPC-кодер для выполнения LDPC-кодирования сокращенного информационного слова.

Согласно еще одному аспекту настоящего изобретения предоставлен способ для декодирования канала в системе связи, в которой используется код Контроля Четности с Низкой Плотностью (LDPC), в котором демодулируют сигнал, переданный из передатчика, определяют, присутствует ли, по меньшей мере, один сокращенный бит в этом демодулированном сигнале, определяют позицию сокращенного информационного бита посредством оценки информации о шаблоне сокращения, когда присутствует, по меньшей мере, один сокращенный бит, и данные декодируют с использованием определенной позиции сокращенного информационного бита. Информация о шаблоне сокращения включает в себя шаблон сокращения, определенный с учетом схемы модуляции.

Согласно еще одному аспекту настоящего изобретения предоставлено устройство для декодирования канала в системе связи, в которой используется код Контроля Четности с Низкой Плотностью (LDPC), причем это устройство включает в себя блок оценки шаблона сокращения для демодулирования сигнала, переданного из передатчика, для определения того, присутствует ли, по меньшей мере, один сокращенный бит в демодулированном сигнале, и, если присутствует, по меньшей мере, один сокращенный бит, для определения позиции сокращенного информационного бита посредством оценки информации о шаблоне сокращения, и декодер для декодирования данных, используя определенную позицию сокращенного информационного бита. Информация о шаблоне сокращения включает в себя шаблон сокращения, определенный с учетом схемы модуляции.

Полезные эффекты

Настоящее изобретение может генерировать отдельный LDPC-код с разной длиной кодового слова, используя информацию о матрице контроля четности, заданной в системе связи, в которой используется модуляция высшего порядка и LDPC-код.

В добавление, варианты осуществления настоящего изобретения могут выполнять сокращение, используя разные шаблоны сокращения согласно схемам модуляции.

Краткое описание чертежей

Вышеупомянутые и другие аспекты, отличительные признаки и преимущества определенных вариантов осуществления настоящего изобретения будут очевидны из следующего подробного описания с сопутствующими чертежами, на которых:

Фиг.1 - иллюстрация примера матрицы контроля четности LDPC-кода длиной 8;

Фиг.2 - иллюстрация графа Таннера для матрицы контроля четности LDPC-кода длиной 8;

Фиг.3 - иллюстрация схематической структуры DVB-S2 LDPC-кода;

Фиг.4 - иллюстрация примера матрицы контроля четности DVB-S2 LDPC-кода;

Фиг.5(a) - схематическая иллюстрация сигнальной совокупности для обычной QPSK-модуляции, используемой в цифровой системе связи;

Фиг.5(b) - схематическая иллюстрация сигнальной совокупности для обычной 16-QAM-модуляции, используемой в цифровой системе связи;

Фиг.5(c) - схематическая иллюстрация сигнальной совокупности для обычной 64-QAM-модуляции, используемой в цифровой системе связи;

Фиг.6 - иллюстрация структурной схемы приемопередатчика в системе связи, в которой используется LDPC-код;

Фиг.7(a) - иллюстрация примера сопоставления сигнальной совокупности/бита при 16-QAM-модуляции;

Фиг.7(b) - иллюстрация примера сопоставления сигнальной совокупности/бита, которое было модифицировано посредством сокращения при 16-QAM-модуляции;

Фиг.8(a) - иллюстрация примера сопоставления сигнальной совокупности/бита при 64-QAM-модуляции;

Фиг.8(b) - иллюстрация примера сопоставления сигнальной совокупности/бита, которое было модифицировано посредством сокращения при 64-QAM-модуляции;

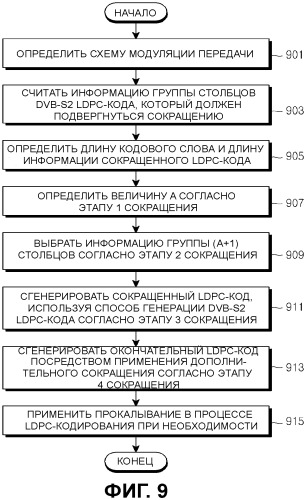

Фиг.9 - иллюстрация процедуры для генерации LDPC-кода с разной длиной кодового слова из матрицы контроля четности сохраненного LDPC-кода согласно одному варианту осуществления настоящего изобретения;

Фиг.10 - иллюстрация структурной схемы передающего устройства, в котором применяется предлагаемый сокращенный LDPC-код, согласно одному варианту осуществления настоящего изобретения;

Фиг.11 - иллюстрация структурной схемы передающего устройства, в котором применяется предлагаемый сокращенный/проколотый LDPC-код, согласно одному варианту осуществления настоящего изобретения;

Фиг.12 - иллюстрация структурной схемы приемного устройства, в котором используется LDPC-код, к которому применяется предлагаемое сокращение, согласно одному варианту осуществления настоящего изобретения;

Фиг.13 - иллюстрация структурной схемы приемного устройства, в котором используется LDPC-код, к которому применяется предлагаемое сокращение и прокалывание, согласно одному варианту осуществления настоящего изобретения; и

Фиг.14 - иллюстрация схемы последовательности операций, иллюстрирующей процесс приема в приемном устройстве согласно одному варианту осуществления настоящего изобретения.

Во всех чертежах одинаковые позиционные обозначения относятся к одинаковым элементам, признакам и структурам.

Вариант осуществления

Нижеприведенное описание в сочетании с прилагаемыми чертежами предназначено для помощи в полном понимании вариантов осуществления настоящего изобретения, как определено формулой изобретения и ее эквивалентами. Оно включает в себя различные конкретные детали, которые помогают понять изобретение, однако эти конкретные детали не должны рассматриваться как ограничения. Соответственно, специалистам в данной области техники будет очевидно, что в рамках объема и сущности настоящего изобретения могут быть выполнены различные изменения и модификации описанных вариантов осуществления. К тому же описание известных функций и конструкций опущено для краткости и ясности.

Сверх того, термины и слова, использованные в следующем описании и формуле изобретения, не ограничиваются библиографическими значениями, и они использовались настоящим изобретателем, чтобы обеспечить ясное и последовательное понимание настоящего изобретения. Соответственно, специалистам в данной области техники будет очевидно, что следующее описание вариантов осуществления настоящего изобретения предоставлено только в целях иллюстрации, а не в целях ограничения изобретения, как определено прилагаемой формулой изобретения и ее эквивалентами.

Следующее описание вариантов осуществления настоящего изобретения предоставляет способ для поддержки LDPC-кодов с разными длинами кодового слова, подходящими для модуляции высшего порядка, используя матрицу контроля четности структурированного LDPC-кода определенного типа. В добавление, описание вариантов осуществления настоящего изобретения предоставляет устройство для поддержки разных длин кодового слова согласно модуляции высшего порядка в системе связи, в которой используется LDPC-код определенного типа, и способ для управления таким устройством. В частности, описание вариантов осуществления настоящего изобретения предоставляет способ для генерации LDPC-кода, используя матрицу контроля четности заданного LDPC-кода, где сгенерированный LDPC-код меньше, чем заданный LDPC-код, а также соответствующее устройство.

Фиг.6 представляет собой структурную схему приемопередатчика в системе связи, в которой используется LDPC-код.

Ссылаясь на Фиг.6, сообщение u вводится в LDPC-кодер 611 в передатчике 610 до выполнения его передачи в приемник 630. LDPC-кодер 611 кодирует введенное сообщение u и выводит кодированный сигнал c в модулятор 613. Модулятор 613 модулирует кодированный сигнал c и передает модулированный сигнал s в приемник 630 через беспроводной канал 620. Демодулятор 631 в приемнике 630 демодулирует принятый сигнал r и выводит демодулированный сигнал x в LDPC-декодер 633. LDPC-декодер 633 декодирует демодулированный сигнал x, в результате чего получается оценка u сообщения, основанного на данных, которые были приняты через беспроводной канал 620.

Используя предопределенную схему, LDPC-кодер 611 генерирует матрицу контроля четности согласно длине кодового слова, необходимой для системы связи. В частности, согласно одному варианту осуществления настоящего изобретения LDPC-кодер 611 будет поддерживать разные длины кодового слова, используя LDPC-код без отдельной необходимости дополнительной сохраненной информации.

Согласно одному варианту осуществления настоящего изобретения в способе получения разных длин кодового слова из заданного LDPC-кода используется способ сокращения и/или способ прокалывания. В настоящее время известны способы, которые оптимизируют производительность посредством применения сокращения или прокалывания к LDPC-коду согласно кодовой скорости и длине кодового слова. Тем не менее в большинстве случаев, поскольку известный способ определения шаблонов сокращения и прокалывания выполняет процесс оптимизации с учетом только Двоичной Фазовой Манипуляции (Binary Phase Shift Keying, BPSK) или Квадратурной Фазовой Манипуляции (Quadrature Phase Shift Keying, QPSK), для заданного LDPC-кода может существовать только один оптимизированный шаблон сокращения и/или прокалывания.

Тем не менее шаблоны прокалывания и сокращения, оптимизированные для схемы сопоставления сигнальной совокупности/бита, определенной в модуляции высшего порядка, могут отличаться от таковых для BPSK или QPSK-модуляции.

При BPSK или QPSK-модуляции, поскольку надежности битов, включенных в символ, равны, надежности битов кодового слова LDPC, после того как оно подвергается сокращению или прокалыванию, также равны. Следовательно, нет необходимости учитывать схему модуляции при определении шаблонов сокращения и прокалывания. Тем не менее, как описано выше, при модуляции высшего порядка, такой как 16-QAM, 64-QAM и 256-QAM, поскольку надежности битов, включенных в символ, отличаются, когда определена схема модуляции и схема сопоставления сигнальной совокупности/бита, надежности каждого бита в кодовом слове LDPC, после того как оно подвергается сокращению или прокалыванию, могут отличаться от надежности кодового слова LDPC, до того как оно было подвергнуто сокращению или прокалыванию.

Фиг.7(a), 7(b), 8(a) и 8(b) иллюстрируют примеры сопоставления битов, где биты сопоставляются символу согласно степеням переменных узлов в кодовом слове LDPC для 16-QAM и 64-QAM, соответственно. В частности, Фиг.7(a) иллюстрирует пример сопоставления сигнальной совокупности/бита при 16-QAM-модуляции, а Фиг.7(b) иллюстрирует пример сопоставления сигнальной совокупности/бита, которое было модифицировано посредством сокращения при 16-QAM-модуляции. Для удобства кодовое слово LDPC разделено на 8-битные или 12-битные блоки.

Ссылаясь на Фиг.7(a), y0 и y1, указывают биты с высокой надежностью, которые определяют знаки действительной части и мнимой части в символе 16-QAM, соответственно. То есть отношение надежности между этими битами выражается как y0=y1 >y2=y3. На Фиг.7(a), поскольку y1 и y3 сопоставляются части кодового слова LDPC, которая соответствует переменным узлам наивысшей степени, 1/2 переменных узлов наивысшей степени сопоставляются части с высокой надежностью, а другая 1/2 сопоставляются части с низкой надежностью.

Предполагая, что половина переменных узлов наивысшей степени была подвергнута сокращению, как проиллюстрировано на Фиг.7(b), когда биты символа, соответствующие несокращенным переменным узлам наивысшей степени рассматриваются в сокращенном кодовом слове LDPC, 7/8 переменных узлов наивысшей степени сопоставляется y3, а 1/8 сопоставляется y1. То есть битовое отношение сильно отличается до и после сокращения.

Аналогично, Фиг.8(a) иллюстрирует пример сопоставления сигнальной совокупности/бита при 64-QAM-модуляции, а Фиг.8(b) иллюстрирует пример сопоставления сигнальной совокупности/бита, которое было модифицировано посредством сокращения при 64-QAM-модуляции.

На Фиг.8(a), отношение надежности между битами, включенными в символ, выражается как y0=y1 > y2=y3 > y4=y5. В этом случае, 1/3 переменных узлов с наивысшей степенью в кодовом слове LDPC сопоставляются биту y5 с наименьшей надежностью. Тем не менее, когда 2/3 переменных узлов наивысшей степени подвергаются сокращению, как проиллюстрировано на Фиг.8(b), 5/6 остальных несокращенных переменных узлов наивысшей степени сопоставляются биту y5 с наименьшей надежностью, так что битовое отношение отличается до и после сокращения.

Когда, как описано здесь, для заданного LDPC-кода фиксируются схема модуляции высшего порядка и схема сопоставления сигнальной совокупности/бита, шаблон сокращения или прокалывания, используемый в BPSK или QPSK-модуляции, может быть непригоден, поскольку отношение бита кодового слова LDPC, сопоставляемого каждому биту символа модуляции, сильно отличается согласно способу сокращения.

Известно, что в случае LDPC-кода распределение степени матрицы контроля четности оптимизированного LDPC-кода очень отличается согласно схеме модуляции. То есть распределение степени LDPC-кода, оптимизированного для BPSK или QPSK-модуляции и распределение степени LDPC-кодов, оптимизированных для 16-QAM, 64-QAM и 256-QAM, отличаются друг от друга.

По схожим причинам очевидно, что когда предполагается, что задан LDPC-код с одним распределением степени, оптимизированный шаблон сокращения или прокалывания отличается согласно схеме модуляции высшего порядка. Соответственно, шаблон сокращения должен быть определен с учетом целевой схемы модуляции, чтобы найти оптимизированный шаблон сокращения или прокалывания для LDPC-кода.

Описание сокращения приведено ниже, до описания способа определения шаблона сокращения или прокалывания с учетом схемы модуляции. Термин "сокращение" обозначает способ, согласно которому, по существу, не передается специфицированная часть кодового слова LDPC после генерации кодового