Отказоустойчивая вычислительная система с аппаратно-программной реализацией функций отказоустойчивости и динамической реконфигурации

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники, а именно к информационным системам, и может быть использовано при построении высоконадежных вычислительных и управляющих систем, предназначенных для решения задач управления бортовыми системами транспортного корабля. Техническим результатом является увеличение быстродействия и автоматизация процесса реконфигурации в отказоустойчивых системах. Отказоустойчивая вычислительная система с аппаратно-программной реализацией функций отказоустойчивости и динамической реконфигурации содержит первую, вторую, третью и четвертую вычислительные машины (ВМ), соединенные первой, второй, третьей и четвертой последовательными шинами данных, первый, второй, третий и четвертый вторичные источники питания (ВИП), первый, второй, третий и четвертый контроллеры межмашинного обмена (КММО), первый, второй, третий и четвертый контроллеры управления конфигурацией (КУК). 13 з.п. ф-лы, 34 ил.

Реферат

Изобретение относится к области вычислительной техники и может использоваться при построении высоконадежных вычислительных и управляющих систем, предназначенных для решения задач управления бортовыми системами транспортного корабля.

Известна компьютерная система [1], исправляющая одиночную ошибку, которая содержит первый системный модуль с первым процессором, с шиной первого процессора и первой шиной I/O (входа/выхода), второй системный модуль со вторым процессором, с шиной второго процессора и второй шиной I/O, третий системный модуль с третьим процессором, с шиной третьего процессора и третьей шиной I/O, причем первый модуль системы включает первую память, первый процессор, первый блок управления I/O, первый мост, сравнивающий данные первой процессорной шины с данными второй и третьей процессорных шин, причем первый выход первого модуля соединен с первыми входами второго и третьего модуля, первый выход которого соединен с первым входом первого модуля и вторым входом второго модуля, первый выход которого соединен со вторыми входами первого и третьего модуля, причем в каждом модуле память соединена с процессором, процессор соединен с мостом, мост соединен с блоком управления I/O, выход которого является вторым выходом модуля, причем второй модуль системы включает вторую память, второй процессор, второй блок управления I/O, второй мост, сравнивающий данные второй процессорной шины с данными первой и третьей процессорных шин, причем третий модуль системы включает третью память, третий процессор, третий блок управления I/O, третий мост, сравнивающий данные третьей процессорной шины с данными первой и второй процессорных шин.

Недостатком этой системы является низкая надежность, обусловленная отказом функционирования ее при появлении второго отказа.

Известна отказоустойчивая вычислительная система для управления полетом летательного аппарата [2], состоящая из модулей обработки данных, включающих в себя процессоры и их запоминающие устройства, и контроллера шины, соединенных обычным широкополосным каналом связи.

Система выполняет ряд заданий, каждое из которых представляет собой последовательность итераций. Входными данными для выполнения очередной итерации некоторого задания являются выходные данные, полученные на предыдущей итерации некоторой совокупности заданий (включающей в себя и рассматриваемое задание). Входные и выходные сигналы всей системы формируются при выполнении заданий процессорами ввода-вывода. Надежность системы обеспечивается за счет независимого выполнения каждой итерации любого задания несколькими модулями. После выполнения очередной итерации процессор пересылает полученные результаты в собственное запоминающее устройство (ЗУ). Процессор, использующий результаты этой итерации, определяет их правильные значения, сравнивая выходные данные, сформированные каждым процессором, выполнявшим данную итерацию. Обычно правильные значения выбираются голосованием по методу «два из трех». Если не все варианты выходных данных идентичны, то фиксируется ошибка. Такие ошибки записываются в ЗУ процессора и затем используются управляющей программой для выявления неисправных блоков.

Недостатком этой системы является невысокое быстродействие, синхронизация по общесистемному времени, а не по программным событиям, отсутствие сбоеустойчивости и невозможность автоматического проведения процесса восстановления или перестройки структуры (реконфигурации).

Известна отказоустойчивая вычислительная система для управления полетом летательного аппарата [3], состоящая из пяти идентичных компьютеров общего назначения (GPCs), соединенных цифровой шиной данных, каждый GPC включает центральный узел обработки (CPU), который обеспечивает центральную вычислительную способность, и процессор входа/выхода (IOP), который исполняет операции контроля входов/выходов для CPU, четыре из компьютеров предназначены для решения задач и работают как избыточный совместимый набор. Вычисления каждого компьютера в этом наборе проверяются другими компьютерами. Таким образом, комплекс компьютеров поддерживает отказоустойчивость оперативной и безопасной работы системы, пятый компьютер предназначен для функционального управления системы.

Используются двадцать четыре шины данных компьютера, организованные в семь групп. Передача данных является мультиплексной с разделением во времени, используя импульсную кодовую модуляцию. Каждая шина работает по стробу одного мегабита в секунду.

Описанное устройство как наиболее близкое к предлагаемому принято за прототип и представлено на фиг.34.

Недостатком этой системы является невысокое быстродействие, синхронизация по общесистемному времени (по самой медленной ВМ), а не по программным событиям, отсутствие сбоеустойчивости и механизмов восстановления ВМ, находящейся в состоянии программного сбоя, и невозможность автоматического проведения процесса восстановления или перестройки структуры (реконфигурации).

Задачей изобретения является увеличение быстродействия и автоматизация процесса реконфигурации в отказоустойчивых системах.

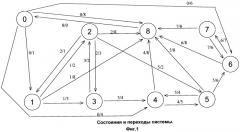

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.2-33, где:

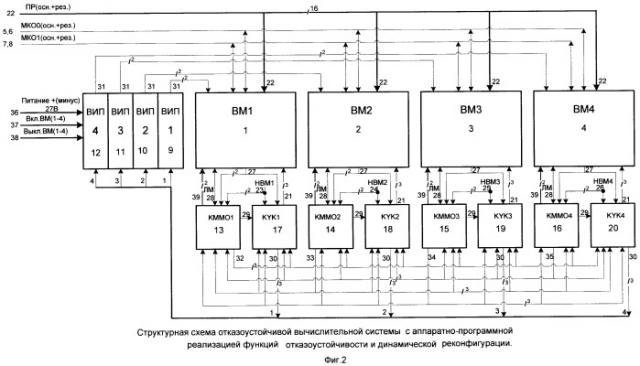

- на фиг.2 представлена структурная схема отказоустойчивой вычислительной системы с аппаратно-программной реализацией функций отказоустойчивости и динамической реконфигурации;

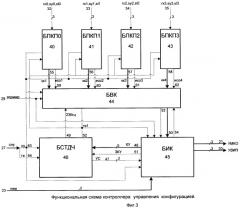

- на фиг.3 представлена функциональная схема контроллера управления конфигурацией;

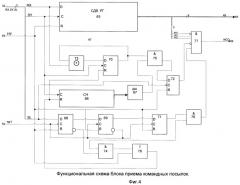

- на фиг.4 представлена функциональная схема блока приема командных посылок;

- на фиг.5 представлена функциональная схема блока выделения команд;

- на фиг.6 представлена функциональная схема блока исполнения команд;

- на фиг.7 представлена функциональная схема блока сторожевого таймера и делителя частоты;

- на фиг.8 представлена функциональная схема контроллера межмашинного обмена;

- на фиг.9 представлена функциональная схема блока приема посылок ММО;

- на фиг.10 представлена функциональная схема блока выдачи посылок ММО;

- на фиг.11 представлена функциональная схема блока управления прямым доступом;

- на фиг.12 представлена функциональная схема узла отсчета временных интервалов;

- на фиг.13 представлена функциональная схема узла режима одиночной команды;

- на фиг.14 представлена функциональная схема генератора одиночного импульса;

- на фиг.15 представлена диаграмма состояний и переходов;

- на фиг.16 представлен формат командной посылки магистрали ММО;

- на фиг.17 представлен формат команд управления конфигурацией ВМ;

- на фиг.18 представлен формат команды управления сторожевым таймером;

- на фиг.19 представлен формат команд управления МКО;

- на фиг.20 представлено соответствие значений кода КО выполняемым операциям;

- на фиг.21, 21а представлен алгоритм работы МС блока БВК;

- на фиг.22 представлен алгоритм работы МС блока исполнения команд (БИК);

- на фиг.23 представлен формат формируемых посылок;

- на фиг.24 представлен формат регистра управления РУСП блока приема посылок ММО;

- на фиг.25 представлен формат регистра управления РУСВ блока выдачи посылок ММО;

- на фиг.26 представлен алгоритм работы МС блока приема посылок каналов ММО;

- на фиг.27 представлен алгоритм работы МС блока выдачи посылок ММО;

- на фиг.28 представлена временная диаграмма операций записи и чтения в ОЗУ;

- на фиг.29, 29а представлен алгоритм работы МС блока управления прямым доступом;

- на фиг.30, 30а представлен алгоритм работы МС формирователя признака синхронизации;

- на фиг.31 представлен формат регистра управления и состояния РУСС блока формирователя признака синхронизации ФПС;

- на фиг.32 представлен формат регистра продолжительности ожидания синхронизации (РПОС) блока ФПС;

- на фиг.33 представлен формат регистра продолжительности синхронизации (РПС) блока ФПС.

Указанные преимущества заявляемой системы перед прототипом достигаются за счет того, что в отказоустойчивую вычислительную систему с аппаратно-программной реализацией функций отказоустойчивости и динамической реконфигурации, содержащую первую 1, вторую 2, третью 3 и четвертую 4 вычислительные машины (ВМ), соединенные первой 5, второй 6, третьей 7 и четвертой 8 последовательными шинами данных, дополнительно введены первый 9, второй 10, третий 11 и четвертый 12 вторичные источники питания (ВИП), первый 13, второй 14, третий 15 и четвертый 16 контроллеры межмашинного обмена (КММО), первый 17, второй 18, третий 19 и четвертый 20 контроллеры управления конфигурацией (КУК), первые 21 группы выходов которых соединены с первыми группами входов первой, второй, третьей и четвертой ВМ, вторые 22 группы входов которых соединены с первой группой входов системы, вторая 23, третья 24, четвертая 25, пятая 26 группы входов которой соединены с первыми группами входов КММО1 (13) и КУК1 (17), КММО2 (14) и КУК2 (18), КММО3 (15) и КУК3 (19), КММО4 (16) и КУК4 (20) соответственно, вторые 27 группы входов которых соединены с первыми группами выходов ВМ (1, 2, 3, 4), локальная двунаправленная магистраль 28 которых соединена с локальными двунаправленными магистралями КММО (13, 14, 15, 16), первые 29 выходы которых соединены с первыми входами контроллеров КУК (17, 18, 19, 20), вторые 30 группы выходов которых соединены с первыми группами входов ВИП (9, 10, 11, 12) соответственно, группы выходов 31 которых соединены с третьими группами входов ВМ (1, 2, 3, 4), причем первая 32 группа выходов первого 13 КММО соединена с третьими группами входов второго 14, третьего 15 и четвертого 16 КММО и первого 17, второго 18, третьего 19 и четвертого КУК 20, первая 33 группа выходов второго 14 КММО соединена с четвертыми группами входов первого 13, третьего 15 и четвертого КММО 16 и первого 17, второго 18, третьего 19 и четвертого 20 КУК, первая 34 группа выходов третьего 15 КММО соединена с пятыми группами входов первого 13, второго 14 и четвертого 16 КММО и первого 17, второго 18, третьего 19 и четвертого 20 КУК, первая 35 группа выходов четвертого 16 КММО соединена с шестыми группами входов первого 13, второго 14 и третьего 15 КММО и первого 17, второго 18, третьего 19 и четвертого 20 КУК, причем шестая 36 группа входов системы соединена со вторыми группами входов первого 9, второго 10, третьего 11 и четвертого 12 ВИП, первые входы которых соединены с седьмой 37 группой входов системы, восьмая 38 группа входов которой соединена со вторыми входами первого 9, второго 10, третьего 11 и четвертого 12 ВИП, причем вторые 39 группы выходов КММО (13, 14, 15, 16) соединены с четвертыми группами входов ВМ (1, 2, 3, 4).

Контроллер (17, 18, 19, 20) управления конфигурацией содержит первый 40 блок приема командных посылок, второй 41 блок приема командных посылок, третий 42 блок приема командных посылок, четвертый 43 блок приема командных посылок, блок выделения команд 44, блок исполнения команд 45, блок сторожевого таймера и делителя частоты 46, первая 47 группа выходов которого соединена с первой группой входов блока исполнения команд 45, первая 48 группа выходов которого соединена с первой группой входов блока сторожевого таймера и делителя частоты 46, первый 49 выход которого соединен с первым входом блока выделения команд 44, группа выходов 50 которого соединена со второй группой входов блока исполнения команд 45, вторая группа выходов которого является первой 21 группой выходов контроллера управления конфигурацией 17, вторая 30 группа выходов которого является третьей группой выходов блока исполнения команд 45, первый 51 выход которого соединен с первым входом блока сторожевого таймера и делителя частоты 46, второй 52 выход которого соединен с первыми входами первого блока приема командных посылок 40, второго блока приема командных посылок 41, третьего блока приема командных посылок 42, четвертого блока приема командных посылок 43, блока исполнения команд 45 и со вторым входом блока выделения команд 44, первый 53 выход которого соединен со вторым входом блока исполнения команд 45, второй 54 выход которого соединен с третьим входом блока выделения команд 44, первая 55, вторая 56, третья 57 и четвертая 58 группы входов которого соединены с первыми группами выходов первого 40, второго 41, третьего 42 и четвертого 43 блоков приема командных посылок соответственно, первые выходы которых соединены с четвертым 59, пятым 60, шестым 61, седьмым 62 входами блока выделения команд 44, восьмой 63 вход которого соединен со вторыми входами первого 40, второго 41, третьего 42 и четвертого 43 блоков приема командных посылок и блока сторожевого таймера и делителя частоты 46, третьим входом блока исполнения команд 45 и является первым сигналом второй 27 группы входов контроллера управления конфигурацией 17, первая 23 группа входов которого соединена с третьей группой входов блока исполнения команд 45, четвертый вход которого соединен с девятым входом блока выделения команд 44 и является первым 29 входом контроллера управления конфигурацией 17, третья 32, четвертая 33, пятая 34 и шестая 35 группы входов которого соединены с первыми группами входов первого 40, второго 41, третьего 42 и четвертого 43 блоков приема командных посылок соответственно, причем второй 64 сигнал второй 27 группы входов соединен с третьим входом блока сторожевого таймера и делителя частоты 46.

Блок приема командных посылок 40 содержит сдвиговый регистр 65, счетчик 66, дешифратор 67, первый 68 триггер, второй 69 триггер, третий 70 триггер, четвертый 71 триггер, пятый 72 триггер, исключающее ИЛИ 73, первый 74 элемент И, второй 75 элемент И, третий 76 элемент И, четвертый 77 элемент И, элемент ИЛИ 78, выход которого соединен со сбросовыми входами счетчика 66 и третьего 70 триггера, выход которого соединен с первыми входами исключающего ИЛИ 73 и второго 75 элемента И, выход которого соединен с информационным входом пятого 72 триггера, выход которого соединен с первым инверсным входом четвертого 77 элемента И, выход которого является выходом 59 блока приема командных посылок 40, группа выходов 55 которого соединена с группой выходов сдвигового регистра 65, информационный вход которого соединен со вторым входом исключающего ИЛИ 73 и является первым сигналом группы входов 32 блока приема командных посылок 40, второй сигнал которой соединен с тактовыми входами сдвигового регистра 65, счетчика 66 и третьего 70 триггера, информационный вход которого соединен с выходом исключающего ИЛИ 73, причем первый 52 вход блока приема командных посылок 40 соединен с тактовыми входами первого 68, второго 69 и четвертого 71 триггеров, выход четвертого 71 триггера соединен с первым входом третьего 76 элемента И, выход которого соединен с первым входом четвертого 77 элемента И, второй и третий входы которого являются вторым и третьим сигналами группы выходов 55 блока приема командных посылок 40, первый сигнал которой соединен со вторым инверсным входом четвертого 77 элемента И, причем второй 63 вход блока приема командных посылок 40 соединен со сбросовыми входами сдвигового регистра 65, первого 68, второго 69, четвертого 71 и пятого 72 триггеров и первым входом элемента ИЛИ 78, второй вход которого соединен с выходом первого 74 элемента И, первый вход которого соединен со вторым входом третьего 76 элемента И и инверсным выходом второго 69 триггера, прямой выход которого соединен с информационным входом четвертого 71 триггера, прямой выход первого 68 триггера соединен с информационным входом второго 69 триггера, а инверсный выход соединен со вторым входом первого 74 элемента И, третий сигнал группы входов 32 блока приема командных посылок 40 соединен с информационным входом первого 68 триггера и тактовым входом пятого 72 триггера, причем группа выходов счетчика 66 соединена с группой входов дешифратора 67, выход которого соединен со вторым входом второго 75 элемента И.

Блок выделения команд 44 содержит коммутатор 79 передачи кода команд (КПКК), регистр 80 признаков готовности (РПГ), коммутатор 81 признаков готовности кода команд (КПГКК), схему сравнения 82, узел отсчета временных интервалов (УОВИ) 83, узел режима одиночной команды (УРОК) 84, машину состояний (МС) 85, группа выходов которой соединена с группой входов РПГ 80 и с первой группой входов КПКК 79, первая группа выходов которого соединена с первой группой входов схемы сравнения 82 и является группой выходов 50 блока выделения команд 44, выход 53 которого соединен с первым выходом МС 85, второй выход 86 которой соединен с первым входом УОВИ 83, первый выход 87 которого соединен с первым входом МС 85, второй вход которой соединен с выходом схемы сравнения 82, вторая группа входов которой соединена со второй группой выходов КПКК 79, вторая группа входов 55 которого соединена с первой группой входов блока выделения команд 44, вторая 56, третья 57 и четвертая 58 группы входов которого соединены с третьей, четвертой и пятой группами входов КПКК 79 соответственно, причем первый 49 и второй 52 входы блока выделения команд 44 соединены со вторым входом УОВИ 83 и с третьими входами МС 85 и УОВИ 83 и первым входом УРОК 84 соответственно, первый 88 и второй 89 выходы которого соединены с четвертым и пятым входами МС 85, третий выход которой соединен с первым входом РПГ 80, второй, третий, четвертый и пятый входы которого являются четвертым 59, пятым 60, шестым 61 и седьмым 62 входами блока выделения команд 44 соответственно, восьмой 63 вход которого соединен со вторым входом УРОК 84, с четвертым входом УОВИ 83 и с шестым входом МС 85, первая группа входов которой соединена с группой выходов КПГКК 81, группа входов которого соединена с группой 90 выходов РПГ 80, с группой входов УРОК 84 и со второй группой входов МС 85, седьмой вход которой является девятым 29 входом блока 44, третий 54 вход которого соединен с третьим входом УРОК 84, третий 91 выход которого соединен с восьмым входом МС 85, девятый вход которого соединен со вторым 92 выходом УОВИ 83.

Блок исполнения команд (БИК) 45 содержит регистр команд (РгК) 93, схему сравнения (СС) 94, генератор одиночного импульса (ГОИ) 95 и машину состояний (МС) 96, первая группа выходов которой является первой 48 группой выходов БИК 45, вторая 21 группа выходов которого соединена со второй группой выходов МС 96, третья группа выходов которой является третьей 30 группой выходов БИК 45, первый 51 и второй 54 выходы которого соединены с первым и вторым выходами МС 96, первая и вторая группы входов которой соединены с первой и второй группами выходов РгК 93, третья группа выходов которого соединена с первой группой входов СС 94, выход которой соединен с первым входом МС 96, третий 97 выход которой соединен с первым входом ГОИ 95, выход 98 которого соединен со вторым входом МС 96, третий вход которой соединен со входом РгК 93 и является вторым 53 входом БИК 45, первая 47 группа входов которого соединена со вторым входом ГОИ 95 (первый сигнал) и четвертым входом (второй сигнал) МС 96, пятый вход которой соединен с третьим входом ГОИ 95 и является первым 51 входом БИК 45, третий 63 вход которого соединен с четвертым входом ГОИ 95 и шестым входом МС 96, седьмой вход которой является четвертым 29 входом БИК 45, вторая 50 и третья 23 группы входов которого соединены с группой входов РгК 93 и второй группой входов СС 94.

Блок сторожевого таймера и делителя частоты (БСТДЧ) 46 содержит сторожевой таймер (СТ) 99 и делитель частоты (ДЧ) 100, первый и второй выходы которого являются первым 49 и вторым 52 выходами БСТДЧ 46, первая 47 группа выходов которого соединена с выходом СТ 99 (первый сигнал) и третьим выходом ДЧ (второй сигнал) 100, четвертый выход которого соединен с первым входом СТ 99, группа входов которого является первой 48 группой входов БСТДЧ 46, вторая 27 группа входов которого (первый сигнал) 63 соединена с первым входом ДЧ 100 и вторым входом СТ 99, а второй 64 сигнал соединен со вторым входом ДЧ 100, причем первый 51 вход БСТДЧ 46 соединен с третьим входом СТ 99.

Контроллер межмашинного обмена (13, 14, 15, 16) содержит первый 101, второй 102 и третий 103 блоки приема посылок из каналов межмашинного обмена (Б1ПП, Б2ПП, Б3ПП), блок выдачи посылок (БВП) 104, блок управления прямым доступом (БПД) 105, формирователь признака синхронизации (ФПС) 106, первый 107 и второй 108 буферы ввода-вывода (Б1ВВ, Б2ВВ), первую 109 и вторую 110 группы элементов ИЛИ, первая группа выходов второй группы элементов ИЛИ является второй 39 группой выходов КММО 13, первая 32 группа выходов которого соединена с первой группой выходов БВП 104, вторая 111 группа выходов которого соединена с первыми 112 группами выходов Б1ПП 101, Б2ПП 102, Б3ПП 103 и ФПС 106 и группами входов второй 110 группы элементов ИЛИ, причем выход ФПС 106 является выходом 29 КММО 13, локальная магистраль 28 которого состоит из адресных шин, информационных шин и управляющих шин и соединена с группами входов-выходов первого 107 Б1ВВ и второго 108 Б2ВВ и БПД 105, с первой группой выходов 113, с первым выходом 114 и с первой группой входов 115 БПД 105, вторая 116 группа выходов которого соединена с первой группой входов Б1ВВ 107, группа выходов 117 которого соединена с первыми группами входов Б1ПП 101, Б2ПП 102, Б3ПП 103, БВП 104 и ФПС 106 и со второй группой входов БПД 105, третья группа входов которого соединена со вторыми группами входов Б1ПП 101, Б2ПП 102, Б3ПП 103, БВП 104, ФПС 106 и с группой выходов 118 второго 108 буфера Б2ВВ, первый вход которого соединен с выходом первой 109 группы элементов ИЛИ, группы входов которой соединены с третьей группой выходов БВП 104 и со вторыми 119 группами выходов Б1ПП 101, Б2ПП 102, Б3ПП 103 и ФПС 106, третья группа входов которого соединена с первыми 120 выходами Б1ПП 101, Б2ПП 102, Б3ПП 103 и БВП 104, третья группа входов которого соединена с третьими группами входов Б1ПП 101, Б2ПП 102, Б3ПП 103 и является первой 23 группой входов КММО 13, вторая 27 группа входов которого соединена с четвертыми группами входов БПД 105, Б1ПП 101, Б2ПП 102, Б3ПП 103, БВП 104 и ФПС 106, пятая группа входов которого соединена с пятыми группами входов Б1ПП 101, Б2ПП 102, Б3ПП 103. БВП 104, со входом Б1ВВ 107, со вторым входом Б2ВВ 108 и с третьей группой выходов 121 БПД 105, причем четвертая 33, пятая 34 и шестая 35 группы входов КММО 13 соединены с шестыми, седьмыми и восьмыми группами входов Б1ПП 101, Б2ПП 102, Б3ПП 103, девятые группы входов которых соединены с первой 32 группой выходов БВП 104, второй 122 выход которого соединен со вторыми выходами Б1ПП 101, Б2ПП 102, Б3ПП 103 и с пятой группой входов БПД 105.

Блок приема посылок ММО содержит первый 123, второй 124, третий 125, четвертый 126 мультиплексоры (МП), сдвиговый регистр (СДВ РГ) 127, регистр командного слова (РКС) 128, буферный регистр данных (БРД) 129, регистр управления и состояния приема (РУСП) 130, машину состояний 131, счетчик 132, дешифратор 133, триггер 134, элемент И 135, элемент исключающее ИЛИ 136, выход которого соединен с информационным входом триггера 134, выход которого соединен с первыми входами элемента исключающее ИЛИ 136 и элемента И 135, выход которого соединен с первым входом МС 131, первый выход которой соединен со входом РКС 128, группа входов которого соединена с группой входов БРД 129 и группой выходов СДВ РГ 127, информационный вход которого соединен со вторым входом элемента исключающее ИЛИ 136 и выходом первого мультиплексора 123, первый вход которого является первым сигналом девятой 32 группы входов блока 101, второй и третий сигналы которой соединены с первыми входами второго 124 и третьего 125 мультиплексоров, вторые входы которых соединены со вторым входом первого мультиплексора 123 и являются сигналами шестой 33 группы входов блока 101, седьмая 34 группа входов которого соединена с третьими входами первого 123, второго 124 и третьего 125 мультиплексоров, четвертые входы которых являются сигналами восьмой 35 группы входов блока 101, первая 112 группа выходов которого соединена со вторым и третьим выходами МС 131, четвертый выход которой соединен со входом БРД 129, группа выходов РКС 128 соединена с первой группой входов четвертого 126 мультиплексора, группа выходов которого является второй 119 группой выходов блока 101, первый 120 выход которого соединен с пятым выходом МС 131, шестой выход которой является вторым 122 выходом блока 101, первая 117 группа входов которого соединена с первой группой входов МС 131, седьмой и восьмой выходы которой соединены с первым и вторым входами четвертого мультиплексора 126, вторая группа входов которого соединена с группой выходов РУСП 130, первая группа входов которого является второй 118 группой входов блока 101, третья 23 группа входов которого соединена со второй группой входов МС 131, группа выходов которой соединена с пятыми входами первого 123, второго 124 и третьего 125 мультиплексоров, выход третьего мультиплексора соединен со сбросовым входом СДВ РГ 127, выход которого соединен со вторым входом МС 131, девятый выход которой соединен со входом РУСП 130, вторая группа входов которого является пятой 121 группой входов блока 101 и соединена с третьей группой входов МС 131, четвертая группа входов которой соединена со второй группой входов четвертого мультиплексора 126, третья группа входов которого соединена с группой выходов БРД 129, причем выход второго 124 мультиплексора соединен с тактовыми входами СДВ РГ 127, счетчика 132 и триггера 134, сбросовый вход которого соединен со сбросовым входом счетчика 132, с третьим входом МС 131 и является вторым сигналом четвертой 27 группы входов блока 101, первый сигнал которой соединен с четвертым входом МС 131, пятый вход которой соединен со вторым входом элемента И 135 и выходом дешифратора 133, группа входов которого соединена с группой выходов счетчика 132.

Блок выдачи посылок ММО 104 содержит регистр командного слова выдачи (РКСВ) 137, буферный регистр выдачи посылок (БВП) 138, регистр управления и состояния выдачи (РУСВ) 139, первый 140 и второй 141 мультиплексоры (МП), сдвиговый регистр (СДВ РГ) 142, счетчик 143, дешифратор 144, первый 145 и второй 146 триггеры, элемент исключающее ИЛИ 147 и машину состояний 148, первая группа выходов которой является первой 32 группой выходов блока выдачи посылок ММО 104, вторая 112 группа выходов которого соединена с первым и вторым выходами МС 148, вторая группа выходов которой соединена с третьей 119 группой выходов блока выдачи посылок ММО 104, первый 120 и второй 122 выходы которого соединены с третьим и четвертым выходами МС 148, первая и вторая группы входов которой являются первой 117 и третьей 23 группами входов блока выдачи посылок ММО 104, вторая 118 группа входов которого соединена с первыми группами входов РКСВ 137, БВП 138, РУСВ 139, тактовые входы которых соединены с пятым, шестым и седьмым выходами МС 148 соответственно, восьмой выход которой соединен с загрузочным и инверсным разрешающим входами СДВ РГ 142, выход которого соединен с первым входом второго 141 мультиплексора и соединен с первым входом МС 148, третья группа выходов которой соединена со второй группой входов РУСВ 139, группа выходов которого соединена с третьей группой входов МС 148, девятый выход которой соединен с тактовыми входами первого 145 и второго 146 триггеров, СДВ РГ 142 и счетчика 143, группа выходов которого соединена с группой входов дешифратора 144, инверсный выход которого соединен со вторым входом второго 141 мультиплексора, выход которого соединен с информационным входом второго триггера 146 и первым входом элемента исключающее ИЛИ 147, выход которого соединен с информационным входом первого 145 триггера, выход которого соединен со вторым входом элемента исключающее ИЛИ 147, причем первый сигнал четвертой 27 группы входов блока 104 соединен со вторым входом МС 148, третий вход которой является вторым сигналом четвертой 27 группы входов блока 104 и соединен со сбросовыми входами СДВ РГ 142, счетчика 143 и первого 145 триггера, с установочным входом второго 146 триггера, выход которого соединен с четвертым входом МС 148, четвертая группа входов которой является пятой 121 группой входов блока 104, причем группы выходов РКСВ 137 и БВП 138 соединены с первой и второй группами входов первого 140 МП, группа выходов которого соединена с информационными входами СДВ РГ 142, инверсный выход первого 145 триггера соединен со вторым входом второго 141 МП, вход первого мультиплексора 140 соединен с пятым выходом МС 148.

Блок управления прямым доступом 105 содержит первый регистр текущего адреса приема (РТАП1) 149, второй регистр текущего адреса приема (РТАП2) 150, третий регистр текущего адреса приема (РТАП3) 151, первый регистр конечного адреса приема (РКАП1) 152, второй регистр конечного адреса приема (РКАП2) 153, третий регистр конечного адреса приема (РКАП3) 154, регистр текущего адреса выдачи (РТАВ) 155, регистр конечного адреса выдачи (РКАВ) 156, первый счетчик текущего адреса первого блока приема посылок (СТА Б1ПП) 157, второй счетчик текущего адреса второго блока приема посылок (СТА Б2ПП) 158, третий счетчик текущего адреса третьего блока приема посылок (СТА Б3ПП) 159, счетчик текущего адреса блока выдачи посылок (СТА БВП) 160, первую 161, вторую 162, третью 163, четвертую 164 схемы сравнения, машину состояний (МС) 165, мультиплексор (МП) 166, первая и вторая группы выходов которого являются первой 28 и второй 116 группами выходов локальной магистрали (ЛМ) блока 105, группа входов-выходов 28 которого соединена с группой входов-выходов МС 165, первая группа выходов которой является третьей 121 группой выходов блока, первый выход ЛМ 28 блока соединен с первым выходом МС 165, вторая группа выходов которой соединена с первыми входами регистров РТАП1 149, РТАП2 150, РТАП3 151, РТАВ 155, РКАП1 152, РКАП2 153, РКАП3 154, РКАВ 156 и счетчиков текущего адреса СТА Б1ПП 157, СТА Б2ПП 158, СТА Б3ПП 159, СТА БВП 160, первая группа выходов которого соединена с первой группой входов МП 166, вторая, третья и четвертая группы входов которого соединены с первыми группами выходов счетчиков СТА Б1ПП 157, СТА Б2ПП 158, СТА Б3ПП 159, вторые входы которых соединены со вторым, третьим и четвертым выходами МС 165, пятый выход которой соединен со вторым входом счетчика СТА БВП 160, вторая группа выходов которого соединена с первой группой входов четвертой СС 164, вторая группа входов которой соединена с группой выходов регистра РКАВ 156, группа входов которого соединена с группами входов регистров РТАП1 149, РТАП2 150, РТАП3 151, РТАВ 155, РКАП1 152, РКАП2 153, РКАП3 154 и является третьей 118 группой входов блока 105, первая (ЛМ) 28 и вторая 117 группы входов которого соединены с первой и второй группами входов МС 165, третья группа выходов которой соединена с пятой группой входов МП 166, причем группы выходов регистров РТАВ 155, РТАП1 149, РТАП2 150, РТАП3 151 соединены с группами входов счетчиков СТА БВП 160, СТА Б1ПП 157, СТА Б2ПП 158, СТА Б3ПП 159, третьи входы которых соединены между собой и соединены с первым входом МС 165 и являются первым сигналом четвертой 27 группы входов блока 105, второй сигнал которой соединен со вторым входом МС 165, третий, четвертой, пятый и шестой входы которой соединены с выходами первой 161, второй 162, третьей 163 и четвертой 164 схем сравнения, первые группы входов которых соединены с группами выходов счетчиков СТА Б1ПП 157, СТА Б2ПП 158, СТА Б3ПП 159, причем группы выходов регистров РКАП1 152, РКАП2 153, РКАП3 154 соединены со вторыми группами входов первой 161, второй 162 и третьей 163 СС, пятая 122 группа входов блока 105 соединена с третьей группой входов МС 165.

Узел отсчета временных интервалов (УОВИ) 83 содержит первый 167, второй 168, третий 169 и четвертый 170 триггеры, счетчик 171, дешифратор 172 и элемент ИЛИ 173, выход которого соединен со сбросовыми входами второго 168 и третьего 169 триггеров, прямой выход которого является вторым 92 выходом УОВИ 83, первый 87 выход которого соединен с выходом четвертого 170 триггера и первым входом элемента ИЛИ 173, второй вход которого является четвертым 63 входом УОВИ 83 и соединен со сбросовыми входами первого 167 и четвертого 170 триггеров, тактовые входы которых соединены с тактовым входом второго 168 триггера и является третьим 52 входом УОВИ 83, первый 86 вход которого соединен с информационным входом второго 168 триггера, выход которого соединен с тактовым входом третьего 169 триггера, инверсный выход которого соединен со сбросовым входом счетчика 171, тактовый вход которого соединен с выходом первого 167 триггера, информационный вход которого является вторым 48 входом УОВИ 83, причем группа выходов счетчика 171 соединена с группой входов дешифратора 172, выход которого соединен с информационным входом четвертого 170 триггера, информационный вход третьего 169 триггера соединен с 3.3В.

Узел режима одиночной команды (УРОК) 84 содержит первый 174, второй 175 и третий 176 триггеры, первый 177 и второй 178 элементы ИЛИ, первый 179 и второй 180 элементы И, выходы которых являются третьим 91 и вторым 89 выходами УРОК 84, первый 88 выход которого соединен с выходом первого 174 триггера, инверсный выход которого соединен с первым входом второго 178 элемента ИЛИ, выход которого соединен со сбросовыми входами второго 175 и третьего 176 триггеров, прямой и инверсный выходы которого соединены с первыми входами первого 179 и второго 180 элементов И, вторые входы которых соединены с информационным входом третьего 176 триггера и с выходом второго 175 триггера, тактовый вход которого соединен с тактовыми входами первого 174 и третьего 176 триггеров и является первым 52 входом УРОК 84, второй 63 вход которого соединен со вторым входом второго элемента ИЛИ 178 и сбросовым входом первого 174 триггера, информационный вход которого является третьим 54 входом УРОК 84, группа входов 90 которого соединена с первым, вторым, третьим и четвертым входами первого 177 элемента ИЛИ, выход которого соединен с информационным входом второго 175 триггера.

Генератор одиночного импульса (ГОИ) 95 содержит счетчик 181, дешифратор 182, первый 183 и второй 184 триггеры и элемент И 185, выход которого является выходом 98 ГОИ, первый 97 и второй 47 входы которого соединены со сбросовым и тактовым входами счетчика 181 соответственно, группа выходов которого соединена с группой входов дешифратора 182, выход которого соединен с информационным входом первого 183 триггера, выход которого соединен с информационным входом второго 184 триггера и первым входом элемента И 185, второй вход которого соединен с инверсным выходом второго 184 триггера, тактовый вход которого соединен с тактовым входом первого 183 триггера и является третьим 52 входом ГОИ, четвертый 63 вход которого соединен со сбросовыми входами первого 183 и второго 184 триггеров.

Формирователь признака синхронизации (ФПС) 106 содержит регистр управления и состояния синхронизации (РУСС) 186, регистр продолжительности ожидания синхронизации (РПОС) 187, регистр продолжительности синхронизации (РПС) 188, мультиплексор (МП) 189, счетчик продолжительности ожидания синхронизации (СПОС) 190 и машину состояния (МС) 191, первая группа выходов которой является первой 112 группой выходов ФПС, вторая 119 группа выходов которого соединена с группой выходов МП 189, первая группа входов которого соединена с группой выходов РПОС 187 и группой входов СПОС 190, выход которого соединен с первым входом МС 191, вторая группа выходов которой соединена с первой группой входов РУСС 186, группа выходов которого соединена с первой группой входов МС 191 и со второй группой входов МП 189, третья группа входов которого соединена с группой выходов РПС 188 и второй группой входов МС 191, третья группа выходов и первый выход которой соединены с четвертой группой входов МП 189 и выходом 29 ФПС 106 соответственно, первая 117 группа входов которого соединена с третьей группой входов МС 191, четвертая, пятая и шестая группы входов которой соединены с третьей 120, четвертой 27 и пятой 121 группами входов ФПС 106 соответственно, вторая 118 группа входов которого соединена с первыми группами входов РПОС 187 и РПС 188 и со второй группой входов РУСС 186, первый и второй входы которого соединены со вторым и третьим выходами МС 191, четвертый и пятый выходы которой соединены с первыми входами РПОС 187 и СПОС 190 и вторым входом РПОС 187, причем шестой, седьмой и восьмой выходы МС 191 соединены со вторым входом СПОС 190, с первым и вторым входами РПС 188 соответственно.

Отказоустойчивая вычислительная система с аппаратно-программной реализацией функций отказоустойчивости и динамической реконфигурации работает следующим образом.

Отказоустойчивая вычислительная система включает три ВМ рабочей конфигурации и одну ВМ в холодном резерве, общая схема парирования сбоев и отказов состоит в следующем. Структурная схема отказоустойчивой вычислительной системы с аппаратно-программной реализацией функций отказоустойчивости и динамической реконфигурации представлена на фиг.2. Каждая ВМ рабочей конфигурации решает одну и ту же целевую задачу специального программного обеспечения (СПО), при помощи программного обеспечения отказоустойчивости (ПОО) результаты решения передает другим ВМ рабочей конфигурации и принимает от них их копии результатов решения, а затем по своей и полученным копиям решения определяет прав