Полевой транзисторный ключ

Иллюстрации

Показать всеИзобретение относится к области преобразовательной техники, а более конкретно к полевым транзисторным ключам на базе силовых МДП-транзисторов, и может найти применение в импульсных высокочастотных преобразователях напряжения. Изобретение обеспечивает повышение КПД за счет одновременного снижения статических и динамических потерь в ключевом элементе. Сущность изобретения: полевой транзисторный ключ содержит схему управления и ключевой элемент, состоящий из параллельно включенных МДП-транзисторов, истоки которых объединены и соединены с выводом схемы управления, один из МДП-транзисторов - быстродействующий средней мощности, а другой - низкочастотный мощный, затворы их соответственно присоединены к первому и второму выводам схемы управления, которая содержит логическое устройство, обеспечивающее необходимые задержки между управляющими импульсами. 5 ил.

Реферат

Предлагаемое изобретение относится к области преобразовательной техники, а более конкретно к полевым транзисторным ключам (ПТК) на базе силовых МДП-транзисторов, и может найти применение в импульсных высокочастотных преобразователях напряжения.

Известны ключи аналогичного назначения (см. «Мощные переключающие МДП-транзисторы и их применение». Ч.II, В.В.Бачурин, В.П.Дьяконов, B.C.Ежов, A.M.Ремнев. - М.: ЦНИИ «Электроника», 1984. - 44 стр. (Обзоры по электронной технике, серия 2, выпуск 1)). Распространенным способом снижения потерь в ключевых элементах (КЭ) является параллельное включение нескольких транзисторов или использование транзисторов с большим запасом по мощности, имеющих более низкое значение сопротивления открытого канала.

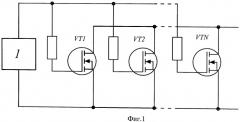

Наиболее близким по своей технической сущности к заявляемому является полевой транзисторный ключ, содержащий параллельно включенные однотипные мощные МДП-транзисторы, как показано на фиг.1 (см. Э.С.Окснер «Мощные полевые транзисторы и их применение». М.: «Радио и связь», 1985. - 114-120 стр.).

Полевой транзисторный ключ состоит из ключевого элемента (КЭ), представляющего собой два или более параллельно включенных силовых МДП-транзистора, управляемых от одной общей для всех транзисторов схемы управления (СУ). Параллельное включение используется для снижения статических потерь на КЭ в открытом состоянии за счет уменьшения его сопротивления или при необходимости коммутации тока, превышающего предельно допустимое значение для одного транзистора. Для предотвращения паразитных колебаний затворы транзисторов включаются через небольшие, 5-10 Ом, сопротивления или на выводы затворов надеваются небольшие ферритовые бусинки. Однако при таком включении пропорционально количеству транзисторов увеличивается входная емкость, так что если важно быстродействие, то схема управления должна обладать большей мощностью для перезаряда входной емкости.

Основными недостатками указанного прототипа являются относительно большие динамические потери, обусловленные большим временем переключения мощных транзисторов с малым сопротивлением открытого канала, которое выбирается из условий снижения статических потерь, а также невозможность комплексного улучшения удельных энергетических характеристик, а именно повышение частоты преобразователя с целью уменьшения массы индуктивных элементов приводит к увеличению динамических потерь, а значит, к уменьшению КПД.

Задача, на решение которой направлено заявляемое изобретение, - повышение КПД за счет одновременного снижения статических и динамических потерь в КЭ.

Поставленная задача решается за счет того, что полевой транзисторный ключ содержит схему управления и ключевой элемент, состоящий из параллельно включенных МДП-транзисторов, истоки которых объединены и соединены с выводом схемы управления, один из МДП-транзисторов - быстродействующий средней мощности, а другой - низкочастотный мощный, затворы их соответственно присоединены к первому и второму выводам схемы управления, которая содержит логическое устройство, обеспечивающее необходимые задержки между управляющими импульсами.

Изобретение поясняется чертежами, где:

на фиг.1 показан прототип;

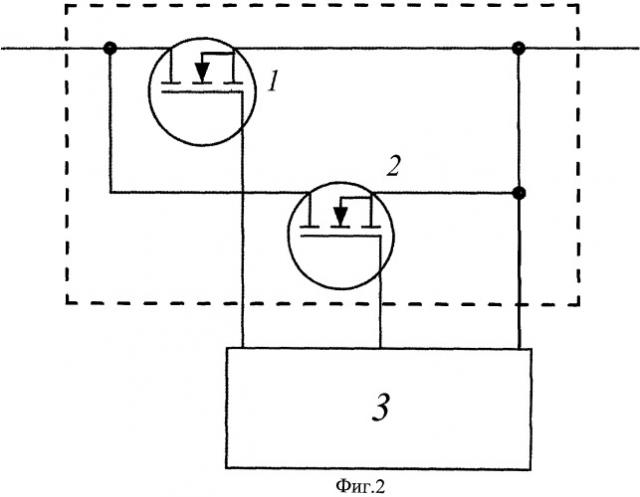

на фиг.2 изображен заявляемый ПТК;

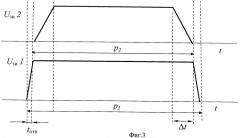

на фиг.3 изображены временные диаграммы, поясняющие его работу, где масштаб крутизны фронтов искажен для наглядности;

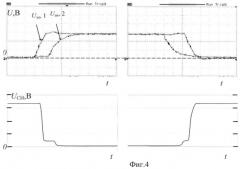

на фиг.4 изображены осциллограммы напряжений МДП-транзисторов, где Uзи - напряжение затвор-исток (масштаб по напряжению 5 вольт/деление, масштаб по времени 25 наносекунд/деление), Uси - напряжение сток-исток (масштаб по напряжению 15 вольт/деление);

на фиг.5 приведена электрическая схема устройства управления (СУ), один из вариантов ее выполнения.

Заявляемый ПТК состоит из схемы управления и ключевого элемента. КЭ содержит быстродействующий МДП-транзистор 1 средней мощности и низкочастотный мощный МДП-транзистор 2, обладающий малым сопротивлением открытого канала. При этом сток транзистора 1 соединен со стоком транзистора 2, исток транзистора 1 соединен с истоком транзистора 2, а затворы присоединены соответственно к первому и второму выходам схемы управления 3, третий выход схемы управления (общий) присоединен к объединенным истокам.

Работает ПТК следующим образом. При включении КЭ управляющий импульс от схемы управления 3 сначала поступает на затвор быстродействующего МДП-транзистора 1, при этом динамические потери в ключе определяются только этим транзистором. Через время toтп, равное времени включения транзистора 1, от схемы управления 3 подается отпирающий импульс на низкочастотный МДП-транзистор 2. Соединенные параллельно транзисторы обладают меньшим сопротивлением в открытом состоянии и определяют статические потери. При запирании КЭ задний фронт управляющего импульса, поступающего на затвор быстродействующего МДП-транзистора 1, отстает от заднего фронта импульса, поступающего на затвор низкочастотного транзистора 2, на время выключения транзистора 2, что минимизирует динамические потери на заднем фронте, которые также определяются быстродействующим транзистором 1.

Таким образом, быстродействующий транзистор 1 минимизирует величину динамических потерь на переднем и заднем фронтах за счет малого времени переключения, а низкочастотный транзистор 2, шунтируя быстродействующий транзистор, минимизирует величину статических потерь, за счет чего общие потери снижаются. При этом необходимо, чтобы управляющий импульс (p2) мощного транзистора 2 имел меньшую длительность по сравнению с управляющим импульсом (p1) быстродействующего транзистора 1 и по времени был заключен внутри него. Длительности импульсов и требуемые задержки на включение и выключение транзисторов обеспечиваются схемой управления 3.

За счет одновременного снижения статических и динамических потерь в КЭ в нем уменьшается тепловыделение и повышается КПД. При необходимости снижения массы индуктивных элементов за счет повышения частоты преобразователя можно повысить КПД незначительно или оставить неизменным. Т.о. можно выбрать вариант с высоким КПД и низкой массой индуктивных элементов.

Был изготовлен лабораторный образец. В качестве транзистора 1 использован МДП-транзистор IRFB17N20D, в качестве транзистора 2 - МДП-транзистор КП813А. Схема управления представлена на фиг.5. Осциллограммы работы данного устройства представлены на фиг.4.

Полевой транзисторный ключ, содержащий схему управления и ключевой элемент, состоящий из параллельно-включенных МДП-транзисторов, истоки которых объединены и соединены с выводом схемы управления, отличающийся тем, что один из МДП-транзисторов - быстродействующий средней мощности, а другой - низкочастотный мощный, затворы их соответственно присоединены к первому и второму выводу схемы управления, которая содержит логическое устройство, обеспечивающее необходимые задержки между управляющими импульсами.