Резервированный формирователь

Иллюстрации

Показать всеИзобретение относится к резервированному формированию вычислительных систем. Техническим результатом является повышение надежности вычислительных систем. Резервированный формирователь содержит задающий генератор, подключенный к нему блок формирования, выходы которого являются выходами формирователя, два задающих генератора с подключенными к ним блоками формирования, выходы которых являются выходами формирователя, управляющий выход каждого блока формирования подключен к управляющим входам двух других формирователей. 1 з.п. ф-лы, 2 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных устройств, к которым предъявляются повышенные требования по безотказности.

При создании вычислительных устройств, работающих в неблагоприятных внешних условиях, например вычислительных систем, управляющих объектами ракетно-космической техники, с целью повышения надежности используют резервирование. Одним из наиболее распространенных решений является троирование (трехканальное построение) вычислительных устройств с мажоритацией выходных сигналов или с переключением по результатам попарного сравнения информации трех каналов (см., например, трехканальную вычислительную систему по а.с. №1156273). Для работы таких систем требуется синхронная и синфазная работа всех трех каналов системы, что обеспечивается наличием общего блока формирования синхроимпульсов (см. «Устройство для формирования синхроимпульсов», a.c. SU №1338031. Н03K 5/00, от 13.09.87). Устройство содержит задающий генератор, который реализован, в частности, на основе кольца из нечетного числа инверторов, а также блок формирования импульсов, формирующий синхроимпульсы для синхронизации работы компонентов вычислительной системы.

Данное устройство может быть принято в качестве прототипа.

Общим недостатком известных устройств, обеспечивающих работу резервированных вычислительных систем, является то, что при возникновении отказа любого элемента устройства формирования импульсов вычислительная система переходит в неработоспособное состояние. Возникает задача найти такую реализацию устройства формирования, при которой одиночный отказ в нем приводил бы к отказу только одного канала в резервированной системе. Для решения этой задачи предлагается резервированный формирователь импульсов синхронизации.

Формирователь включает три идентичных канала, каждый из которых содержит задающий генератор, подключенный к блоку формирования синхроимпульсов для соответствующего канала вычислительной системы.

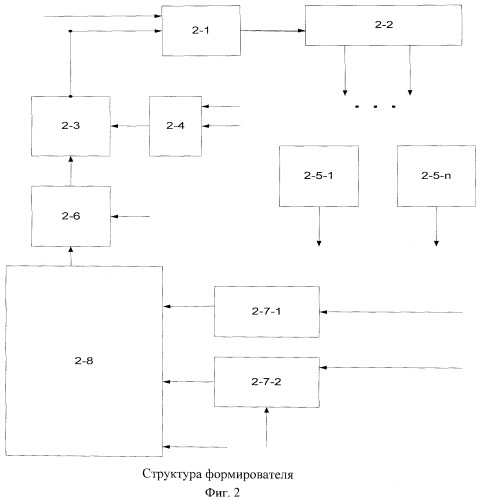

Структурная схема формирователя приведена на фиг.1, где цифрами 1-1-1, 1-1-2 и 1-1-3 обозначены задающие генераторы первого, второго и третьего каналов формирователя, а цифрами 1-2-1, 1-2-2 и 1-2-3 обозначены блоки формирования синхроимпульсов первого, второго и третьего каналов формирователя. Выходы задающих генераторов в каждом канале подключены к соответствующим блокам формирования синхроимпульсов, у каждого из которых группа выходов является выходами формирователя, а управляющий выход подключен к одному из входов двух других блоков формирования.

Блок формирования синхроимпульсов содержит элемент И, сдвиговый регистр, триггер останова, дешифратор, n триггеров-формирователей выходных сигналов, два триггера привязки, мажоритарный элемент и триггер пуска.

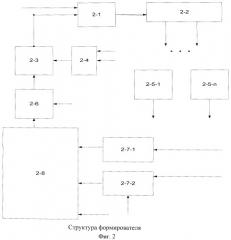

На фиг.2 приведена структурная схема блока формирования, где цифрой 2-1 обозначен элемент И, цифрой 2-2 обозначен сдвиговый регистр, цифрой 2-3 обозначен триггер останова, цифрой 2-4 обозначен дешифратор, цифрами от 2-5-1 до 2-5-n обозначены n триггеров-формирователей выходных сигналов, выходы которых являются группой выходов блока и выходами формирователя в целом, цифрой 6 обозначен триггер пуска, цифрами 2-7-1 и 2-7-2 обозначены триггеры привязки сигналов останова, поступающих с других каналов формирователя. Цифрой 2-8 обозначен мажоритарный элемент. При этом первый вход элемента И является входом блока, подключенным к выходу задающего генератора, а выход элемента И подключен к входу сдвигового регистра, группа выходов которого подключена к входам дешифратора, выход которого подключен к запускающему входу триггера останова, выход которого подключен ко второму входу элемента И. Кроме того, запускающие и сбрасывающие входы триггеров-формирователей подключены соответственно к определенным нечетным и четным разрядам сдвигового регистра, определенные разряды которого подключены к стробирующим входам триггера пуска и триггеров привязки, выходы которых подключены к первому и второму входам мажоритарного элемента, к третьему входу которого подключен выход триггера останова, являющийся выходом блока, а сбрасывающий вход триггера подключен к выходу триггера пуска, вход которого подключен к выходу мажоритарного элемента. Входы триггеров привязки являются входами блока, связанными с выходами формирователей двух других каналов. Формирователь работает следующим образом.

После включения питания частота с задающих генераторов начинает поступать на сдвиговые регистры блоков формирования.

Сдвиг по разрядам регистра 2-2 обеспечивает запуск в нужной фазе и сброс после требуемой длительности триггеров-формирователей 2-5, с выхода которых начинают поступать на выход импульсы синхронизации.

После определенного числа тактов, определяемых распайкой дешифратора 2-4, сигнал с его выхода включает триггер останова 2-3, включение которого запрещает прохождение сигналов задающего генератора через элемент И на сдвиговый регистр, в результате чего приостанавливается формирование импульсов синхронизации. Сигнал с выхода включенного триггера останова поступает на один из входов своего мажоритарного элемента и выдается в два других канала блоков формирования.

После поступления на вход мажоритарного элемента еще одного сигнала с любого из двух других каналов его выходной сигнал включает триггер пуска, который сбрасывает триггер останова и поступление частоты на сдвиговый регистр возобновляется. Сигналы останова, поступающие с соседних каналов, перед поступлением на мажоритарный элемент проходят привязку к частоте задающего генератора данного канала, а вторичная привязка после мажоритарного элемента на триггере пуска исключает возникновение «гоночных» ситуаций из-за несовпадения фаз задающих генераторов разных каналов. В результате возникает «притормаживание» наиболее быстрого канала формирователя, которое может перемещаться по каналам формирователя и обеспечивает их синфазную работу по формированию одноименных синхроимпульсов разных каналов с точностью до такта высокой частоты задающих генераторов. Выбор частоты задающих генераторов не менее 16М Гц, как правило, обеспечивает синхронную и синфазную в требуемых пределах работу разных каналов вычислительной системы. В то же время отказ любого элемента в одном из каналов формирователя не приводит к нарушению работы двух других каналов и системы в целом, так как отказ в одном из блоков формирования позволяет сохранить работоспособность по крайней мере двух каналов формирователя и соответственно вычислительной системы в целом.

1. Резервированный формирователь, содержащий задающий генератор, к которому подключен блок формирования, выходы которого являются выходами формирователя, отличающийся тем, что в его состав дополнительно введены два задающих генератора с подключенными к ним блоками формирования, выходы которых являются выходами формирователя, при этом управляющий выход каждого блока формирования подключен к управляющим входам двух других формирователей.

2. Формирователь по п.1, отличающийся тем, что каждый блок формирования содержит элемент И, первый вход которого является входом блока и выходом задающего генератора, а выход элемента И подключен к входу сдвигового регистра, группа выходов которого подключена к входам дешифратора, выход которого подключен к запускающему входу триггера останова, выход которого является выходом блока и подключен ко второму входу элемента И, а выходы нечетных и четных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам n триггеров - формирователей, выходы которых являются выходами блока, первый и второй управляющих входы которого являются соответственно входами первого и второго триггеров привязки, синхронизирующие входы которых подключены к выходу j-го разряда сдвигового регистра, а выходы этих триггеров подключены соответственно к первому и второму входам мажоритарного элемента, к третьему входу которого подключен выход триггера останова, а выход мажоритарного элемента подключен к запускающему входу триггера пуска, стробирующий вход которого подключен к выходу j+1 разряда сдвигового регистра, а выход триггера пуска подключен к сбрасывающему входу триггера останова.