Дифференциальный усилитель с повышенным ослаблением входного синфазного сигнала

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, работающих с двумя сигналами, имеющими синфазную составляющую. Технический результат: повышение коэффициента ослабления входных синфазных сигналов (Кос.сф). Устройство содержит с первого по четвертый входные транзисторы, с первого по четвертый токостабилизирующие двухполюсники, первый и второй выходные транзисторы, источник вспомогательного напряжения, цепь нагрузки, первое и второе дополнительные токовые зеркала. 6 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ) и компараторах), работающих с двумя сигналами, имеющими синфазную составляющую.

Известны схемы дифференциальных усилителей (ДУ) на основе двух параллельно включенных дифференциальных каскадов [1-14], которые стали основой многих серийных операционных усилителей, выпускаемых как зарубежными, так и российскими микроэлектронными фирмами.

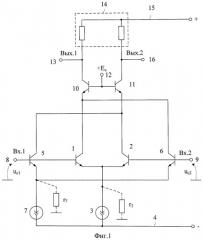

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №6.583.668 fig.5, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны друг с другом и через первый 3 токостабилизирующий двухполюсник подключены к первой 4 шине источника питания, третий 5 и четвертый 6 входные транзисторы, эмиттеры которых объединены и через второй 7 токостабилизирующий двухполюсник подключены к первой 4 шине источника питания, причем база третьего 5 входного транзистора соединена с первым 8 входом устройства и базой первого 1 входного транзистора, база четвертого 6 входного транзистора соединена со вторым 9 входом устройства и базой второго 2 входного транзистора, первый 10 и второй 11 выходные транзисторы, базы которых объединены и подключены к источнику вспомогательного напряжения 12, эмиттер первого 10 выходного транзистора соединен с коллектором первого 1 входного транзистора, эмиттер второго 11 выходного транзистора соединен с коллектором второго 2 входного транзистора, коллектор первого 10 выходного транзистора соединен с первым 13 выходом устройства и первым входом цепи нагрузки 14, согласованной со второй 15 шиной источника питания, коллектор второго 11 выходного транзистора соединен со вторым 16 выходом устройства и вторым входом цепи нагрузки 14, согласованной со второй 15 шиной источника питания.

Существенный недостаток известного ДУ, фиг.1, состоит в том, что он имеет сравнительно невысокое ослабление входных синфазных сигналов, что отрицательно сказывается на точностных параметрах неинвертирующих решающих усилителей и компараторов двух сигналов на его основе.

Основная задача предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов (Кос.сф).

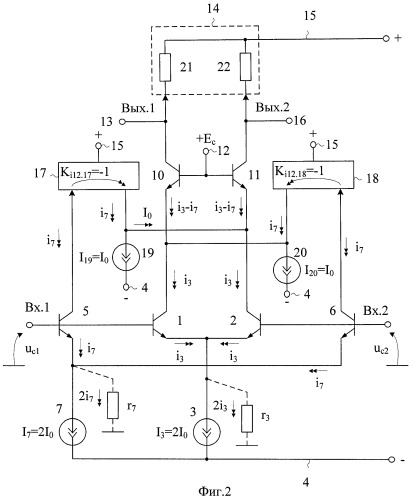

Поставленная задача решается тем, что в дифференциальном усилителе (фиг.1), содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны друг с другом и через первый 3 токостабилизирующий двухполюсник подключены к первой 4 шине источника питания, третий 5 и четвертый 6 входные транзисторы, эмиттеры которых объединены и через второй 7 токостабилизирующий двухполюсник подключены к первой 4 шине источника питания, причем база третьего 5 входного транзистора соединена с первым 8 входом устройства и базой первого 1 входного транзистора, база четвертого 6 входного транзистора соединена со вторым 9 входом устройства и базой второго 2 входного транзистора, первый 10 и второй 11 выходные транзисторы, базы которых объединены и подключены к источнику вспомогательного напряжения 12, эмиттер первого 10 выходного транзистора соединен с коллектором первого 1 входного транзистора, эмиттер второго 11 выходного транзистора соединен с коллектором второго 2 входного транзистора, коллектор первого 10 выходного транзистора соединен с первым 13 выходом устройства и первым входом цепи нагрузки 14, согласованной со второй 15 шиной источника питания, коллектор второго 11 выходного транзистора соединен со вторым 16 выходом устройства и вторым входом цепи нагрузки 14, согласованной со второй 15 шиной источника питания, предусмотрены новые элементы и связи - коллектор третьего 5 входного транзистора соединен со входом первого 17 дополнительного токового зеркала, согласованного со второй 15 шиной источника питания, коллектор четвертого 6 входного транзистора соединен со входом второго 18 дополнительного токового зеркала, согласованного со второй 15 шиной источника питания, выход первого 17 дополнительного токового зеркала подключен к эмиттеру второго 11 выходного транзистора и через третий 19 токостабилизирующий двухполюсник связан с первой 4 шиной источника питания, выход второго 18 дополнительного токового зеркала соединен с эмиттером первого 10 выходного транзистора и через четвертый 20 токостабилизирующий двухполюсник соединен с первой 4 шиной источника питания.

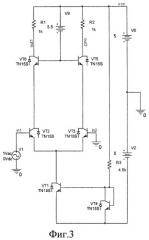

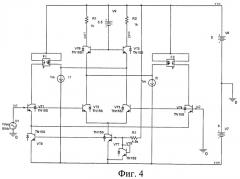

Схема усилителя-прототипа представлена на чертеже фиг.1. На чертеже фиг.2 показан заявляемый ДУ в соответствии с формулой изобретения. Схемы исследованных авторами ДУ фиг.1 и фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП HПП «Пульсар» представлены на чертеже фиг.3 (прототип) и фиг.4 (заявляемый ДУ), а на чертеже фиг.5 изображены результаты их компьютерного моделирования - частотная зависимость коэффициента ослабления входных синфазных сигналов (Кос.сф). Графики фиг.6 характеризуют частотную зависимость дифференциального коэффициента усиления ДУ фиг.3 и фиг.4.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых связаны друг с другом и через первый 3 токостабилизирующий двухполюсник подключены к первой 4 шине источника питания, третий 5 и четвертый 6 входные транзисторы, эмиттеры которых объединены и через второй 7 токостабилизирующий двухполюсник подключены к первой 4 шине источника питания, причем база третьего 5 входного транзистора соединена с первым 8 входом устройства и базой первого 1 входного транзистора, база четвертого 6 входного транзистора соединена со вторым 9 входом устройства и базой второго 2 входного транзистора, первый 10 и второй 11 выходные транзисторы, базы которых объединены и подключены к источнику вспомогательного напряжения 12, эмиттер первого 10 выходного транзистора соединен с коллектором первого 1 входного транзистора, эмиттер второго 11 выходного транзистора соединен с коллектором второго 2 входного транзистора, коллектор первого 10 выходного транзистора соединен с первым 13 выходом устройства и первым входом цепи нагрузки 14, согласованной со второй 15 шиной источника питания, коллектор второго 11 выходного транзистора соединен со вторым 16 выходом устройства и вторым входом цепи нагрузки 14, согласованной со второй 15 шиной источника питания. Коллектор третьего 5 входного транзистора соединен со входом первого 17 дополнительного токового зеркала, согласованного со второй 15 шиной источника питания, коллектор четвертого 6 входного транзистора соединен со входом второго 18 дополнительного токового зеркала, согласованного со второй 15 шиной источника питания, выход первого 17 дополнительного токового зеркала подключен к эмиттеру второго 11 выходного транзистора и через третий 19 токостабилизирующий двухполюсник связан с первой 4 шиной источника питания, выход второго 18 дополнительного токового зеркала соединен с эмиттером первого 10 выходного транзистора и через четвертый 20 токостабилизирующий двухполюсник соединен с первой 4 шиной источника питания.

В частном случае цепь нагрузки 14 реализована на основе резисторов 21 и 22. Элементы r3 и r7 в схеме фиг.2 характеризуют выходные сопротивления двухполюсников 3 и 7 соответственно.

Рассмотрим работу заявляемого ДУ (фиг.2).

Коэффициент ослабления входного синфазного сигнала ДУ (фиг.2), например, для выхода 13 определяется отношением

где - коэффициент усиления дифференциального сигнала uвх;

uвх=uc1-uc2 - входной дифференциальный сигнал ДУ;

uвых.1 - выходное напряжение на первом 13 выходе, обусловленное дифференциальным напряжением uвх;

- коэффициент преобразования входного синфазного сигнала uc1=uc2=uc в выходное напряжение на первом 13 выходе ДУ.

По определению

где iк10 - приращение коллекторного тока транзистора 10, обусловленное дифференциальным сигналом uвх. Причем

где rэi=φт/Iэi - дифференциальное сопротивление эмиттерного перехода i-го транзистора при статическом токе эмиттера Iэi=I0;

φт≈25 мВ - температурный потенциал.

Поэтому коэффициент усиления по напряжению для входного дифференциального сигнала ДУ (фиг.2)

Если токи двухполюсников 3 и 7 одинаковы (I3=I7=2I0), то в первом приближении

Рассмотрим далее факторы, влияющие на передачу синфазного сигнала со входов ДУ Вх.1, Вх.2 на его выход 13. Изменение uc1=uc2=uc3 (фиг.2) приводит к изменению токов через выходные сопротивления r3 и r7 двухполюсников 3 и 7:

где , .

Это приводит к появлению приращений коллекторных токов транзисторов 1 и 2, а также транзисторов 5 и 6:

Приращения токов iк5 и iк6 поступают на входы токовых зеркал 17 и 18 и, далее, в эмиттеры транзисторов 10 и 11. Если коэффициенты передачи по току токовых зеркал 17 и 18 близки к единице (Кi12.17=1, Ki12.18=1), то в эмиттерной цепи транзисторов 10 и 11 происходит вычитание двух близких по величине токов iк1 и iк5 (iк2 и iк6), обусловленных влиянием синфазных составляющих uc1, uc2 входного сигнала:

или после преобразований

где α1≈1, α2≈1 - коэффициенты усиления по току эмиттеров транзисторов 1 и 2;

Ki12.17=1, Ki12.18=1 - коэффициенты усиления по току токовых зеркал 17, 18.

Таким образом, коэффициент преобразования входного синфазного сигнала Ксф для выхода 13 и Кос.сф ДУ (фиг.2):

где .

Учитывая, что в ДУ-прототипе определяется формулой

из (15) и (16) находим, что в заявляемом ДУ Кос.сф улучшается в Nc-раз, где

Анализ уравнения (17) показывает, что при α5=α1, r3=r7, Ki12.17=1 за счет вычитания в нагрузке R21 составляющих ошибки, обусловленной синфазным сигналом на входах ДУ, общее ослабление синфазных сигналов ДУ (фиг.2) повышается. В усилителе-прототипе этот эффект отсутствует. Поэтому передача синфазного сигнала на выход 13 ДУ-прототипа более значительна и, как следствие, его Кос.сф принимает на один-два порядка меньшее значение.

Результаты компьютерного моделирования (фиг.5) подтверждают данный теоретический вывод - заявляемый ДУ в сравнении с прототипом имеет на 80 дБ (т.е. 104) лучший коэффициент ослабления входных синфазных сигналов. Кроме этого его дифференциальный коэффициент усиления не менее чем на 4 дБ выше, чем у ДУ-прототипа.

Источники информации

1. Патент США №6.583.668, fig.5

2. Патент США №4.511.852, fig.6

3. Патент США №7.436.262, fig.4

4. Патент США №5.966.050, fig.6

5. Патентная заявка США 2006/0181348

6. Патент США №6.917.257, fig.1

7. Патент США №6.172.551, fig.3B

8. Патент США №6.262.628

9. Патент США №4.331.929

10. Патент США №5.936.468

11. Патентная заявка США 2009/0051439

12. Ав. свид. СССР №681538

13. Патент США №6.891.405, fig.1

14. Патент JP 2004040157

Дифференциальный усилитель с повышенным ослаблением входного синфазного сигнала, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых связаны друг с другом и через первый (3) токостабилизирующий двухполюсник подключены к первой (4) шине источника питания, третий (5) и четвертый (6) входные транзисторы, эмиттеры которых объединены и через второй (7) токостабилизирующий двухполюсник подключены к первой (4) шине источника питания, причем база третьего (5) входного транзистора соединена с первым (8) входом устройства и базой первого (1) входного транзистора, база четвертого (6) входного транзистора соединена со вторым (9) входом устройства и базой второго (2) входного транзистора, первый (10) и второй (11) выходные транзисторы, базы которых объединены и подключены к источнику вспомогательного напряжения (12), эмиттер первого (10) выходного транзистора соединен с коллектором первого (1) входного транзистора, эмиттер второго (11) выходного транзистора соединен с коллектором второго (2) входного транзистора, коллектор первого 10 выходного транзистора соединен с первым (13) выходом устройства и первым входом цепи нагрузки (14), согласованной со второй (15) шиной источника питания, коллектор второго (11) выходного транзистора соединен со вторым (16) выходом устройства и вторым входом цепи нагрузки (14), согласованной со второй (15) шиной источника питания, отличающийся тем, что коллектор третьего (5) входного транзистора соединен со входом первого (17) дополнительного токового зеркала, согласованного со второй (15) шиной источника питания, коллектор четвертого (6) входного транзистора соединен со входом второго (18) дополнительного токового зеркала, согласованного со второй (15) шиной источника питания, выход первого (17) дополнительного токового зеркала подключен к эмиттеру второго (11) выходного транзистора и через третий (19) токостабилизирующий двухполюсник связан с первой (4) шиной источника питания, выход второго (18) дополнительного токового зеркала соединен с эмиттером первого (10) выходного транзистора и через четвертый (20) токостабилизирующий двухполюсник соединен с первой (4) шиной источника питания.