Аналоговый смеситель двух сигналов

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи и может использоваться в структуре радиоприемных устройств ВЧ и СВЧ диапазонов. Технический результат: обеспечение в АС малых значений постоянной составляющей выходного синфазного напряжения Uвых.с≈0 и его высокой стабильности при температурных и иных внешних воздействиях, а также технологических погрешностях изготовления элементов. Дополнительный технический результат: повышение коэффициента усиления (коэффициента преобразования входных сигналов fx, fy) AC для основных гармоник его выходного напряжения. Аналоговый смеситель двух сигналов содержит с первого по четвертый входные транзисторы, преобразователь «напряжение-ток», первый и второй двухполюсники коллекторной нагрузки, первый и второй выходные транзисторы, первый и второй источники опорного тока, первый и второй резисторы обратной связи. 10 ил.

Реферат

Предлагаемое изобретение относится к области радиотехники и связи и может использоваться в структуре радиоприемных устройств ВЧ и СВЧ диапазонов.

В современных системах телекоммуникаций в качестве аналоговых смесителей двух сигналов (АС) находят применение различные модификации перемножающей ячейки Джильберта [1-24] (термин «ячейка Джильберта» широко используется в микроэлектронике, см., например, патент №7.054.609, и обозначает «перемножающую» архитектуру на основе двух дифференциальных каскадов с перекрестным включением коллекторов входных транзисторов).

Для согласования потенциалов выходов классического АС Джильберта с последующим функциональным узлом в известных устройствах связи применяются выходные эмиттерные повторители (патенты US 7,403,758 fig.2, US 5.684.419 fig.3 и др.), которые, однако, вносят дополнительные статические погрешности преобразования сигналов.

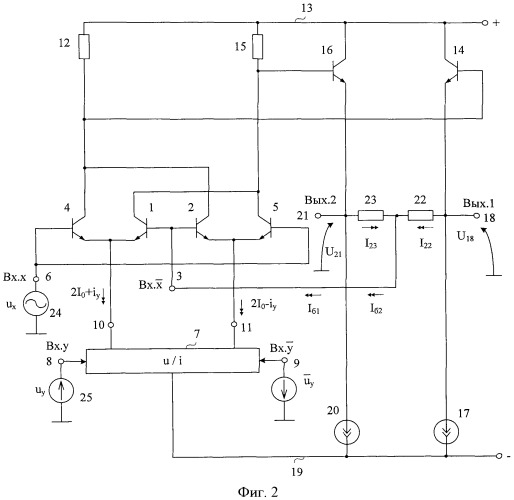

Ближайшим прототипом заявляемого устройства является аналоговый смеситель двух сигналов фиг.1, представленный в патенте US 5.684.419 fig.3 (данная архитектура присутствует также в патенте US 7.403.758 fig.2 и др.). Он содержит первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 входу канала «X», третий 4 и четвертый 5 входные транзистора, базы которых подключены ко второму 6 входу канала «X», преобразователь «напряжение-ток» 7, имеющий первый 8 и второй 9 входы канала «Y», а также первый 10 и второй 11 токовые выходы, причем первый 10 токовый выход преобразователя «напряжение-ток» 7 соединен с объединенными эмиттерами первого 1 и третьего 4 входных транзисторов, а второй 11 токовый выход преобразователя «напряжение-ток» 7 соединен с объединенными эмиттерами второго 2 и четвертого 5 входных транзисторов, первый 12 двухполюсник коллекторной нагрузки, включенный между первой 13 шиной источника питания и объединенными коллекторами второго 2 и третьего 4 входных транзисторов, связанными с базой первого 14 выходного транзистора, второй 15 двухполюсник коллекторной нагрузки, включенный между первой 13 шиной источника питания и объединенными коллекторами первого 1 и четвертого 5 входных транзисторов, связанными с базой второго 16 выходного транзистора, первый 17 источник опорного тока, включенный между эмиттером первого 14 выходного транзистора, связанного с первым 18 выходом устройства и второй 19 шиной источника питания, второй 20 источник опорного тока, включенный между эмиттером второго 16 выходного транзистора, связанного со вторым 21 выходом устройства и второй 19 шиной источника питания, связанной с эмиттерной цепью преобразователя «напряжение-ток» 7, причем коллекторы первого 14 и второго 16 выходных транзисторов подключены к первой 13 шине источников питания.

Существенный недостаток известного смесителя состоит в том, что он имеет нестабильный уровень выходного синфазного напряжения (Uвых.с=(Uвых.1+Uвых.2)/2. Причем численные значения Uвых.с существенно отличаются от нуля и зависят как от температурных, так и режимных изменений в схеме АС (напряжений питания, разброса сопротивлений резисторов нагрузки, токов источников опорного тока и т.п.). Это не позволяет обеспечить эффективное использование динамического диапазона АС, который принимает наибольшее значение при Uвых.с=0.

Основная задача предлагаемого изобретения состоит в обеспечении в АС малых значений постоянной составляющей выходного синфазного напряжения Uвых.c≈0 и его высокой стабильности при температурных и иных внешних воздействиях, а также технологических погрешностях изготовления элементов.

Дополнительная задача - повышение коэффициента усиления (коэффициента преобразования входных сигналов fx, fy) AC для основных гармоник его выходного напряжения.

Поставленные задачи решаются тем, что в аналоговом смесителе двух сигналов, содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 входу канала «X», третий 4 и четвертый 5 входные транзистора, базы которых подключены ко второму 6 входу канала «X», преобразователь «напряжение-ток» 7, имеющий первый 8 и второй 9 входы канала «Y», а также первый 10 и второй 11 токовые выходы, причем первый 10 токовый выход преобразователя «напряжение-ток» 7 соединен с объединенными эмиттерами первого 1 и третьего 4 входных транзисторов, а второй 11 токовый выход преобразователя «напряжение-ток» 7 соединен с объединенными эмиттерами второго 2 и четвертого 5 входных транзисторов, первый 12 двухполюсник коллекторной нагрузки, включенный между первой 13 шиной источника питания и объединенными коллекторами второго 2 и третьего 4 входных транзисторов, связанными с базой первого 14 выходного транзистора, второй 15 двухполюсник коллекторной нагрузки, включенный между первой 13 шиной источника питания и объединенными коллекторами первого 1 и четвертого 5 входных транзисторов, связанными с базой второго 16 выходного транзистора, первый 17 источник опорного тока, включенный между эмиттером первого 14 выходного транзистора, связанного с первым 18 выходом устройства и второй 19 шиной источника питания, второй 20 источник опорного тока, включенный между эмиттером второго 16 выходного транзистора, связанного со вторым 21 выходом устройства и второй 19 шиной источника питания, связанной с эмиттерной цепью преобразователя «напряжение-ток» 7, причем коллекторы первого 14 и второго 16 выходных транзисторов подключены к первой 13 шине источников питания, предусмотрены новые элементы и связи - первый 18 выход устройства связан с первым 3 входом канала «X» через первый 22 резистор обратной связи, а второй 21 выход устройства связан с первым 3 входом канала «X» через второй 23 резистор обратной связи.

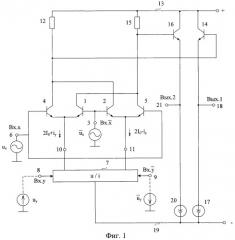

На чертеже фиг.1 представлена схема АС-прототипа, на которой преобразователь «напряжение-ток» 7 показан в виде функционального узла, реализуемого по традиционным схемам, например, на базе дифференциального каскада с местной отрицательной обратной связью (фиг.8).

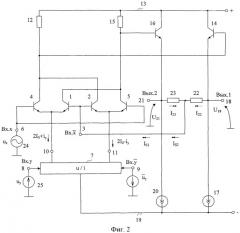

На чертеже фиг.2 представлена схема заявляемого АС в соответствии с формулой изобретения.

На чертеже фиг.3 представлена схема АС-прототипа в среде Cadance на моделях SiGe интегральных транзисторов.

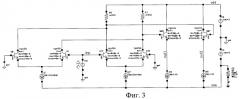

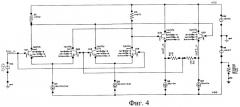

На чертеже фиг.4 представлена схема предлагаемого смесителя в среде Cadence на моделях SiGe интегральных транзисторов при изменении выходных токов преобразователя 7 на величину Ivar=500 мкА (управление по каналу «Y»: I4=2 мА+Ivar; I5=2 мА-Ivаr).

На чертеже фиг.5 приведена зависимость выходного дифференциального напряжения смесителя фиг.4 от напряжения по каналу «X» при разных напряжениях (токах управления Ivar) канала «Y».

На чертеже фиг.6 показаны зависимости модуля коэффициента усиления по напряжению Кy сравниваемых смесителей фиг.3 и фиг.4 от тока управления (Ivar) по каналу «Y».

На чертеже фиг.7 приведен график зависимости погрешности перемножения двух сигналов сравниваемых схем фиг.3 и фиг.4 в режиме управляемого усилителя.

На чертеже фиг.8 показана схема АС-прототипа с реальным выполнением преобразователя «напряжение-ток» 7 на основе дополнительных дифференциальных каскадов на транзисторах Q43, Q42, Q44, Q45.

На чертеже фиг.9 показана схема заявляемого АС с таким же выполнением преобразователя «напряжение-ток» 7, как и в схеме фиг.8.

На чертеже фиг.10 приведена зависимость амплитуды выходной гармоники fx+fy 250 МГц от управляющего напряжения канала «Y» сравниваемых схем фиг.8, фиг.9 при fx=100 МГц, fy=150 МГц.

Заявляемый смеситель двух сигналов фиг.2 содержит первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 входу канала «X», третий 4 и четвертый 5 входные транзисторы, базы которых подключены ко второму 6 входу канала «X», преобразователь «напряжение-ток» 7, имеющий первый 8 и второй 9 входы канала «Y», а также первый 10 и второй 11 токовые выходы, причем первый 10 токовый выход преобразователя «напряжение-ток» 7 соединен с объединенными эмиттерами первого 1 и третьего 4 входных транзисторов, а второй 11 токовый выход преобразователя «напряжение-ток» 7 соединен с объединенными эмиттерами второго 2 и четвертого 5 входных транзисторов, первый 12 двухполюсник коллекторной нагрузки, включенный между первой 13 шиной источника питания и объединенными коллекторами второго 2 и третьего 4 входных транзисторов, связанными с базой первого 14 выходного транзистора, второй 15 двухполюсник коллекторной нагрузки, включенный между первой 13 шиной источника питания и объединенными коллекторами первого 1 и четвертого 5 входных транзисторов, связанными с базой второго 16 выходного транзистора, первый 17 источник опорного тока, включенный между эмиттером первого 14 выходного транзистора, связанного с первым 18 выходом устройства и второй 19 шиной источника питания, второй 20 источник опорного тока, включенный между эмиттером второго 16 выходного транзистора, связанного со вторым 21 выходом устройства и второй 19 шиной источника питания, связанной с эмиттерной цепью преобразователя «напряжение-ток» 7, причем коллекторы первого 14 и второго 16 выходных транзисторов подключены к первой 13 шине источников питания. Первый 18 выход устройства связан с первым 3 входом канала «X» через первый 22 резистор обратной связи, а второй 21 выход устройства связан с первым 3 входом канала «X» через второй 23 резистор обратной связи.

Рассмотрим работу АС фиг.2.

В статическом режиме (когда входные напряжения каналов «X» и «Y» равны нулю ux=0, uy=0, при идентичных транзисторах 1, 2, 4 и 5 за счет отрицательной обратной связи по синфазному сигналу через транзисторы 1, 2 и 16, 14 уровень статических напряжений на выходах АС 21 и 18 относительно общей шины также близок к нулю:

где I22, I23 - статические токи в резисторах 22 и 23;

I22≈I23≈Iб1≈б2=10÷20 мкА (для типовых интегральных транзисторов и их статических токов при коэффициенте усиления по току базы β1≈β2=80÷100);

Iб1≈Iб2 - токи базы транзисторов 1 и 2.

Если выбрать R23=R22=200÷500 Ом, то из (1), (2) следует, что в заявляемом AC Uвых.с≈2÷5 мВ. Это позволяет обеспечить непосредственное подключение выходов 18 и 21 АС фиг.2 к последующему функциональному узлу устройства связи, в котором АС используется, и не заботиться о согласовании их статических режимов.

Следует также заметить, что в схеме фиг.2 двухполюсники нагрузки 12 и 15 могут быть выполнены в виде транзисторных источников тока, что существенно повышает коэффициент усиления АС, а также его коэффициент преобразования амплитуды ux в амплитуды выходных гармоник с частотами fx+fy, fy-fx. Такой режим невозможен в АС-прототипе фиг.1, так как применение источников тока в качестве двухполюсников нагрузки 12 и 15 приведет к насыщению (или отсечке) транзисторов 1-5 и, следовательно, к нарушению работоспособности устройства. В заявляемом АС с источниками тока в качестве двухполюсников 12, 15 обеспечивается активный режим транзисторов 1÷5 цепью отрицательной обратной связи.

Далее, в качестве транзисторов 16 и 14 в схеме фиг.2 могут применяться (для уменьшения влияния низкоомной Rн=50 Ом нагрузки) составные биполярные транзисторы или их полевые аналоги. Это также не повлияет на работу схемы фиг.2 благодаря наличию отрицательной обратной связи.

Предлагаемая схема имеет базовые свойства классической ячейки Джильберта фиг.5, фиг.6, фиг.7, но характеризуется близким к нулю уровнем выходных статических напряжений. При этом за счет использования в качестве двухполюсников 12 и 15 источников тока предельные коэффициенты преобразования схемы АС фиг.2 повышаются (в сравнении с прототипом) более чем на порядок.

Синусоидальные напряжения первого смешиваемого сигнала ux (на входе 6 канала «X») и второго смешиваемого сигнала uy (на входах канала «Y» 8, 9) «перемножаются» традиционным образом в ячейке Джильберта 1. Об этом свидетельствуют чертежи фиг.5, свидетельствующие о «перемножающих» свойствах заявляемого устройства.

Предлагаемое техническое решение имеет существенные преимущества в сравнении с классическими смесителями сигналов Джильберта, защищенными более 300 патентами ведущих микроэлектронных фирм мира.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US №2008/113644

2. Патентная заявка US №2006/0232334, fig.1

3. Патент US №4.965.528, fig.2

4. Патент US №6.744.308

5. Патент US №7.633.328

6. Патент US №7.110.740

7. Патентная заявка US №2009/0085663, fig.2

8. Патент US №7.514.981, fig.1

9. Авт.св. СССР №642843

10. Патент US №5.933.771, fig.2

11. Патент US №6.016.079, fig.4

12. Патент US №5.057.784

13. Патент US №4.286.226

14. Патентная заявка US №2008/0261552, fig.1

15. Патент US №6.373.345, fig.2

16. Патентная заявка US №2010/0164595, fig.2

17. Патентная заявка US №2010/0141325

18. Патент US №4.344.188, fig.1, fig.3

19. Патент ЕР 1455441

20. Патент US №7.812.775, fig.20, fig.16

21. Патент ЕР 2235559, fig.3

22. Патент US №7.676.212, fig.2

23. Патентная заявка US №2008/0180156, fig.1, fig.5

24. Патент US №5.825.231, fig.1

Аналоговый смеситель двух сигналов, содержащий первый (1) и второй (2) входные транзисторы, базы которых подключены к первому (3) входу канала «X», третий (4) и четвертый (5) входные транзисторы, базы которых подключены ко второму (6) входу канала «X», преобразователь «напряжение-ток» (7), имеющий первый (8) и второй (9) входы канала «Y», а также первый (10) и второй (11) токовые выходы, причем первый (10) токовый выход преобразователя «напряжение-ток» (7) соединен с объединенными эмиттерами первого (1) и третьего (4) входных транзисторов, а второй (11) токовый выход преобразователя «напряжение-ток» (7) соединен с объединенными эмиттерами второго (2) и четвертого (5) входных транзисторов, первый (12) двухполюсник коллекторной нагрузки, включенный между первой (13) шиной источника питания и объединенными коллекторами второго (2) и третьего (4) входных транзисторов, связанными с базой первого (14) выходного транзистора, второй (15) двухполюсник коллекторной нагрузки, включенный между первой (13) шиной источника питания и объединенными коллекторами первого (1) и четвертого (5) входных транзисторов, связанными с базой второго (16) выходного транзистора, первый (17) источник опорного тока, включенный между эмиттером первого (14) выходного транзистора, связанного с первым (18) выходом устройства, и второй (19) шиной источника питания, второй (20) источник опорного тока, включенный между эмиттером второго (16) выходного транзистора, связанного со вторым (21) выходом устройства, и второй (19) шиной источника питания, связанной с эмиттерной цепью преобразователя «напряжение-ток» (7), причем коллекторы первого (14) и второго (16) выходных транзисторов подключены к первой (13) шине источников питания, отличающийся тем, что первый (18) выход устройства связан с первым (3) входом канала «X» через первый (22) резистор обратной связи, а второй (21) выход устройства связан с первым (3) входом канала «X» через второй (23) резистор обратной связи.