Устройство коммуникационного интерфейса

Иллюстрации

Показать всеИзобретение относится к цифровой вычислительной технике, а именно к высокоскоростным коммуникационным системам для высокопроизводительных многопроцессорных вычислительных систем. Техническим результатом является снижение энергопотребления и повышение быстродействия, что обеспечивает расширение области применения устройства коммуникационного интерфейса на базе DS-кодирования сигналов. Устройство коммуникационного интерфейса содержит блок выдачи данных, блок приема данных, блок управления, блок управления потоком данных и связи, причем в блок выдачи данных введен буфер передачи символов и новые связи, в блок приема данных введены блок формирования сигналов, детектор рассоединения, блок преобразования кода, детектор начала приема и блок перехода временного домена и новые связи. 2 з.п. ф-лы, 17 ил., 11 табл.

Реферат

Настоящее изобретение относится к цифровой вычислительной технике, а именно к высокоскоростным коммуникационным системам для высокопроизводительных многопроцессорных вычислительных систем с распределенной обработкой информации. Данное устройство предназначено, в частности, для применения при построении многопроцессорных вычислительных систем с распределенной архитектурой, используемых, в том числе, в бортовых вычислительных комплексах.

В качестве аналога из уровня техники известно устройство с параллельным коммуникационным интерфейсом [авт.свид. СССР №1211747. Устройство для сопряжения процессоров в многопроцессорной вычислительной системе / Горбачев С.В., Сакун Л.И. Заявлено 04.07.1984. Опубл. бюл. №6, 1986], содержащее блок передачи данных, блок приема данных, блок управления, блок определения готовности приемников, блок выделения приоритетного запроса.

В силу параллельного характера используемого коммуникационного интерфейса он имеет громоздкую физическую реализацию, так как кроме линий синхронизации содержит большое число линий приема и передачи данных. Возникающие проблемы со сдвигом по фазе синхросигнала и битов данных на множестве линий данных из-за их физической неоднородности приводят к тому, что известный параллельный интерфейс может использоваться на ограниченных расстояниях (до нескольких метров) и имеет ограниченное быстродействие. Таким образом, недостаток этого устройства состоит в ограниченной области применения, что вызвано ограничениями по длине и быстродействию, а также из-за большого энергопотребления при использовании параллельной синхронизации. Соответствующие ограничения присутствуют и в отношении надежности устройства.

Ближайшим аналогом к заявляемому устройству является устройство коммуникационного интерфейса [patent GB №91304711.4. Int. Cl.5 H04L 1/00. Communication interface for serial transmission of variable length data tokens / Priority 25.05.90, №9011700. Data of filing 24.05.91. Data of publication 27.11.91. Bulletin 91/48 of European Patent Office. Publication number 0458648 A2] для использования в коммуникационной системе, соединяющей как минимум два компьютера, причем устройство коммуникационного интерфейса, содержащее блок выдачи данных, блок приема данных, блок управления и блок управления потоком данных, выход запроса на выдачу символа управления потоком которого соединен с одноименным входом блока выдачи данных, выход готовности выдачи символа управления потоком которого соединен с одноименным входом блока управления потоком данных, входы подтверждения приема символа управления потоком и подтверждения приема информационного символа которого соединены соответственно с одноименными входами блока управления и одноименными выходами блока приема данных, выход ошибки кодировки символа которого является выходом ошибки кодировки символа системного интерфейса устройства и соединен с одноименным входом блока управления, первый и второй выходы сброса которого соединены с входами сброса соответственно блока выдачи данных и блока приема данных, входы данных и стробирования которого являются соответственно входами данных и стробирования интерфейса устройства с каналом приема информации, выходы данных и стробирования интерфейса устройства с каналом выдачи информации являются соответственно выходами данных и стробирования блока выдачи данных, вход синхронизации выдачи данных которого является входом синхронизации выдачи данных системного интерфейса устройства, вход чтения данных системного интерфейса устройства является одноименным входом блока приема данных, выходы данных для приема и готовности данных для приема которого являются соответствующими выходами системного интерфейса устройства, выход ошибки кредитования системного интерфейса устройства является одноименным выходом блока управления потоком данных и соединен с одноименным входом блока управления, третий выход сброса которого соединен с входом сброса блока управления потоком данных, входы подтверждения выдачи информационного символа и разрешения приема данных которого соединены с одноименными выходами соответственно блока выдачи данных и блока приема данных, вход сброса системного интерфейса устройства является входом сброса блока управления, выход готовности выдачи данных системного интерфейса устройства является одноименным выходом блока выдачи данных, входы записи и данных для выдачи системного интерфейса устройства являются соответствующими входами блока выдачи данных, который содержит блок арбитража выдачи символов, формирователь символа, блок DS-кодирования символа, буфер выдачи данных, выход готовности выдачи данных которого является одноименным выходом блока выдачи данных, входы записи и данных для выдачи которого являются соответствующими входами буфера выдачи данных, выход которого соединен с входом информационного символа блока арбитража выдачи символов, выходы подтверждения выдачи информационного символа и готовности выдачи символа управления потоком которого являются соответственно одноименными выходами блока выдачи данных, вход запроса на выдачу символа управления потоком которого является одноименным входом блока арбитража выдачи символов, вход сброса которого является входом сброса блока выдачи данных и соединен с входами сброса формирователя символа, блока DS-кодирования символа и буфера выдачи данных, вход готовности передачи данных которого соединен с одноименным выходом блока арбитража выдачи символов, вход синхронизации которого соединен с входом синхронизации буфера выдачи данных и является входом локальной синхронизации блока выдачи данных, выходы данных и стробирования которого являются одноименными выходами блока DS-кодирования символа, вход полного кода символа которого соединен с одноименным выходом формирователя символа; блок приема данных содержит первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь в параллельный код, буфер приема данных, дешифратор преобразованного кода, причем вход локальной синхронизации блока приема данных является входом синхронизации буфера приема данных и дешифратора преобразованного кода, выходы ошибки кодировки символа и подтверждение приема символа управления потоком которого являются одноименными выходами блока приема данных, выход данных для приема которого является одноименным выходом буфера приема данных, выходы разрешения приема данных и готовности данных для приема которого являются соответственно одноименными выходами блока приема данных, вход чтения данных которого является входом чтения буфера приема данных, информационный вход которого соединен с выходом данных дешифратора преобразованного кода, выход подтверждения приема информационного символа которого соединен с одноименным входом буфера приема данных и является одноименным выходом блока приема данных, вход сброса которого является входом сброса дешифратора преобразованного кода и соединен с входом сброса буфера приема данных, вход данных блока приема данных соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход стробирования блока приема данных соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

В данном устройстве использование DS-кодирования позволяет несколько снизить энергопотребление без снижения скоростных характеристик по сравнению с ранее известными аналогами за счет того, что в один момент времени может происходить изменение только одного сигнала, либо на линии стробирования S, либо на линии данных D коммуникационного интерфейса. Используемый в устройстве способ DS-кодирования характеризуется тем, что сигналы данных на линии данных D являются последовательным потоком битов данных, представляющих собой последовательность изменений сигнала только когда биты данных изменяют свое значение, в то время как сигнал строба на линии стробирования S изменяет значение только на границе битов в те моменты, когда сигнал данных не изменяет свое состояние, таким образом, исключая одновременные изменения в последовательном потоке сигналов данных и стробов. В блоке приема данных путем объединения D-сигнала и S-сигнала по функции ИСКЛЮЧАЮЩЕЕ ИЛИ (XOR) формируется синхросигнал, изменяющий свое состояние в каждом битовом интервале, что позволяет его использование для приема сигналов данных с линии данных D и дальнейшей обработки битовых данных в устройстве коммуникационного интерфейса.

Недостатком этого устройства по-прежнему остается ограниченное быстродействие и относительно высокое энергопотребление. Это связано с тем, что все элементы устройства работают на одной локальной частоте, на которой осуществляется как выдача битовых данных, так и их прием, и последующее распознавание символа данных. Поэтому возможность повышения быстродействия устройства значительно ограничивается из-за пропорционального роста энергопотребления элементов всего устройства. При этом в домене формирования синхросигнала для приема битов данных имеет место эффект «завала фронтов» синхросигнала, поскольку он вырабатывается по функции XOR из сигналов с входных линий D и S коммуникационного интерфейса. В силу большой протяженности этих линий (порядка нескольких метров) они обладают значительными паразитными емкостями и индуктивностями, которые вызывают завал фронтов D- и S-сигналов. С другой стороны, формируемый в приемнике устройства синхросигнал имеет длинный путь (clock path), так как вырабатывается на основе D- и S-сигналов, поступающих из передатчика другого устройства через коммуникационный канал, что ограничивает возможность уменьшения периода изменения сигналов. Эти причины не позволяют повысить скорость передачи данных и существенно ограничивают быстродействие всего устройства коммуникационного интерфейса. В свою очередь, наличие в схеме устройства синхросигналов с продолжительным временем перехода от одного уровня к другому, в течение которого происходит дополнительное рассеивание энергии на триггерах и логических элементах, приводит к излишнему росту энергопотребления. Это сужает область применения устройства и, в частности, ограничивает использование в бортовых системах и для встраиваемых применений. Это также приводит к тому, что соответствующие ограничения присутствуют и в отношении надежности устройства.

Техническим результатом предлагаемого изобретения является расширение области применения устройства за счет снижения энергопотребления и обеспечения возможности повышения быстродействия путем минимизации числа триггеров и других элементов устройства, работающих на частоте передачи данных, более высокой по сравнению с локальной частотой, а также вследствие устранения завала фронтов синхросигнала при приеме битов данных и повышения скорости распознавания символов данных из потока принимаемых битов данных. Также имеет место в качестве технического результата возможность относительного повышения надежности устройства.

Технический результат достигается тем, что в предложенном устройстве коммуникационного интерфейса, содержащем блок выдачи данных, блок приема данных, блок управления и блок управления потоком данных, выход запроса на выдачу символа управления потоком которого соединен с одноименным входом блока выдачи данных, выход готовности выдачи символа управления потоком которого соединен с одноименным входом блока управления потоком данных, входы подтверждения приема символа управления потоком и подтверждения приема информационного символа которого соединены соответственно с одноименными входами блока управления и одноименными выходами блока приема данных, выход ошибки кодировки символа которого является выходом ошибки кодировки символа системного интерфейса устройства и соединен с одноименным входом блока управления, первый и второй выходы сброса которого соединены с входами сброса соответственно блока выдачи данных и блока приема данных, входы данных и стробирования которого являются соответственно входами данных и стробирования интерфейса устройства с каналом приема информации, выходы данных и стробирования интерфейса устройства с каналом выдачи информации являются соответственно выходами данных и стробирования блока выдачи данных, вход синхронизации выдачи данных которого является входом синхронизации выдачи данных системного интерфейса устройства, вход чтения данных системного интерфейса устройства является одноименным входом блока приема данных, выходы данных для приема и готовности данных для приема которого являются соответствующими выходами системного интерфейса устройства, выход ошибки кредитования системного интерфейса устройства является одноименным выходом блока управления потоком данных и соединен с одноименным входом блока управления, третий выход сброса которого соединен с входом сброса блока управления потоком данных, входы подтверждения выдачи информационного символа и разрешения приема данных которого соединены с одноименными выходами соответственно блока выдачи данных и блока приема данных, вход сброса системного интерфейса устройства является входом сброса блока управления, выход готовности выдачи данных системного интерфейса устройства является одноименным выходом блока выдачи данных, входы записи и данных для выдачи системного интерфейса устройства являются соответствующими входами блока выдачи данных, который содержит блок арбитража выдачи символов, формирователь символа, блок DS-кодирования символа, буфер выдачи данных, выход готовности выдачи данных которого является одноименным выходом блока выдачи данных, входы записи и данных для выдачи которого являются соответствующими входами буфера выдачи данных, выход которого соединен с входом информационного символа блока арбитража выдачи символов, выходы подтверждения выдачи информационного символа и готовности выдачи символа управления потоком которого являются соответственно одноименными выходами блока выдачи данных, вход запроса на выдачу символа управления потоком которого является одноименным входом блока арбитража выдачи символов, вход сброса которого является входом сброса блока выдачи данных и соединен с входами сброса формирователя символа, блока DS-кодирования символа и буфера выдачи данных, вход готовности передачи данных которого соединен с одноименным выходом блока арбитража выдачи символов, вход синхронизации которого соединен с входом синхронизации буфера выдачи данных и является входом локальной синхронизации блока выдачи данных, выходы данных и стробирования которого являются одноименными выходами блока DS-кодирования символа, вход полного кода символа которого соединен с одноименным выходом формирователя символа; блок приема данных содержит первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь в параллельный код, буфер приема данных, дешифратор преобразованного кода, причем вход локальной синхронизации блока приема данных является входом синхронизации буфера приема данных и дешифратора преобразованного кода, выходы ошибки кодировки символа и подтверждение приема символа управления потоком которого являются одноименными выходами блока приема данных, выход данных для приема которого является одноименным выходом буфера приема данных, выходы разрешения приема данных и готовности данных для приема которого являются соответственно одноименными выходами блока приема данных, вход чтения данных которого является входом чтения буфера приема данных, информационный вход которого соединен с выходом данных дешифратора преобразованного кода, выход подтверждения приема информационного символа которого соединен с одноименным входом буфера приема данных и является одноименным выходом блока приема данных, вход сброса которого является входом сброса дешифратора преобразованного кода и соединен с входом сброса буфера приема данных, вход данных блока приема данных соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход стробирования блока приема данных соединен со вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, введено соединение входа локальной синхронизации системного интерфейса устройства с входами локальной синхронизации блока управления, блока управления потоком данных, блока приема данных, блока выдачи данных, вход разрешения передачи символов управления потоком которого соединен с одноименным выходом блока управления, выход ошибки рассоединения блока приема данных соединен с одноименным входом блока управления и является выходом ошибки рассоединения системного интерфейса устройства, выход установления соединения системного интерфейса устройства является выходом установления соединения блока приема данных и соединен с одноименным входом блока управления, причем в блок приема данных введены блок формирования сигналов, детектор рассоединения, блок преобразования кода, детектор начала приема и блок перехода временного домена, в блок выдачи данных введен буфер передачи символов, вход локальной синхронизации которого соединен с входом локальной синхронизации блока выдачи данных, вход разрешения передачи символа управления потоком которого является одноименным входом блока арбитража выдачи символов, вход синхронизации выдачи данных блока выдачи данных является одноименным входом буфера передачи символов и соединен с входами синхронизации формирователя символа и блока DS-кодирования символа, вход сброса блока выдачи данных соединен с одноименным входом буфера передачи символов, выход готовности передачи символов которого соединен с одноименным входом блока арбитража выдачи символов, выходы записи и символов которого соединены соответственно с одноименными входами буфера передачи символов, выход которого соединен с информационным входом формирователя символа, выходы длины символа и записи длины символа которого соединены соответственно с одноименными входами блока DS-кодирования символа, выход готовности передачи символа которого соединен с одноименными входами формирователя символа и буфера передачи символов; выход ошибки рассоединения блока приема данных является выходом детектора рассоединения, управляющий вход которого соединен с выходом признака изменения уровня первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с входом синхронизации блока формирования сигналов и входом синхронизации детектора начала приема, выход корректировки фронта синхросигнала которого соединен с одноименным входом блока формирования сигналов, вход разрешения синхронизации которого соединен с одноименным выходом детектора начала приема и является выходом установления соединения блока приема данных, информационный выход и выход готовности преобразователя в параллельный код соединены соответственно с одноименными входами блока перехода временного домена, информационный выход и выход разрешения которого соединены соответственно с информационным входом и входом разрешения блока преобразования кода, выходы параллельного кода слова данных и разрядности слова данных которого соединены соответственно с одноименными входами дешифратора преобразованного кода, выход числа дешифрируемых битов которого соединен с одноименным входом блока преобразования кода, вход синхронизации которого соединен с входами синхронизации блока перехода временного домена, детектора рассоединения, детектора начала приема и входом локальной синхронизации блока приема данных, вход данных которого соединен с входом сигнала данных блока формирования сигналов и с информационным входом детектора начала приема, вход сброса блока приема данных соединен с управляющим входом детектора начала приема и с входами сброса детектора рассоединения, блока преобразования кода и блока формирования сигналов, выход битов данных которого соединен с одноименным входом преобразователя в параллельный код, вход синхронизации которого соединен с выходом сигнала синхронизации блока формирования сигналов.

Предпочтительно, блок формирования сигналов содержит триггер первого бита, триггер второго бита, регистр выделенных сигналов, первый триггер деления частоты, второй триггер деления частоты, первый элемент НЕ, второй элемент НЕ, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом синхронизации регистра выделенных сигналов и является выходом сигнала синхронизации блока формирования сигналов, вход синхронизации которого соединен с одноименными входами триггеров первого и второго битов, первого и второго триггеров деления частоты, вход сигнала данных блока формирования сигналов соединен с входами данных триггеров первого и второго битов, вход разрешения синхронизации блока формирования сигналов является входом разрешения регистра выделенных сигналов, входы первого и второго битов соединены соответственно с выходами триггеров первого и второго битов, выход регистра выделенных сигналов является выходом битов данных блока формирования сигналов, вход корректировки фронта синхросигнала которого является первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с выходом первого триггера деления частоты и с входом первого элемента НЕ, выход которого соединен с входом данных первого триггера деления частоты, вход сброса которого является входом сброса блока формирования сигналов и соединен с одноименным входом второго триггера деления частоты, выход которого соединен со вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом второго элемента НЕ, выход которого соединен с входом данных второго триггера деления частоты. Блок преобразования кода содержит сдвигающий регистр выборки, регистр первого байта, регистр второго байта, регистр третьего байта, регистр четвертого байта, блок сдвига данных, регистр управления сдвигом, первый сумматор, регистр управления чтением, второй сумматор, регистр константы, выход которого соединен с первым входом сложения второго сумматора, выход которого соединен с информационным входом регистра управления чтением, выход состояния которого соединен со вторым входом сложения второго сумматора, вход вычитания которого является входом числа дешифрируемых битов блока преобразования кода и соединен с первым входом сложения первого сумматора, второй вход сложения которого соединен с выходом состояния регистра управления сдвигом, информационный вход которого соединен с выходом первого сумматора, управляющий выход регистра управления сдвигом соединен с управляющим входом блока сдвига данных, выход которого является выходом параллельного кода слова данных блока преобразования кода, вход сброса которого соединен с одноименными входами регистра управления сдвигом, регистра управления чтением и сдвигового регистра выборки, вход синхронизации которого является входом синхронизации блока преобразования кода и соединен с одноименными входами регистров первого, второго, третьего и четвертого байтов, регистра управления сдвигом и регистра управления чтением, выход разрядности слова данных которого является одноименным выходом блока преобразования кода, вход разрешения которого соединен с разрешающими входами регистра управления сдвигом, регистра управления чтением и сдвигающего регистра выборки, выход которого соединен с собственным последовательным входом, с входами выборки регистров первого, второго, третьего и четвертого байтов, информационные входы которых соединены с информационным входом блока преобразования кода, выходы регистров первого, второго, третьего и четвертого байтов соединены соответственно с первым, вторым, третьим и четвертым информационными входами блока сдвига данных.

Предлагаемое изобретение предназначено для организации высокоскоростного обмена информацией между процессорными узлами или компьютерами по дуплексному последовательному коммуникационному каналу, образованному симплексными каналами выдачи и приема информации, и может быть использовано при создании высокопроизводительных многопроцессорных вычислительных систем для применения в широких областях, требующих пониженного энергопотребления и повышения быстродействия. В предлагаемом техническом решении обеспечивается возможность для повышения скорости передачи данных через коммуникационный канал, то есть выдачи и приема данных в устройстве коммуникационного интерфейса при одновременном ограничении роста энергопотребления за счет разделения всех элементов устройства на два временных домена. Первый временной домен, в который включены элементы устройства, осуществляющие подготовку выдаваемых символов данных и обработку принимаемых символов данных, работает на частоте локальной синхронизации устройства. Второй временной домен включает элементы устройства, непосредственно осуществляющие выдачу и работающие на частоте выдачи данных в коммуникационный интерфейс, а также элементы устройства, непосредственно обеспечивающие прием битов данных и работающие на частоте принимаемых сигналов из коммуникационного интерфейса. Для повышения пропускной способности коммуникационного интерфейса частота выдачи данных может быть увеличена в несколько раз по сравнению с частотой локальной синхронизации. Поскольку в данном техническом решении имеется возможность минимизировать число триггеров, работающих на максимальной частоте передачи данных, то это способствует снижению потребляемой мощности по сравнению с прототипом при одинаковых значениях скорости передачи данных. Уменьшение задержек при приеме данных за счет формирования внутренних синхросигналов без завала фронтов и одновременного выделения двух смежных битов из входной линии данных способствует увеличению скорости приема данных и снижению потребляемой мощности. Возможность декодирования из последовательности принимаемых битов данных более одного символа за один такт локальной частоты обеспечивает повышение скорости приема данных и способствует выравниванию скорости приема со скоростью выдачи бит данных. Это является одним из факторов, способствующих снижению частоты локальной синхронизации по отношению к частоте выдачи данных, что приводит к уменьшению энергопотребления при обеспечении возможности одновременного увеличения скорости передачи битов данных в коммуникационном канале по сравнению с прототипом. Таким образом, данное устройство может быть эффективно использовано для создания распределенных бортовых вычислительных комплексов, а также в различных встраиваемых применениях. Отдельные элементы устройства могут быть реализованы стандартными средствами из данной области техники, при этом только системное решение, предложенное в рамках настоящего изобретения, позволяет достигнуть соответствующего технического результата.

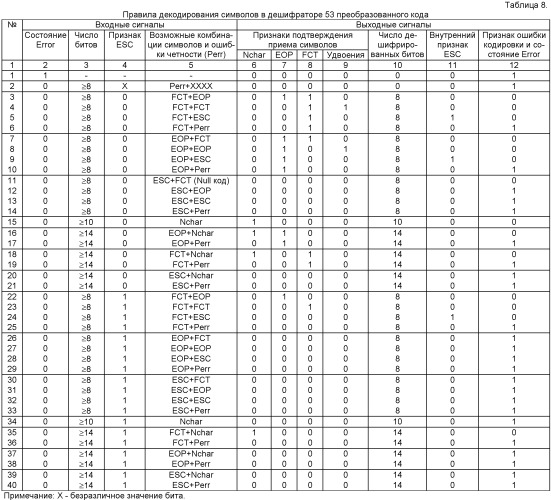

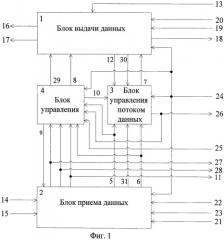

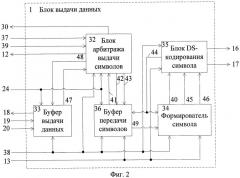

Детально сущность данного технического решения поясняется описанием со ссылками на чертежи, где на фиг.1 представлена структурная схема устройства, на фиг.2 - функциональная схема блока выдачи данных, на фиг.3 - функциональная схема блока приема данных. На фиг.4 и фиг.5 представлены возможные варианты реализации функциональных схем блока управления потоком данных и блока управления. На фиг.6 показана функциональная схема блока формирования сигналов. На фиг.7 приведена возможная реализация функциональной схемы детектора начала приема. На фиг.8 приведен пример реализации детектора рассоединения. На фиг.9 приведена структура блока преобразования кода. На фиг.10 представлена возможная реализация структуры блока DS-кодирования символа. На фиг.11 приведен граф машины состояния, описывающий режимы функционирования устройства. На фиг.12 показаны временные диаграммы, поясняющие правила формирования при DS-кодировании D- и S-сигналов в коммуникационном интерфейсе устройства. На фиг.13 показаны временные диаграммы, поясняющие работу блока формирования сигналов. На фиг.14 показаны временные диаграммы, поясняющие работу детектора рассоединения. На фиг.15 показаны области смежных символов, охватываемые битами контроля символа. На фиг.16 показаны сигналы данных и стробирования в момент запуска устройства. На фиг.17 проиллюстрирован пример графа переходов при инициализации взаимодействия через коммуникационный канал между двумя устройствами.

Как показано на фиг.1, предлагаемое устройство содержит блок 1 выдачи данных, блок 2 приема данных, блок 3 управления потоком данных, блок 4 управления, выход 5 подтверждения приема символа управления потоком, выход 6 подтверждения приема информационного символа, выход 7 запроса на выдачу символа управления потоком, первый выход 8 сброса, второй выход 9 сброса, третий выход 10 сброса, выход 11 ошибки рассоединения, выход 12 готовности выдачи символа управления потоком, вход 13 синхронизации выдачи данных, входы 14 данных и 15 стробирования, выходы 16 данных и 17 стробирования, выход 18 готовности выдачи данных, вход 19 записи, вход 20 данных для выдачи, вход 21 чтения данных, выход 22 данных для приема, выход 23 готовности данных для приема, вход 24 локальной синхронизации, вход 25 сброса, выход 26 ошибки кредитования, выход 27 ошибки кодировки символа, выход 28 установления соединения, выход 29 разрешения передачи символа управления потоком, выход 30 подтверждения выдачи информационного символа, выход 31 разрешения приема данных.

Блок 1 выдачи данных содержит (см. фиг.2) блок 32 арбитража выдачи символов, буфер 33 выдачи данных, формирователь 34 символа, блок 35 DS-кодирования символа, буфер 36 передачи символов, выход 30 подтверждения выдачи информационного символа, вход 37 разрешения передачи символа управления потоком, вход 38 сброса, выходы 16 данных и 17 стробирования, вход 39 запроса на выдачу символа управления потоком, выходы 12 готовности выдачи символа управления потоком и 18 готовности выдачи данных, входы 19 записи и 20 данных для выдачи, входы 13 синхронизации выдачи данных и 24 локальной синхронизации, выход 40 полного кода символа, выход 41 готовности передачи символов, выход 42 записи, выход 43 символа, выход 44 готовности передачи символа, выход 45 длины символа, выход 46 записи длины символа, выход 47 буфера 33 выдачи данных, выход 48 готовности передачи данных, выход 49 буфера 36 передачи символов.

Блок 2 приема данных содержит (см. фиг.3) первый элемент 50 ИСКЛЮЧАЮЩЕЕ ИЛИ, преобразователь 51 в параллельный код, буфер 52 приема данных, дешифратор 53 преобразованного кода, блок 54 формирования сигналов, детектор 55 начала приема, детектор 56 рассоединения, блок 57 перехода временного домена, блок 58 преобразования кода, входы 14 данных и 15 стробирования, выход 27 ошибки кодировки символа, выходы 22 данных для приема и 23 готовности данных для приема, вход 21 чтения данных, выход 11 ошибки рассоединения, вход 24 локальной синхронизации, вход 59 сброса, информационный выход 60, выход 61 разрешения, выход 62 данных, выход 63 признака изменения уровня, выход 64 битов данных, выход 65 сигнала синхронизации, выход 28 установления соединения, выход 66 корректировки фронта синхросигнала, выход 67 параллельного кода слова данных, выход 68 разрядности слова данных, выход 69 числа дешифрируемых битов, выход 5 подтверждение приема символа управления потоком, выход 6 подтверждения приема информационного символа, выход 31 разрешения приема данных.

Блок 3 управления потоком данных содержит (см. фиг.4) формирователь 70 запросов кредитования, счетчик 71 принятых символов, счетчик 72 переданных символов, детектор 73 ошибки кредитования, вход 74 разрешения приема данных, вход 75 сброса, вход 76 готовности выдачи символа управления потоком, вход 24 локальной синхронизации, вход 77 подтверждения приема информационного символа, вход 78 подтверждения приема символа управления потоком, вход 79 подтверждения выдачи информационного символа, выход 7 запроса на выдачу символа управления потоком, выход 26 ошибки кредитования.

Блок 4 управления содержит (см. фиг.5) регистр 80 состояния, блок 81 формирования нового состояния, формирователь 82 управляющих сигналов, блок 83 задержки, вход 24 локальной синхронизации, вход 25 сброса, вход 84 установления соединения, вход 85 ошибки кредитования, вход 86 ошибки рассоединения, вход 87 ошибки кодировки символа, первый выход 90 сброса, второй выход 91 сброса, третий выход 92 сброса, вход 88 подтверждения приема символа управления потоком, вход 89 подтверждения приема информационного символа, выход 29 разрешения передачи символа управления потоком.

Блок 54 формирования сигналов содержит (см. фиг.6) триггер 93 первого бита, триггер 94 второго бита, регистр 95 выделенных сигналов, первый триггер 96 деления частоты, второй триггер 97 деления частоты, первый элемент 98 НЕ, второй элемент 99 НЕ, второй элемент 100 ИСКЛЮЧАЮЩЕЕ ИЛИ, третий элемент 101 ИСКЛЮЧАЮЩЕЕ ИЛИ, вход 59 сброса, вход 102 сигнала данных, вход 103 синхронизации, вход 104 корректировки фронта синхросигнала, вход 105 разрешения синхронизации, выход 64 битов данных, выход 65 сигнала синхронизации.

Детектор 55 начала приема содержит (см. фиг.7) первый сдвигающий регистр 106, второй сдвигающий регистр 107, компаратор 108 нулевого символа, блок 109 константы нулевого символа, триггер 110 разрешения, триггер 111 коррекции, информационный вход 112, вход 113 синхронизации, управляющий вход 114, выход 115 разрешения синхронизации, выход 66 корректировки фронта синхросигнала.

Детектор 56 рассоединения содержит (см. фиг.8) первый 116 и второй 117 триггеры сброса, счетчик 119 тайм-аута, компаратор 121 тайм-аута, блок 120 константы тайм-аута, элемент 118 ИЛИ, триггер 266 ошибки, вход 59 сброса, управляющий вход 122, вход синхронизации 123, выход 124 детектора.

Блок 58 преобразования кода содержит (см. фиг.9) сдвигающий регистр 125 выборки, регистр 126 первого байта, регистр 127 второго байта, регистр 128 третьего байта, регистр 129 четвертого байта, блок 130 сдвига данных, регистр 131 управления сдвигом, первый сумматор 132, регистр 133 управления чтением, второй сумматор 134, регистр 135 константы, вход 59 сброса, вход 136 синхронизации, вход 137 разрешения, информационный вход 138, вход 139 числа дешифрируемых битов, выход 67 параллельного кода слова данных, выход 68 разрядности слова данных.

Блок 35 DS-кодирования символа содержит (см. фиг.10) третий сдвигающий регистр 140, указатель 141 числа битов, формирователь 142 строба, триггер 143 выдачи D-сигнала, триггер 144 выдачи S-сигнала, вход 38 сброса, вход 145 полного кода символа, вход 146 длины символа, вход 147 записи длины символа, вход 13 синхронизации выдачи данных, выход 16 данных, выход 17 стробирования, выход 44 готовности передачи символа.

На временных диаграммах (см. фиг.13) для блока 54 формирования сигналов показано: а - изменение сигнала на входе 102 синхронизации, b - состояние сигнала на входе 59 сброса, с - изменение сигнала на входе 101 сигнала данных, d - изменение состояния выхода триггера 93 первого бита, е - изменение состояния выхода триггер 94 второго бита, f - изменение сигнала на выходе первого триггера 96 деления частоты, g - изменение сигнала на выходе второго триггера 97 деления частоты, h - состояние сигнала на выходе второго элемента 100 ИСКЛЮЧАЮЩЕЕ ИЛИ, i - изменение сигнала на входе 103 корректировки фронта синхросигнала, j - изменение сигнала на выходе 65 сигнала синхронизации, k - состояние сигнала на входе 105 разрешения синхронизации, m - состояние сигнала на выходе 64 битов данных.

На временных диаграммах (см. фиг.14) для детектора 56 рассоединения показано: а - изменение сигнала на входе 123 синхронизации детектора, b - состояние сигнала на управляющем входе 122 детектора, с - изменение сигнала на выходе первого триггера 116 сброса, d - изменение состояния выхода второго триггера 117 сброса, е - изменение состояния выхода элемента 118 ИЛИ, f - изменение сигнала на выходе счетчика 119 тайм-аута, g - состояние сигнала на выходе 124 детектора, h - состояние сигнала на входе 59 сброса детектора.

Блок 1 выдачи данных предназначен для формирования и выдачи в коммуникационный интерфейс символов данных из пакетных данных, поступающих через вход данных для выдачи, соединенного с одноименным входом 20 устройства, являющимся частью системного интерфейса с хост-системой (компьютером), а также управляющих символов по требованию, поступающему с выхода 7 запроса на выдачу символа управления потоком блока 3 управления потоком данных на одноименный вход блока. Вход 19 записи системного интерфейса устройства явл