Устройство анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах

Иллюстрации

Показать всеИзобретение относится к области цифровой вычислительной техники и предназначено для моделирования комбинаторных задач при проектировании вычислительных систем (ВС), например для размещения процессов. Техническим результатом является расширение области применения устройства за счет введения средств анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах по критерию минимизации интенсивности взаимодействия процессов и данных. Устройство содержит два регистра сдвига, блок формирования перестановок (БФП), блок постоянной памяти, блок запоминания лучшего варианта (БЗЛВ), коммутатор, АЛУ, дешифратор выбора дуги, реверсивный счетчик ячеек, блок оперативной памяти, счетчик топологии, два счетчика расстояний, умножитель, сумматор, регистр минимальной длины связей, два элемента сравнения, вычитатель, триггер начала счета, триггер режима, триггер задания топологии, регистр длины связей, счетчик дуг, дешифратор блокировки дуги, регистр номера дуги, регистр минимального веса, электронную модель графа, группу из n элементов ИЛИ, группу из m элементов И, два одновибратора, три элемента задержки, первый блок элементов ИЛИ, блок анализа списка перекрытий. 1 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к области цифровой вычислительной техники и предназначено для моделирования комбинаторных задач при проектировании вычислительных систем (ВС), например для размещения процессов (задач, файлов, данных, управляющих процессов и т.д.).

Известен элемент однородной среды, включающий блок обработки входных сигналов, блок запоминания признака конечной точки, блок выходной логики, триггер записи трасс, блок оценки текущего размещения, блок передачи информации, входы, выходы, управляющий вход, информационные входы, информационные выходы, индикаторный выход (а.с. 1291957 СССР, кл. G06F 7/00, опубл. 23.02.87, БИ №7).

Недостатком указанного элемента является узкая область применения, обусловленная ограниченным числом критериев оценки степени оптимальности размещения.

Наиболее близким к предлагаемому устройству по технической сущности является устройство для формирования субоптимального размещения и его оценки, содержащее блок формирования перестановок, блок постоянной памяти, коммутатор, арифметико-логическое устройство (АЛУ), блок запоминания лучшего варианта, введены дешифратор выбора дуги, реверсивный счетчик ячеек, блок оперативной памяти, счетчик топологии, первый и второй счетчики расстояний, умножитель, сумматор, регистр минимальной длины связей, первый элемент сравнения, вычитатель, триггер начала счета, триггер режима, триггер задания топологии, регистр длины связей, второй элемент сравнения, счетчик дуг, дешифратор блокировки дуги, регистр номера дуги, регистр минимального веса, группа элементов И, первый и второй элементы И, второй блок элементов ИЛИ, третий элемент И, первый и второй одновибраторы, первый, второй и третий элементы задержки, два регистра сдвига, элемент ИЛИ и группу элементов ИЛИ, электронную модель графа (ЭМГ), содержащую m электронных моделей дуги, причем l-я электронная модель дуги (l=1, 2,…, m) содержит триггер блокировки дуги, регистр веса дуги, регистр блокировки дуги, первый элемент И, второй элемент И, элемент ИЛИ (Патент РФ №2193796, кл. G06F 17/10, 7/38, опубл. 27.11.2002, БИ №33).

Недостатком указанного устройства является узкая область применения, обусловленная отсутствием средств анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах (МС) по критерию минимизации интенсивности взаимодействия процессов и данных.

Технической задачей изобретения является расширение области применения устройства за счет введения средств анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах по критерию минимизации интенсивности взаимодействия процессов и данных.

Техническая задача решается тем, что в устройство анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах, содержащее первый регистр сдвига, второй регистр сдвига, блок формирования перестановок (БФП), блок постоянной памяти, блок запоминания лучшего варианта (БЗЛВ), коммутатор, АЛУ, дешифратор выбора дуги, реверсивный счетчик ячеек, блок оперативной памяти, счетчик топологии, первый и второй счетчики расстояний, умножитель, сумматор, регистр минимальной длины связей, первый элемент сравнения, вычитатель, триггер начала счета, триггер режима, триггер задания топологии, регистр длины связей, второй элемент сравнения, счетчик дуг, дешифратор блокировки дуги, регистр номера дуги, регистр минимального веса, электронную модель графа, группу с 1-го по n-й элементов ИЛИ, группу с 1-го по m-й элементов И, первый и второй элементы И, второй блок элементов ИЛИ, третий элемент И, первый и второй одновибраторы, первый, второй и третий элементы задержки, первый блок элементов ИЛИ, причем выходы БФП соединены с соответствующими входами блока постоянной памяти и соответствующими входами БЗЛВ, сигнализирующий выход БФП соединен с установочным входом триггера начала счета, выходы блока постоянной памяти соединены с соответствующими входами коммутатора, выход которого соединен с входом АЛУ, выход которого соединен с информационным входом БЗЛВ, а выход БЗЛВ соединен с первым информационным входом АЛУ, выход переполнения регистра сдвига соединен с входом регистра сдвига, выходы первого и второго регистров сдвига с первого по n-й подключены к первым и вторым входам элементов ИЛИ 1-го по n-й соответственно, выход переполнения регистра сдвига соединен с управляющим входом АЛУ и с управляющим входом БФП, тактовый вход устройства соединен с входом регистра сдвига, с тактовым входом БФП и с первыми входами первого и второго элементов И, выход счетчика дуг соединен с входом дешифратора выбора дуги и входом данных регистра номера дуги, выход блока элементов ИЛИ подключен к первому входу элемента сравнения и к входу данных регистра минимального веса, выход регистра минимального веса соединен с вторым входом элемента сравнения и с входом данных блока оперативной памяти, выход элемента задержки соединен с входом установки регистра минимального веса и с входом установки регистра номера дуги, выход третьего элемента И соединен с синхровходом регистра минимального веса и с синхровходом регистра номера дуги, выход регистра номера дуги соединен с информационным входом дешифратора блокировки дуги, выход переполнения счетчика дуг соединен с разрешающим входом дешифратора блокировки дуги, а также с входом элемента задержки, первым счетным входом реверсивного счетчика ячеек и входом записи блока оперативной памяти, выход первого элемента И соединен со счетным входом счетчика дуг и со входом элемента задержки, выход которого соединен со вторым входом третьего элемента И, первый вход которого соединен с выходом элемента сравнения, второй вход первого элемента И соединен с прямым выходом триггера начала счета, который также соединен со вторым входом второго элемента И, третий вход первого элемента И соединен с инверсным выходом триггера режима, прямой выход которого соединен с третьим входом второго элемента И, выход второго элемента И соединен со вторым счетным входом реверсивного счетчика ячеек, выход которого подключен к адресному входу блока оперативной памяти, выход которого подключен к первому входу умножителя, выход счетчика расстояний подключен к второму входу умножителя, выход которого подключен к первому входу сумматора, второй вход которого подключен к выходу регистра минимальной длины связей и к второму входу вычитателя, выход сумматора подключен к входу данных регистра минимальной длины связей, выход элемента задержки подключен к синхровходу регистра минимальной длины связей, выход второго элемента И и счетный вход счетчика расстояний подключены к входу третьего элемента задержки, выход второго одновибратора подключен к синхровходу счетчика расстояний, выход переполнения которого подключен к счетным входам счетчика топологии, счетчика расстояний и к входу второго одновибратора, выход счетчика топологии подключен к входу счетчика расстояний, вход данных устройства подключен ко входу данных счетчика топологии, синхровход счетчика топологии подключен к входу установки устройства, прямой выход триггера задания топологии подключен к разрешающему входу счетчика топологии, установочный вход триггера задания топологии подключен к входу установки устройства, вход сброса триггера задания топологии подключен к входу установки устройства, выход переполнения реверсивного счетчика ячеек подключен к установочному входу триггера режима, вход сброса которого подключен к входу установки устройства, выход регистра длины связей подключен ко второму входу элемента сравнения и к первому входу вычитателя, первый вход элемента сравнения подключен к выходу АЛУ и входу данных регистра длины связей, выход одновибратора подключен к синхровходу регистра длины связей, вход сброса триггера начала счета подключен к входу установки устройства, l-й выход дешифратора выбора дуги (l=1, 2,…, m) соединен с l-м входом выбора дуги электронной модели графа, l-й выход дешифратора блокировки дуги соединен с l-м входом блокировки дуги электронной модели графа, l-й выход веса дуги электронной модели графа соединен с l-м входом блока элементов ИЛИ и l-м входом блока элементов ИЛИ, l-й выход элемента И группы элементов И с l-го по m-й соединен с l-м управляющим входом электронной модели графа, выход блока элементов ИЛИ соединен со вторым информационным входом АЛУ, выход элемента сравнения соединен с входом первого одновибратора, выходы элементов с 1-го по n-й ИЛИ подключены к соответствующим входам элементов И 1-го по m-й, выход вычитателя соединен с выходом длины связей устройства, дополнительно введен блок анализа списка перекрытий, содержащий ОЗУ базы данных, ОЗУ коммуникационных задержек, счетчик адреса строки, счетчик адреса столбца, счетчик элементов строки базы данных, первый элемент сравнения, второй элемент сравнения, третий элемент сравнения, четвертый элемент сравнения, первый и второй регистры идентификатора кратчайшего канала, первый и второй регистры адреса коммуникационной задержки, регистр суммарной задержки, регистр минимальной суммарной задержки, регистр максимального значения, второй сумматор, триггер записи адреса, триггер запрета, четвертый элемент задержки, пятый элемент задержки, шестой элемент задержки, седьмой элемент задержки, восьмой элемент задержки, первый многовходовой элемент И с инверсными входами, второй многовходовой элемент И с инверсными входами, первый трехвходовой элемент И с инверсными входами, многовходовой элемент И, второй трехвходовой элемент И, двухвходовой элемент И, двухвходовой элемент ИЛИ, двухвходовой элемент ИЛИ с инверсными входами, первый инвертор, второй инвертор, причем тактовый вход устройства подключен к счетному входу счетчика элементов строки базы данных, к счетному входу счетчика адреса столбца и к входу синхронизации триггера записи адреса, вход сброса R счетчика элементов строки базы данных подсоединен к третьему входу первого трехвходового элемента И с инверсными входами, к выходу многовходового элемента И, к первому входу двухвходового элемента ИЛИ, к первому входу двухвходового элемента И и ко входу пятого элемента задержки, выход счетчика адреса столбца подсоединен ко второму адресному входу А2 ОЗУ базы данных, первый вход которого соединен с выходом счетчика адреса строки, счетный вход которого подключен к выходу переполнения счетчика адреса столбца, первый выход счетчика элементов строки базы данных подключен ко входу первого инвертора и к первому входу второго многовходового элемента И с инверсными входами, второй выход счетчика элементов строки базы данных соединен со вторым входом первого многовходового элемента И с инверсными входами и с входом второго инвертора, выход первого инвертора соединен с первым входом первого многовходового элемента И с инверсными входами, входы с третьего по n-й которого соединены с входами с третьего по n-й второго многовходового элемента И с инверсными входами, а также подключены к соответствующим выходам счетчика элементов строки базы данных, выход второго инвертора соединен со вторым входом второго многовходового элемента И с инверсными входами, выход первого многовходового элемента И с инверсными входами подключен ко входу седьмого элемента задержки, второму входу первого трехвходового элемента И с инверсными входами, а также к разрешающему е входу первого элемента сравнения, выход второго многовходового элемента И с инверсными входами соединен со входом восьмого элемента задержки, с первым входом первого трехвходового элемента И с инверсными входами, а также с разрешающим е входом второго элемента сравнения, первый вход которого подключен к выходу второго регистра идентификатора кратчайшего канала, разрешающий w вход которого подключен к выходу восьмого элемента задержки, вход записи второго регистра идентификатора кратчайшего канала подключен к выходу ОЗУ базы данных, ко входу многовходового элемента И, ко входу записи первого регистра идентификатора кратчайшего канала, ко второму входу первого элемента сравнения, ко второму входу второго элемента сравнения, а также ко входу записи первого и второго регистра адреса коммуникационной задержки, выход седьмого элемента задержки подсоединен ко входу w разрешения записи первого регистра идентификатора кратчайшего канала, выход которого соединен с первым входом первого элемента сравнения, выход которого подключен к первому входу двухвходового элемента ИЛИ с инверсными входами, второй вход которого соединен с выходом второго элемента сравнения, выход двухвходового элемента ИЛИ с инверсными входами подсоединен ко второму входу второго трехвходового элемента И и ко входу четвертого элемента задержки, первый вход второго трехвходового элемента И подсоединен ко второму входу двухвходового элемента ИЛИ и к прямому выходу триггера запрета, вход записи которого подключен к выходу двухвходового элемента ИЛИ, выход второго трехвходового элемента И соединен с входом w разрешения записи регистра максимального значения, вход записи которого подключен к первому входу четвертого элемента сравнения, к выходу регистра минимальной суммарной задержки и ко второму входу третьего элемента сравнения, первый вход которого соединен с входом записи регистра минимальной суммарной задержки, с выходом регистра суммарной задержки и со вторым входом второго сумматора, первый вход которого подключен к выходу ОЗУ коммуникационных задержек, первый адресный A1 вход которого соединен с выходом первого регистра адреса коммуникационной задержки, второй адресный А2 вход ОЗУ коммуникационных задержек соединен с выходом второго регистра адреса коммуникационной задержки, вход разрешения выдачи ое ОЗУ коммуникационных задержек подключен к выходу шестого элемента задержки, вход которого подключен ко входу w разрешения записи второго регистра адреса коммуникационной задержки, к инверсному выходу триггера записи адреса и ко входу записи триггера записи адреса, разрешающий вход которого соединен с выходом первого трехвходового элемента И с инверсными входами, прямой выход триггера записи адреса подключен к входу w разрешения записи первого регистра адреса коммуникационной задержки, выход второго сумматора подключен к входу записи регистра суммарной задержки, вход сброса R которого подсоединен к выходу пятого элемента задержки, выход третьего элемента сравнения подключен ко второму входу двухвходового элемента И, выход которого соединен с входом w разрешения записи регистра минимальной суммарной задержки, вход сброса R которого подключен к выходу четвертого элемента задержки, третий вход второго трехвходового элемента И подсоединен к выходу четвертого элемента сравнения, второй вход которого соединен с выходом регистра максимального значения и с выходом показателя.

Электронная модель графа содержит m электронных моделей дуги, причем l-я электронная модель дуги (l=1, 2,…, m) содержит триггер блокировки дуги, регистр веса дуги, регистр блокировки дуги, первый элемент И, второй элемент И, элемент ИЛИ, причем входы первого элемента И соединены с соответствующими входами задания графа устройства, выход первого элемента И соединен с синхровходом регистра веса дуги и с установочным входом триггера блокировки дуги, вход сброса которого соединен с l-м входом блокировки дуги электронной модели графа, вход данных регистра веса дуги соединен с l-м входом веса дуги устройства, первый вход элемента ИЛИ соединен с l-м управляющим входом электронной модели графа, а второй вход элемента ИЛИ соединен с выходом второго элемента И, первый вход которого соединен с прямым выходом триггера блокировки дуги и с разрешающим входом регистра блокировки дуги, второй вход второго элемента И соединен с l-м входом выбора дуги электронной модели графа, вход сброса регистра блокировки дуги соединен с l-м входом сброса устройства, выход регистра блокировки дуги соединен с l-м выходом веса дуги электронной модели графа, который также соединен с выходом регистра веса дуги, выход элемента ИЛИ подключен к разрешающему входу регистра веса дуги.

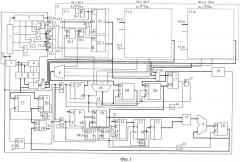

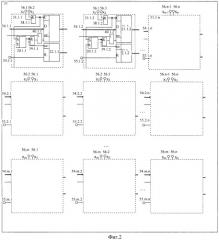

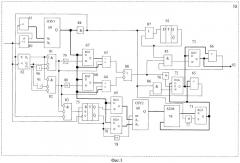

Сущность изобретения поясняется чертежами, где на фиг.1 изображена функциональная схема устройства анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах; фиг.2 поясняет сущность использования электронной модели графа; фиг.3 иллюстрирует принцип работы блока 58 анализа списка перекрытий; фиг.4. поясняет принцип работы предлагаемого устройства.

Общие особенности изобретения состоят в следующем.

Предлагаемое устройство аналогично прототипу используется при моделировании комбинаторных задач проектирования РЭА. Устройство позволяет размещать невзвешенные графы в линейную топологическую модель (размещение в линейку). Дополнительно устройство может применяться для анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах.

Общие особенности изобретения состоят в следующем.

Предлагаемое устройство аналогично прототипу используется при моделировании комбинаторных задач проектирования РЭА. Устройство позволяет выполнять анализ перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах. Подмножество взаимодействующих подпрограмм описывается графом воздействия задач G=<X,E>, где - множество вершин графа G, вершины xi∈X которого соответствуют задачам, а взвешенные дуги eij∈Е описывают связи между задачами и задают объемы данных mij (в байтах), передаваемых при обмене между задачами.

Граф G представляется матрицей обмена информацией (МОИ): , где mij - вес дуги eij.

Мультиконтроллер представляется топологической моделью в виде графа H=<P,V>, где - множество идентификаторов процессорных модулей, организованных в матрицу |P|n×n, где мощность |P|=N=n2 - число процессоров; V - множество межпроцессорных связей, задаваемых матрицей смежности размером n2×n2.

Размещение пакета программ (комплекса задач), описываемых графом G, может быть аналитически описано отображением

где

Здесь s - это номер очередной перестановки, соответствующий s-му варианту размещения. Мощность множества ψ={βS} всевозможных отображений равна числу всевозможных перестановок задач {xqk} в матрице X:|ψ|=N!. Введем матрицу МОИ , описывающую матрицу G, где N=n2=|X|, и матрицу минимальных расстояний (ММР) , N=n2=|Н|.

ММР строится по матрице смежности графа Н. Если непосредственной связи между модулями в базовом блоке нет, то элемент ММР: dij - минимальное межмодульное топологическое расстояние, которое вычисляется как кратчайший путь от вершины pi до вершины pj в графе Н, измеренный числом последовательно соединенных каналов.

Задача размещения параллельных подпрограмм решается посредством целенаправленной перестановки строк и столбцов в матрице обмена информацией. При этом критерием оптимальности искомого варианта размещения является величина максимальной задержки в линиях связи между процессорами мультиконтроллера. Таким образом, задача размещения сформулирована как поиск отображения β*∈Ψ, такого, что

,

где - коммутационная задержка при передаче данных между модулями pa,b и px,y, соответствующая отображению βs, которая пропорциональна произведению dij·mij, где i=(а-1)·n+b, j=(x-1)·n+y.

Данная формула описывает минимаксный критерий поиска наилучшего варианта размещения, который не позволяет правильно оценить качество размещения, так как он не учитывает возможные перекрытия каналов передачи данных. Поэтому необходимо модифицировать критерий для учета перекрытий.

Для решения данной задачи программно создается база данных избыточных кратчайших путей по матрице смежности физической топологии мультиконтроллера. Избыточным кратчайшим путем называется любой из вариантов кратчайших маршрутов передачи данных, который представляется последовательностью номеров процессоров в этом маршруте. Кратчайший канал передачи данных, которому соответствует конкретный избыточный путь, идентифицируется номерами начального и конечного процессора. Для каждого избыточного пути в базе данных помимо идентификатора кратчайшего канала, которому принадлежит избыточный путь, хранится список перекрытий данного пути. Список перекрытий представляет собой список идентификаторов кратчайших каналов, которые можно выделить целиком в данном избыточном пути, включая тот кратчайший канал, которому соответствует данный избыточный путь.

На фиг.4а изображена матричная система из 9 процессоров. Рассмотрим кратчайшие маршруты от процессора 1 до всех остальных процессоров системы. В соответствии с описанным выше форматом фрагмент базы данных избыточных кратчайших путей для данной системы выглядит следующим образом:

| ID кратчайше-го канала | Избыточные пути | Списки перекрытий |

| 1-2 | 1-2 | 1-2 |

| 1-4 | 1-4 | 1-4 |

| 1-3 | 1-2-3 | 1-2, 2-3, 1-3 |

| 1-5 | 1-2-5 | 1-2, 2-5, 1-5 |

| 1-5 | 1-4-5 | 1-4, 4-5, 1-5 |

| 1-7 | 1-4-7 | 1-4, 4-7, 1-7 |

| 1-6 | 1-2-3-6 | 1-2, 2-3, 3-6, 1-3, 2-6, 1-6 |

| 1-6 | 1-2-5-6 | 1-2, 2-5, 5-6, 1-5, 2-6, 1-6 |

| 1-6 | 1-4-5-6 | 1-4, 4-5, 5-6, 1-5, 4-6, 1-6 |

| 1-8 | 1-2-5-8 | 1-2, 2-5, 5-8, 1-5, 2-8, 1-8 |

| 1-8 | 1-4-5-8 | 1-4, 4-5, 5-8, 1-5, 4-8, 1-8 |

| 1-8 | 1-4-7-8 | 1-4, 4-7, 7-8, 1-7, 4-8, 1-8 |

| 1-9 | 1-2-3-6-9 | 1-2, 2-3, 3-6, 6-9, 1-3, 2-6, 3-9, 1-6, 2-9, 1-9 |

| 1-9 | 1-2-5-6-9 | 1-2, 2-5, 5-6, 6-9, 1-5, 2-6, 5-9, 1-6, 2-9, 1-9 |

| 1-9 | 1-4-5-6-9 | 1-4, 4-5, 5-6, 6-9, 1-5, 4-6, 5-9, 1-6, 4-9, 1-9 |

| 1-9 | 1-2-5-8-9 | 1-2, 2-5, 5-8, 8-9, 1-5, 2-8, 5-9, 1-8, 2-9, 1-9 |

| 1-9 | 1-4-5-8-9 | 1-4, 4-5, 5-8, 8-9, 1-5, 4-8, 5-9, 1-8, 4-9, 1-9 |

| 1-9 | 1-4-7-8-9 | 1-4, 4-7, 7-8, 8-9, 1-7, 4-8, 7-9, 1-8, 4-9, 1-9 |

На фиг.46 изображен пример графа исходного алгоритма. Вершины графа являются подпрограммами, а дуги - связями между подпрограммами, веса дуг задают объемы передаваемых данных между подпрограммами. Предположим, что начальное размещение подпрограмм произведено в соответствии номеров подпрограмм номерам процессоров мультиконтроллера, как показано на фиг.4в. Определим примерный объем передаваемых данных между процессорами исходя из условия, что маршрутизация будет выполняться по критерию наименьшей загрузки каналов передачи данных.

Для этого вначале расставим веса дуг графа исходного алгоритма, которые связывают подпрограммы, расположенные в соседних процессорах (фиг.4в). Таким образом, на канал 1-2 накладывается 20 байт, на канал 2-3 - 15 байт, на канал 2-5 - 20 байт, на канал 1-4 - 30 байт, на канал 4-5 - 30 байт, на канал 5-6 - 20 байт, на канал 3-6 - 20 байт, на канал 4-7 - 20 байт, на канал 5-8 - 20 байт, на канал 7-8 - 30 байт, на канал 8-9 - 15 байт и на канал 6-9 - 15 байт.

Далее проложим дуги, для которых имеется только 1 кратчайший путь: x1-x7 и x2-х8 (фиг.4г). При прокладке дуги x1-x7 по пути 1-4-7 на канале 1-4 становится 30+40=70 байт передаваемых данных, на канале 4-7, соответственно, 20+40=60 байт. Аналогично при прокладке дуги x2-x8 по пути 2-5-8 на каналах 2-5 и 5-8 становится 20+30=50 байт.

Дуга x1-x5 имеет 2 варианта кратчайшего маршрута: 1-2-5 и 1-4-5. Сумма уже наложенных объемов данных на каналы единичной длины, составляющие путь 1-2-5, равна 70 байт. На пути 1-4-5 данная сумма равна 100 байт. Таким образом, путь 1-2-5 является менее загруженным, поэтому проложим дугу x1-x5 по пути 1-2-5 (фиг.4д). Соответственно, на канал 1-2 накладывается 20+40=60 байт, на канал 2-5 накладывается 50+40=90 байт.

Аналогично выберем путь для прокладки дуги x4-x8. Сумма объемов данных на пути 4-5-8 равна 80 байт, на пути 4-7-8 - 90 байт. Поэтому дуга прокладывается по пути 4-5-8 как наименее загруженному маршруту. Тогда на канале 4-5 становится 30+30=60 байт, на канале 5-8, соответственно, 50+30=80 байт.

Для дуги x1-x8 существует 3 варианта кратчайшего пути: 1-2-5-8, 1-4-5-8 и 1-4-7-8. Рассчитаем суммарные объемы передаваемых данных на этих маршрутах:

1-2-5-8: 60+90+80=230 байт

1-4-5-8: 70+60+80=210 байт

1-4-7-8: 70+60+30=160 байт

Наименее загруженным является путь 1-4-7-8, поэтому проложим дугу x1-x8 по этому пути (фиг.4е). Тогда на канале 1-4 становится 100 байт, на канале 4-7 - 90 байт, на канале 7-8 - 60 байт.

Таким образом, реальный объем передаваемых данных по каналу 1-4, который, в соответствии с графом исходного алгоритма, равен 30 байт, после маршрутизации может стать 100 байт, поэтому минимаксный критерий не позволяет правильно оценить качество размещения задач.

Предлагаемый минимаксиминный критерий, учитывающий перекрытия каналов, выглядит следующим образом:

где S - номер очередной перестановки задач в МОИ в процессе поиска;

φ={βS} - множество всевозможных отображений вершин графа задач на множество идентификаторов процессоров;

βS - отображение, соответствующее S-й перестановке задач в МОИ;

k - номер кратчайшего пути (канала) между процессорами Pab и Pxy;

t - номер избыточного пути длиной, равной кратчайшему каналу между процессорами Pab и Pxy;

Zt - номер кратчайшего пути в любой паре процессоров длиной d(Zt)≤d(k), меньшей или равной k-му кратчайшему пути между процессорами Pab и Pxy, перекрывающегося с k-м каналом;

nkt - число кратчайших путей с длинами d(Zt)≤d(k), в том числе и основной k-й путь, перекрывающихся с kt-м избыточным путем длины d(k);

Tβs (Zt)(Pab,Pxy)=dij (Zt)·mij·c≠o при mij≠0 - задержка при передаче данных в паре процессоров по Zt-му кратчайшему пути в βS-м варианте отображения после S-й перестановки задач в МОИ, в том числе и задержка в k-м кратчайшем пути по матрице ММР при Zt=k:TβS (k)(Pab,Pxy)=dij (k)·mij·c;

- суммарная задержка на t-ом избыточном пути, равном по длине k-ому кратчайшему каналу d(t)=d(k), с учетом перекрытия t-го пути другими Zt-ми путями длины d(Zt)≤d(k). Если перекрытий нет, то суммарная задержка на любом t-ом избыточном пути k-го канала равна задержке на k-ом кратчайшем пути: TβS (k)(Pab,Pxy)=dij (k)·mij·c.

Величина минимаксиминного критерия вычисляется следующим образом:

1. По матрицам МОИ и ММР вычисляются задержки на всех k-x кратчайших неизбыточных каналах без учета перекрытий:

{TβS (k)(Pab,Pxy)}={mij·dij (k)}, , где при c=const величина с опускается.

2. Используется база данных избыточных путей для всех k-x кратчайших каналов, предварительно создаваемая по матрице смежности физической топологии мультиконтроллера. Для каждого kt-го избыточного пути вычисляется суммарная задержка:

где (mijdij}Zt - задержка, вносимая одним Zt-каналом, перекрывающимся с данным избыточным kt-м каналом, выбираемая из множества рассчитанных на первом шаге задержек. Количество слагаемых nkt определяется длиной списка перекрытий kt-го избыточного пути.

3. По каждому k-му каналу, т.е. одному элементу ММР вычисляется

4. Из всех {Tkmin} находится максимум, который и будет достоверной величиной коммуникационной задержки, не увеличивающейся после дальнейшей маршрутизации по критерию использования наименее занятых линий связи между процессорами:

Найденный в данном шаге поиска максимум сравнивается с предыдущим максимумом, найденным в предыдущем шаге поиска, и принимается решение об успешности или неудаче на S-м шаге перестановок.

Устройство анализа перекрытий каналов при размещении параллельных подпрограмм в многопроцессорных системах (фиг.1) содержит первый регистр 1 сдвига, второй регистр 2 сдвига, блок 3 формирования перестановок (БФП), блок 4 постоянной памяти, блок 5 запоминания лучшего варианта (БЗЛВ), коммутатор 6, АЛУ 7, дешифратор 8 выбора дуги, реверсивный счетчик 9 ячеек, блок 10 оперативной памяти, счетчик 11 топологии, первый 12 и второй 13 счетчики расстояний, умножитель 14, сумматор 15, регистр 16 минимальной длины связей, первый элемент 17 сравнения, вычитатель 18, триггер 19 начала счета, триггер 23 режима, триггер 24 задания топологии, регистр 25 длины связей, второй элемент 26 сравнения, счетчик 27 дуг, дешифратор 28 блокировки дуги, регистр 29 номера дуги, регистр 30 минимального веса, электронную модель 31 графа, группу элементов ИЛИ 32.1-32.n, группу элементов И 33.1-33.m, первый 34 и второй 35 элементы И, второй блок элементов ИЛИ 36, третий элемент И 37, первый 41 и второй 42 одновибраторы, первый 43, второй 44 и третий 45 элементы задержки, первый блок элементов ИЛИ 46, причем выходы БФП 3 соединены с соответствующими входами блока 4 постоянной памяти и соответствующими входами БЗЛВ 5, сигнализирующий выход БФП 3 соединен с установочным входом триггера 19 начала счета, выходы блока 4 постоянной памяти соединены с соответствующими входами коммутатора 6, выход которого соединен с входом АЛУ 7, выход которого соединен с информационным входом БЗЛВ 5, а выход БЗЛВ 5 соединен с первым информационным входом АЛУ 7, выход переполнения регистра 1 сдвига соединен с входом регистра 2 сдвига, выходы регистров 1 и 2 с первого по n-й подключены к первым и вторым входам элементов ИЛИ 32.1-32.n соответственно, выход переполнения регистра 2 сдвига соединен с управляющим входом АЛУ 7 и с управляющим входом БФП 3, тактовый вход 57 устройства соединен с входом регистра 1 сдвига, с тактовым входом БФП 3 и с первыми входами элементов И 34 и 35, выход счетчика 27 дуг соединен с входом дешифратора 8 выбора дуги и входом данных регистра 29 номера дуги, выход блока элементов ИЛИ 36 подключен к первому входу элемента 17 сравнения и к входу данных регистра 30 минимального веса, выход регистра 30 минимального веса соединен с вторым входом элемента 17 сравнения и с входом данных блока 10 оперативной памяти, выход элемента 43 задержки соединен с входом установки регистра 30 минимального веса и с входом установки регистра 29 номера дуги, выход третьего элемента И 37 соединен с синхровходом регистра 30 минимального веса и с синхровходом регистра 29 номера дуги, выход регистра 29 номера дуги соединен с информационным входом дешифратора 28 блокировки дуги, выход переполнения счетчика 27 дуг соединен с разрешающим входом дешифратора 28 блокировки дуги, а также с входом элемента 43 задержки, первым счетным входом реверсивного счетчика 9 ячеек и входом записи блока 10 оперативной памяти, выход элемента И 34 соединен со счетным входом счетчика 27 дуг и со входом элемента 44 задержки, выход которого соединен со вторым входом элемента И 37, первый вход которого соединен с выходом элемента 17 сравнения, второй вход элемента И 34 соединен с прямым выходом триггера 19 начала счета, который также соединен со вторым входом элемента И 35, третий вход элемента И 34 соединен с инверсным выходом триггера 23 режима, прямой выход которого соединен с третьим входом элемента И 35, выход элемента И 35 соединен со вторым счетным входом реверсивного счетчика 9 ячеек, выход которого подключен к адресному входу блока 10 оперативной памяти, выход которого подключен к первому входу умножителя 14, выход счетчика 13 расстояний подключен к второму входу умножителя 14, выход которого подключен к первому входу сумматора 15, второй вход которого подключен к выходу регистра 16 минимальной длины связей и к второму входу вычитателя 18, выход сумматора 15 подключен к входу данных регистра 16 минимальной длины связей, выход элемента 45 задержки подключен к синхровходу регистра 16 минимальной длины связей, выход элемента И 35 и счетный вход счетчика 12 расстояний подключены к входу элемента 45 задержки, выход одновибратора 42 подключен к синхровходу счетчика 12 расстояний, выход переполнения которого подключен к счетным входам счетчика 11 топологии, счетчика 13 расстояний и к входу одновибратора 42, выход счетчика 11 топологии подключен к входу счетчика 12 расстояний, вход 51 данных устройства подключен ко входу данных счетчика 11 топологии, синхровход счетчика 11 топологии подключен к входу 52 установки устройства, прямой выход триггера 24 задания топологии подключен к разрешающему входу счетчика 11 топологии, установочный вход триггера 24 задания топологии подключен к входу 49 установки устройства, вход сброса триггера 24 задания топологии подключен к входу 50 установки устройства, выход переполнения реверсивного счетчика 9 ячеек подключен к установочному входу триггера 23 режима, вход сброса которого подключен к входу 48 установки устройства, выход регистра 25 длины связей подключен ко второму входу элемента 26 сравнения и к первому входу вычитателя 18, первый вход элемента 26 сравнения подключен к выходу АЛУ 7 и входу данных регистра 25 длины связей, выход одновибратора 41 подключен к синхровходу регистра 25 длины связей, вход сброса триггера 19 начала счета подключен к входу 47 установки устройства, l-й выход дешифратора 8 выбора дуги (l=1, 2,…, m) соединен с l-м входом выбора дуги электронной модели 31 графа, l-й выход дешифратора 28 блокировки дуги соединен с l-м входом блокировки дуги электронной модели 31 графа, l-й выход веса дуги электронной модели 31 графа соединен с l-м входом блока элементов ИЛИ 36 и l-м входом блока элементов ИЛИ 46, выход элемента И 33.l соединен с l-м управляющим входом электронной модели 31 графа, выход блока элементов ИЛИ 46 соединен со вторым информационным входом АЛУ 7, выход элемента 26 сравнения соединен с входом одновибратора 41, выходы элементов ИЛИ 32.1-32.n подключены к соответствующим входам элементов И 33.1-33.m, выход вычитателя 18 соединен с выходом 53 длины связей устройства, а также дополнительно введенный блок 58 анализа списка перекрытий, содержащий ОЗУ 59 базы данных, ОЗУ 60 коммуникационных задержек, счетчик 61 адреса строки, счетчик 89 адреса столбца, счетчик 62 элементов строки базы данных, первый 63 элемент сравнения, второй 64 элемент сравнения, третий 65 элемент сравнения, четвертый 66 элемент сравнения, первый 67 и второй 68 регистры идентификатора кратчайшего канала, первый 69 и второй 70 регистры адреса коммуникационной задержки, регистр 71 суммарной задержки, регистр 72 минимальной суммарной задержки, регистр 73 максимального значения, второй 74 сумматор, триггер 75 записи адреса, триггер 76 запрета, четвертый 76 элемент задержки, пятый 77 элемент задержки, шестой 78 элемент задержки, седьмой 79 элемент задержки, восьмой 80 элемент задержки, первый 81 многовходовой элемент И с инверсными входами, второй 82 многовходовой элемент И с инверсными входами, первый 83 трехвходовой элемент И с инверсными входами, многовходовой 84 элемент И, второй 85 трехвходовой элемент И, двухвходовой 86 элемент И, двухвходовой 87 элемент ИЛИ, двухвходовой 88 элемент ИЛИ с инверсными входами, первый 90 инвертор, второй 91 инвертор, причем тактовый 57 вход устройства подключен к счетному 62 входу счетчика элементов строки базы данных, к счетному входу счетчика 89 адреса столбца и к входу синхронизации триггера 75 записи адреса, вход сброса R счетчика 62 элементов строки базы данных подсоединен к третьему входу первого 83 трехвходового элемента И с инверсными входами, к выходу многовходового 84 элемента И, к первому входу двухвходового 87 элемента ИЛИ, к первому входу двухвходового 86 элемента И и ко входу пятого 77 элемента задержки, выход счетчика 89 адреса столбца подсоединен ко второму адресному входу А2 ОЗУ 59 базы данных, первый вход которого соедине