Устройство измерения задержки сигналов точного времени в каналах связи

Иллюстрации

Показать всеИзобретение относится к технике измерения сигналов точного времени в каналах связи и может использоваться в сетях электросвязи, системах передачи. Достигаемый технический результат - повышение точности измерений в условиях фазовых помех в каналах связи. Устройство измерения задержки сигналов точного времени в каналах связи содержит три делителя с переменным коэффициентом деления, блок управления режимами, два релейно-фазовых детектора, вычислитель, счетчик тактовых импульсов, при этом вычислитель содержит фиксатор, два счетчика, три сумматора, формирователь данных измерения, триггер-коммутатор. 4 ил.

Реферат

Изобретение относиться к технике измерения сигналов единого точного времени (ЕТВ), при их распределении в сетях электросвязи, построенных на базе систем передачи синхронной и плезиохронной цифровой иерархии в условиях фазовых помех, с целью установки ЕТВ на различных объектах цифровой сети путем определения задержки этих сигналов в системах передачи.

Наиболее близким техническим решением, принятым за прототип, является «Устройство определения временной задержки» (патент на изобретение №2240648, опубликованный в бюл. №32 от 20.11.2004).

Известное устройство содержит первый второй и третий делители частоты с переменным коэффициентом деления, управляющие входы которых соединены с первыми выходами блока управления режимами, блок установки фазы делителя, на вход которого подключены два сигнала фазирования, выходы которого соединены соответственно с входами первого и третьего делителей частоты с переменным коэффициентом деления, выходы которых соединены с первыми входами соответственно первого и второго релейно-фазововых детекторов, выходы которых соединены с входами блока управления режимами, а выходы второго делителя частоты с переменным коэффициентом деления - со вторыми входами соответственно первого и второго релейно-фазововых детекторов, причем дополнительный сигнал подключен к входу второго делителя частоты с переменным коэффициентом деления, измеряемый сигнал подключен к входу третьего делителя частоты с переменным коэффициентом деления, а опорный сигнал подключен к входу первого делителя частоты с переменным коэффициентом деления.

Недостатком прототипа устройства является его низкая помехоустойчивость и сравнительно низкая точность измерения, что ограничивает возможность его применения на цифровой сети связи.

Задачей предлагаемого изобретения является повышение точности измерений в условиях фазовых помех в каналах связи, которая достигается применением метода многократного измерения в течении всего периода повторения опорного сигнала точного времени с соответствующей обработкой данных, получаемых в результате этих измерений.

Для достижения технического результата в устройство, содержащее первый, делитель частоты с переменным коэффициентом деления, вход которого соединен с входом опорных импульсов устройства, а управляющий вход с первым выходом блока управления режимами, второй и третий выход которого соединены соответственно с управляющими входами второго и третьего делителя частоты с переменными коэффициентами деления, а первый вход - с выходом первого релейно-фазового детектора, первый вход которого соединен с выходом первого делителя частоты с переменным коэффициентом деления, а второй вход - с выходом второго делителя частоты с переменным коэффициентом деления и со вторым входом второго релейно-фазового детектора, первый вход которого соединен с выходом третьего делителя частоты с переменным коэффициентом деления, а выход - со вторым входом блока управления режимами, при этом на входы второго и третьего делителей частоты с переменным коэффициентами деления подключены соответственно входы импульсов дополнительного и измеряемого сигналов, в отличие от прототипа, введены вычислитель, содержащий сумматор, два счетчика, два дополнительных сумматора, триггер-коммутатор, формирователь данных измерения и фиксатор, а также счетчик тактовых импульсов, первый вход которого соединен с входом опорных тактовых импульсов, второй вход - с входом опорного сигнала времени и с первым входом фиксатора в вычислителе, третий вход - с входом измеряемого сигнала времени, а выходы с входами «n» и «0,5ТИ» вычислителя, у которого управляющие входы соединены с управляющими выходами блока управления режимами, так что второй вход фиксатора вычислителя соединен с управляющим входом «Готов», счетные входы сумматора - с выходами «Сигн. 1» и «Сигн. 2», а счетные входы первого и второго счетчиков и первые управляющие входы дополнительных сумматоров - с выходом «Измер», первый же выход вычислителя с триггера-коммутатора «1» соединен с управляющим входом блока управления режимами, а результирующий выход вычислителя, с формирователя данных измерения, является выходом устройства, при этом выход фиксатора соединен с первым управляющим входом сумматора, выход которого соединен со счетными входами первого и второго дополнительных сумматоров, вторые управляющие входы которых соединены с выходами триггера-коммутатора так, что выход «1» соединен с первым управляющим входом первого дополнительного сумматора и управляющим входом первого счетчика, а выход «0» - с первыми управляющими входами второго дополнительного сумматора и второго счетчика, выходы счетчиков соединены с входами триггера-коммутатора так, что вход счета первого счетчика - с входом установки «0» коммутатора, а выход окончания счета второго счетчика - с входом установки «1» и входом дополнительного суммирования первого дополнительного сумматора, причем оба выхода соединены с входом сброса данных в сумматоре, кроме того третий управляющий вход первого дополнительного сумматора соединен с входом «0,5ТИ» вычислителя, а дополнительный счетный вход с выходом второго дополнительного сумматора, а первый счетный вход формирователя данных измерения соединен с выходом первого дополнительного сумматора, второй счетный вход с входом «n0» вычислителя, управляющий вход с выходом окончания счета первого счетчика и входом сброса фиксатора. Работу устройства поясняют следующие графические материалы:

функциональная схема предлагаемого устройства - фиг.1;

функциональная схема вычислителя - фиг.2;

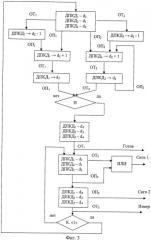

алгоритм работы блока управления режимами - фиг.3;

алгоритм работы вычислителя - фиг 4.

Предлагаемое устройство (см. фиг.1) содержит три делителя с переменным коэффициентом деления (1), (3) и (4), два релейно-фазовых детектора (2) и (5), блок управления режимами (7), счетчик тактовых импульсов (8) и вычислитель (6), причем выходы первого (1) и второго (3) делителя с переменным коэффициентом деления соединены соответственно с первым и вторым входами первого релейно-фазового детектора (2), а выходы третьего (4) и второго (3) делителя с переменным коэффициентом деления соединены соответственно с первым и вторым входами второго релейно-фазового детектора (5), выходы которых (2 и 5) соединены соответственно с первым и вторым входами блока управления режимами (7), а выходы последнего соединены с управляющими входами всех трех делителей с переменным коэффициентом деления (1), (3) и (4), при этом управляющий выход блока управления режимами (7) соединен с первым входом вычислителя (6), управляющие выходы которого соединены с управляющим входами блока управления режимами (7), а результирующий выход - с выходом устройства, а счетные входы вычислителя соединены с выходами счетчика тактовых импульсов (8), в то же время опорные тактовые импульсы (ТИ0) подключены к первым входам первого делителя с переменным коэффициентом деления (1) и счетчика тактовых импульсов (8), тактовые импульсы измеряемого сигнала (ТИИ) - к первым входам третьего делителя с переменным коэффициентом деления (4), а импульсы дополнительного сигнала (ДИ) - к первым входам второго делителя с переменным коэффициентом деления (3), при этом опорный сигнал времени (ОВ) подключен к соответствующему входу вычислителя (6) и второму входу счетчика тактовых импульсов (8), а измеряемый сигнал времени (ИВ) - к третьим входам счетчика тактовых импульсов (8).

Установленный в устройстве вычислитель (6) (см. фиг.2) содержит фиксатор (9), сумматор данных (10), триггер-коммутатор (11), два счетчика (12) и (13), два дополнительных сумматора (15) и (16) и формирователь данных измерения (14), причем вход опорного сигнала времени (ОВ) и управляющий выход «Готов», в составе управляющих выходов блока управления режимами (7), соединены с управляющими входами фиксатора (9), а управляющие выходы блока управления режимами (7): «Сигн. 1» и «Сигн. 2» - со счетными входами сумматора (10), «Измер» - со счетными входами счетчиков (12 и 13) и первыми управляющими входами дополнительных сумматоров (15 и 16), первый же выход вычислителя (6) с коммутатора (11) «1» соединен с управляющим входом блока управления режимами (7), а результирующий выход вычислителя (6) с формирователя данных измерения (14) - с выходом устройства, при этом выход фиксатора (9) соединен с первым управляющим входом сумматора (10), выход которого соединен со счетными входами первого и второго дополнительных сумматоров (15 и 16), вторые же управляющие входы сумматоров (15 и 16) соединены с выходами триггер-коммутатора (11) так, что выход «1» соединен с входом первого дополнительного сумматора (15) и управляющим входом первого счетчика (12), а выход «0» - с входами второго дополнительного сумматора (16) и второго счетчика (13), выходы же счетчиков (12 и 13) соединены с входами триггер-коммутатора (11) так, что вход счета первого счетчика (12) соединен с входом установки «0»(У0) коммутатора (11), а выход окончания счета второго счетчика (13) - с входом установки «1»(У1) и входом дополнительного суммирования первого дополнительного сумматора (15), причем оба выхода соединены с входом сброса данных сумматора (10), кроме того, третий управляющий вход первого дополнительного сумматора (15) соединен с входом «0,5ТИ» вычислителя (6), а дополнительный счетный вход - с выходом второго дополнительного сумматора (16), а первый счетный вход формирователя данных измерения (14) соединен с выходом первого дополнительного сумматора (15), второй счетный вход с входом «n0» вычислителя (6), а управляющий вход - с выходом окончания счета первого счетчика (12) и входом сброса фиксатора (9).

Измерения начинаются в момент поступления сигнала ОВ. При этом счетчик тактовых импульсов (8) начинает считать число ТИ0, которые подаются на его вход, вплоть до момента приема сигнала ИВ. При этом определяется наличие в этом интервале времени дополнительного 0,5 ТИ0. В то же время в соответствии с алгоритмом (см. фиг.3) все делители с переменным коэффициентом деления (ДПКД) непрерывно работают от поступающих тактовых импульсов, т.е. не существует точного момента, соответствующего началу процесса получения данных точного измерения. Начаться такие измерения могут с любого момента. Если сигнал «Готов» поступил раньше, чем сигнал ОВ, то триггер-коммутатор (11) стоит в положении «1» и все ДПКД начнут делить соответственно на d1 и на d2. При таком делении период поделенных сигналов в ДПКД1 (1) и ДПКД3 (4) меньше, чем в ДПКД2 (3) на N измеряемых единиц. При каждом делении в релейно-фазовом детекторе (РФД) (2 и 5) формируется сигнал ОП, когда передний фронт поделенного сигнала с ДПКД1 (1) или ДПКД3 (4) поступил раньше, чем с ДПКД2 (3), или ОТ, если сигнал с ДПКД2 (3) поступил раньше. Для более быстрого фазирования делителей коэффициенты деления, соответственно, в ДПКД1 (1) или ДПКД3 (4) уменьшается на 1, если получен сигнал ОТ, или увеличивается на 1, если получен сигнал ОП. Если при делении на d2+1 появляется сигнал ОТ, то в ДПКД1 (1) и ДПКД3 (4) устанавливается коэффициент деления равным d2 и начинается постепенное сближение передних фронтов поделенных сигналов на N измеряемых единиц при каждом периоде деления. В конце концов, сформируется сигнал ОП. Так как при проведении измерений необходимо, чтобы поделенный сигнал с выхода ДПКД3 (4) был задержан относительно сигнала с выхода ДПКД1 (1), при поступлении сигнала ОП с выхода РФД2 (5) производят однократное увеличение периода поделенных сигналов ДПКД3 (4) на один такт. Этот процесс оканчивается тогда, когда при делении обоих ДПКД на d2, с РФД1 (2) поступил сигнал ОП, а с РФД2 (5) - ОТ. Далее фронт поделенного сигнала с ДПКД1 (1) сближают с фронтом поделенного сигнала от ДПКД2 (3) путем установки таких коэффициентов деления, при которых период поделенного сигнала ДПКД3 (4) меньше на одну измеряемую единицу, чем у ДПКД1 (1). Фазирование ДПКД1 (1) оканчивается при поступлении с РФД1 (2) сигнала ОТ1. При этом формируется сигнал «Готов» и начинается измерение, если до этого на устройство поступил сигнал ОВ. В процессе измерения сигнал с выхода ДПКД3 (4) фазируется с сигналом с выхода ДПКД2, (3) т.е. определяется величина задержки поделенного сигнала ДПКД3 (4) относительно положения, когда этот сигнал был фазирован с ДПКД1 (1).

В процессе измерения начинается расчет временного сдвига в вычислителе (6) в соответствии с алгоритмом фиг.4. Необходимые для проведения расчетов управляющие сигналы («Сигн. 1», «Сигн. 2» и Измер.) формируются в блоке управления режимами (7) в соответствии с алгоритмом фиг.3.

В процессе измерения сначала устанавливают такие коэффициенты деления, при которых период поделенного сигнала с ДПКД3 (4) меньше периода сигнала ДПКД2 (3) на N единиц и на вычислитель (6) в составе сигналов управления поступает «Сигн. 1» при каждом периоде деления. Когда сигнал с ДПКД3 (4) начнет опережать сигнал ДПКД2 (3) формируется в РФД2 (5) сигнал ОП2 и начинается сближение сигналов на входе РФД2 (5) по одной единице при каждом делении. При этом на вход вычислителя поступает «Сигн. 2». Когда фазирование достигнуто, то формируется «Измер» и в зависимости от установленного режима вычислителя («1» или «0» в триггер-коммутаторе) по сигналу управления (1-й Выход) производится повторное вычисление или перед проведением вычислений проводится фазирование по описанному выше алгоритму. До поступления сигнала ОВ 1-й выход вычислителя (6) соответствует положению «1», а сигнал «Готов» не оказывает никакого воздействия на работу вычислителя (6). При этом в соответствии с алгоритмом фиг.3 происходит последовательный переход от режима фазирования к режиму вычисления и обратно к режиму фазирования.

Работу вычислителя поясняет функциональная схема, изображенная на фиг.2 и алгоритм, показанный на фиг 4.

Работа вычислителя начинается при поступлении сигнала «Готов», при условии, что до этого поступил сигнал ОВ, и заканчивается при сигнале заполнении счетчика с выхода первого счетчика (12), по которому результаты измерения поступают на выход устройства. Фиксатор режима измерений (9) определяет период времени, в течение которого сумматор принимает данные, соответствующие «Сигн. 1» и «Сигн. 2» и производит их сложение. Т.к. в триггер-коммутаторе (11) установлен режим «1», то сигнал «Измер» с выхода коммутатора записывает данные сумматора в 1-й дополнительный сумматор (15) и подает импульс на счетчик (12). В 1-м дополнительном сумматоре (15) полученные данные от сумматора n1 суммируются с имеющимися данными (n2=n2+n1). Одновременно добавляется 1 в счетчике (12) (n4). Выходной сигнал этого счетчика (12), при условии, что n4 не равно N2, т.е. счетчик не заполнен, поступает на коммутатор (11), устанавливая режим «0». При этом обнуляются данные сумматора (10) и в 1-м дополнительном сумматоре (15) определяют и устраняют возможную ошибку в положении импульсов ТИИ за счет наличия помех в канале связи, считая при этом, что уровень этих помех в интервале между двумя ОВ не превышает 0,25 периода ТИ, т.е. N3 минимальных интервалов суммирования в сумматоре (10). Сигнал наличия 0,5ТИ с выхода счетчика тактовых импульсов (8) показывает наличие дополнительно 0,5ТИо в измеряемом временном интервале. Если 0,5ТИ=0, то измеряемый сдвиг фаз ТИ не может быть больше 0,75 N3, т.е. если полученный сигнал больше 0,75, то из измеренных данных надо вычесть величину периода ТИ, т.е. величину N3, т.к. за счет помех число ТИ0 в измеряемом интервале меньше, чем замерено счетчиком тактовых импульсов. В результате данные измерения отрицательные, т.е. меньше записанных в 1-й дополнительный сумматор (15) на величину N3. Аналогично, при 0,5ТИ=1 и результатах измерения, меньших 0,25, необходимо увеличить данные 1-го дополнительного сумматора (15) на величину N3. Рассчитанное значение измеряемой задержки, запоминается в 1-м дополнительным сумматоре (15). В дальнейшем повторяется режим измерения, и сумматор (10) набирает новые данные, которые переписываются во 2-й дополнительный сумматор (16) и 2-й счетчик (13), который подсчитывает количество таких измерений. Когда число измерений n5=N1 данные 2-го дополнительного сумматора (16) делятся на число проведенных измерений и подаются в 1-й дополнительный сумматор (15) в качестве корректирующей поправки. После этого в триггер-коммутаторе (11) устанавливается «1». Все процессы повторяются до тех пор, пока 1-й счетчик (12) не отметит, что прошло N2 измерений. При этом обеспечивается перенос всех данных 1-го дополнительного сумматора (15) в формирователь данных измерения (14), в котором уже имеются данные о числе n0, полученных от счетчика тактовых импульсов (8). В формирователе данных измерений (14) производится суммирование полученных донных и приведение их к одному масштабу, который может быть значительно меньше, чем шаг измерения. Этот шаг уменьшается в N4/N2=N5/N3 раз. Полученные таким образом данные измерений поступают на выход устройства.

Таким образом, расчет фактической задержки измеряемого сигнала происходит в вычислителе (6) путем проведения многократных измерений задержки ТИи относительно ТИ0,по описанному выше алгоритму, и суммирование их с данными счетчика тактовых импульсов (8).

Устройство измерения задержки сигналов точного времени в каналах связи относится к технике распределения сигналов единого точного времени по цифровой сети связи и содержит первый делитель частоты с переменным коэффициентом деления, вход которого соединен с входом опорных импульсов устройства, а управляющий вход - с первым выходом блока управления режимами, второй и третий выходы которого соединены соответственно с управляющими входами второго и третьего делителей частоты с переменными коэффициентами деления, а первый вход - с выходом первого релейно-фазового детектора, первый вход которого соединен с выходом первого делителя частоты с переменным коэффициентом деления, а второй вход - с выходом второго делителя частоты с переменным коэффициентом деления и со вторым входом второго релейно-фазового детектора, первый вход которого соединен с выходом третьего делителя частоты с переменным коэффициентом деления, а выход - со вторым входом блока управления режимами, при этом на входы второго и третьего делителей частоты с переменными коэффициентами деления подаются соответственно импульсы дополнительного и измеряемого сигналов, отличающееся тем, что дополнительно введены вычислитель, содержащий сумматор, два счетчика, два дополнительных сумматора, триггер-коммутатор, формирователь данных измерения и фиксатор, а также счетчик тактовых импульсов, первый вход которого соединен с входом опорных импульсов, второй вход - с входом опорного сигнала времени и с первым входом фиксатора в вычислителе, третий вход - с входом измеряемого сигнала времени, а выходы - с входами «n0» и «0,5ТИ» вычислителя, у которого управляющие входы соединены с управляющими выходами блока управления режимами, так что второй вход фиксатора вычислителя соединен с управляющим выходом сигнала «Готов», счетные входы сумматора - с выходами «Сигн.1» и «Сигн.2», а счетные входы первого и второго счетчиков и первые управляющие входы дополнительных сумматоров - с выходом «Измер», первый же выход вычислителя с триггер-коммутатора «1» соединен с управляющим входом блока управления режимами, а результирующий выход вычислителя с формирователя данных измерения является выходом устройства, при этом выход фиксатора соединен с первым управляющим входом сумматора, выход которого соединен со счетными входами первого и второго дополнительных сумматоров, вторые управляющие входы которых соединены с выходами триггер-коммутатора так, что выход «1» соединен с первым управляющим входом первого дополнительного сумматора и первым управляющим входом первого счетчика, а выход «0» - с первыми управляющими входами второго дополнительного сумматора и второго счетчика, выходы счетчиков - с входами триггер-коммутатора так, что выход счета первого счетчика соединен с входом установки «0» коммутатора, а выход окончания счета второго счетчика - с входом установки «1» и входом дополнительного суммирования первого дополнительного сумматора, причем оба выхода соединены с входом сброса данных в сумматоре, кроме того, третий управляющий вход первого дополнительного сумматора соединен с входом «0,5ТИ» вычислителя, а дополнительный счетный вход этого сумматора - с выходом второго дополнительного сумматора, а первый счетный вход формирователя данных измерения соединен с выходом первого дополнительного сумматора, второй счетный вход - с входом «n0» вычислителя, а управляющий вход - с выходом окончания счета первого счетчика и входом сброса фиксатора.