Интегрирующий преобразователь "аналог-цифра-аналог"

Иллюстрации

Показать всеУстройство относится к области вычислительной техники и может использоваться в системах автоматизации для прямого и обратного преобразования аналогового сигнала в цифровой код. Техническим результатом является повышение быстродействия и точности работы АЦП-ЦАП. Устройство содержит источник входного сигнала, сумматоры, интегратор, релейные элементы, n пропорциональных звеньев, n ключевых элементов, источник опорного цифрового кода и устройство вычитания кодов. 8 ил.

Реферат

Устройство относится к области вычислительной техники и может использоваться в системах автоматизации для прямого и обратного преобразования аналогового сигнала в цифровой код.

Известен аналого-цифровой преобразователь (АЦП) по методу двухтактного интегрирования, содержащий интегратор, ключевые элементы, генераторы импульсов, счетчик, регистр памяти, элемент задержки (Волович Г.И. Схемотехника аналоговых и аналогово-цифровых электронных устройств. / Г.И.Волович. - М.: Издательский дом «Додэка-XXI», 2005. - 459 с.).

Известное устройство имеет недостаточно высокую точность, что является следствием разомкнутого характера его структуры.

Известен способ аналого-цифрового преобразования последовательными во времени действиями поразрядного уравновешивания от старшего разряда к младшему и схемы его реализации в виде множества АЦП с общепринятым термином «поразрядного уравновешивания». При всем разнообразии таких АЦП они содержат источник входного сигнала, устройство его сравнения (первый сумматор) с сигналом выхода цифроаналогового преобразователя (ЦАП), кодовые входы которого одновременно являются кодом выхода всего АЦП и управляются кольцевым распределителем, который сам потактово управляется выходом устройства сравнения. Правильный код формируется и периодически фиксируется в конце каждого цикла тактов работы кольцевого распределителя (Темников Ф.Е. Теоретические основы информационной техники. / Темников Ф.Е., Афонин В.А., Дмитриев В.И. - М.: Энергия, 1979. - 512 с. См. стр.118, 119, рис.3-20, 3-21).

Недостатком устройства является его повышенная сложность, пониженное быстродействие из-за задержки на время цикла работы кольцевого распределителя, циклический характер выдачи результатов преобразования.

Наиболее близким к предлагаемому устройству является многозонный развертывающий преобразователь, содержащий последовательно включенные источник входного сигнала, первый сумматор и интегратор, выход которого подключен к входам группы из нечетного числа релейных элементов, выходы которых соединены с входами второго сумматора, выход которого соединен с выходом устройства и с вторым входом первого сумматора (SU №1183988 от 27 апреля 1984 г., опубл. 07.10.85. Бюл. №37).

Устройство служит для преобразования аналогового сигнала в многозонный сигнал с частотно-широтно-импульсной модуляцией (ЧШИМ).

В своем первоначальном виде устройство-прототип не может работать в режиме преобразования аналогового сигнала в цифру с последующим обратным цифроаналоговым преобразованием (ЦАП).

Для преобразования в код выходного сигнала устройства-прототипа требуется включение на его выходе сглаживающего фильтра и непосредственно АЦП того или иного принципа действия.

Такая структура будет иметь низкую точность работы и пониженное быстродействие, так как при ЧШИМ практически невозможно согласовать амплитудное значение пульсаций на выходе сглаживающего фильтра, которое потом может быть учтено как постоянное значение погрешности преобразования, с тактовой частотой АЦП.

Таким образом, известное техническое решение при построении на его основе АЦП будет характеризоваться низким быстродействием и невысокой точностью.

В то же время известное техническое решение относится к замкнутым системам регулирования, что позволяет при соответствующих схемотехнических дополнениях организовать на его основе высокоточный интегрирующий преобразователь «Аналог-Цифра-Аналог».

Технической задачей изобретения является повышение быстродействия и точности работы АЦП-ЦАП на базе известного интегрирующего многозонного частотно-широтно-импульсного развертывающего преобразователя.

Поставленная задача решается тем, что интегрирующий преобразователь «Аналог-Цифра-Аналог» содержит последовательно включенные источник входного сигнала, первый сумматор, интегратор и первый релейный элемент из группы, содержащей n-е число релейных элементов, причем n=1, 2, 3… целое число, второй сумматор, выход которого подключен к аналоговому выходу устройства и соединен со вторым входом первого сумматора, цифровые выходы устройства, характеризуется тем, что в него введены n-е число пропорциональных звеньев, n-1 дополнительных сумматоров, n-е число ключевых элементов, источник опорного цифрового кода и устройство вычитания кодов, причем выход каждого релейного элемента через соответствующее пропорциональное звено подключен к соответствующему входу второго сумматора, а также соединен с входом соответствующего ключевого элемента, выход каждого ключевого элемента соединен с первой группой входов устройства вычитания кодов, вторая группа входов которого соединена с соответствующими выходами источника опорного цифрового кода, выходы устройства вычитания кодов подключены к соответствующим цифровым выходам преобразователя «Аналог-Цифра-Аналог», при этом выход каждого из дополнительных сумматоров подключен к входу каждого релейного элемента, начиная со второго, первый вход каждого из дополнительных сумматоров соединен с выходом предыдущего из n-го числа пропорциональных звеньев, второй вход первого дополнительного сумматора соединен с выходом интегратора, а второй вход каждого из последующих дополнительных сумматоров подключен к выходу предыдущего дополнительного сумматора.

Предлагаемое устройство обеспечивает высокое быстродействие и точность работы АЦП-ЦАП.

Поставленная техническая задача достигается за счет того, что каналы АЦП и ЦАП оказываются охваченными общей отрицательной обратной связью, а также в прямом канале регулирования устройства находится интегратор, что повышает точность работы преобразователя при уменьшенной разрядности, повышает быстродействие, ликвидирует дискретность выдачи результата. Точность при понижении разрядности обеспечивается частотно-широтно-импульсной модуляцией между дискретами выходного кода.

Изобретение поясняется чертежами:

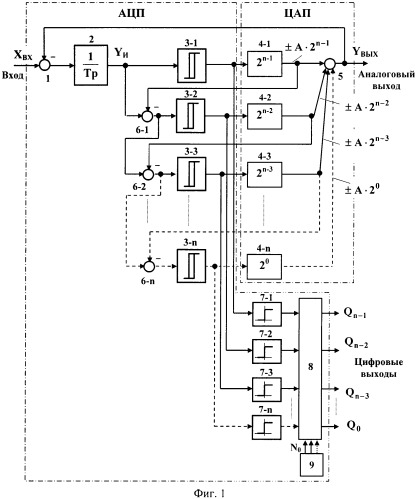

Фиг.1 - функциональная схема предлагаемого устройства;

Фиг.2, 3, 4, 5 - временные диаграммы сигналов интегрирующего преобразователя «Аналог-Цифра-Аналог»;

Фиг.6а, б - амплитудная и модуляционная характеристики интегрирующего преобразователя «Аналог-Цифра-Аналог»;

Фиг.7 - пример принципиальной схемы 4-х разрядного преобразователя;

Фиг.8 - осциллограммы сигналов преобразователя (пример конкретного выполнения предложенной системы).

В состав интегрирующего преобразователя «Аналог-Цифра-Аналог» (фиг.1) входят последовательно включенные первый сумматор 1, интегратор 2, первый релейный элемент 3-1, первое пропорциональное звено 4-1 с коэффициентом усиления 2n-1 и второй сумматор 5, последовательно включенные дополнительный третий сумматор 6-1, второй релейный элемент 3-2 и второе пропорциональное звено 4-2 с коэффициентом усиления 2n-2, последовательно включенные четвертый дополнительный сумматор 6-2, третий релейный элемент 3-3 и третье пропорциональное звено 4-3 с коэффициентом усиления 2n-3, последовательно включенные n-й дополнительный сумматор 6-n, n-й релейный элемент 3-n и n-е пропорциональное звено 4-n с коэффициентом усиления 20, а также в состав устройства входят ключи 7-1, 7-2, …, 7-n, входы которых подключены к соответствующим выходам релейных элементов 3-1, 3-2, …, 3-n, а выходы ключей 7-1, 7-2, …, 7-n соединены с первой группой входов устройства вычитания кодов 8, выходы которого являются «Цифровыми выходами» интегрирующего преобразователя «Аналог-Цифра-Аналог, и источник опорного цифрового кода 9, подключенного ко вторым входам устройства вычитания кодов 8. Причем выход второго сумматора 5 является «Выходом ЦАП» интегрирующего преобразователя «Аналог-Цифра-Аналог» и одновременно соединен с первым входом первого сумматора 1, второй вход которого подключен к источнику входного сигнала - «вход» интегрирующего преобразователя «Аналог-Цифра-Аналог». Первый вход третьего дополнительного сумматора 6-1 подключен к выходу интегратора 2, а второй вход третьего дополнительного сумматора 6-1 соединен с выходом первого пропорционального звена 4-1. Первый вход четвертого дополнительного сумматора 6-2 подключен к выходу третьего дополнительного сумматора 6-1, а второй вход четвертого дополнительного сумматора 6-2 соединен с выходом второго пропорционального звена 4-2. Первый вход n-го дополнительного сумматора 6-n подключен к выходу четвертого дополнительного сумматора 6-2, а второй вход n-го дополнительного сумматора 6-n соединен с выходом третьего пропорционального звена 4-3. Выходы пропорциональных звеньев 4-2, 4-3, …, 4-n соединены с соответствующими входами второго сумматора 5.

Звенья интегрирующего преобразователя «Аналог-Цифра-Аналог» (фиг.1) имеют следующие характеристики.

Сумматоры 1, 6-1, 6-2, …, 6-n содержат два входа с единичным коэффициентом передачи по каждому из них и выполняют операцию вычитания сигналов.

Интегратор 2 имеет передаточную функцию W(p)=1/Тр, где Т - постоянная времени интегрирования. При дискретном изменении входного воздействия выходной сигнал интегратора 2 изменяется по линейному закону со знаком, совпадающим со знаком сигнала на его входе.

Релейные элементы 3-1, 3-2, …, 3-n выполнены с симметричной относительно «нуля» петлей гистерезиса. Их выходной сигнал меняется дискретно в пределах ±А. Однако предельное быстродействие достигается при релейных элементах без гистерезиса, когда сложно описать последовательность их работы.

Пропорциональные звенья 4-1, 4-2, …, 4-n реализованы с коэффициентами усиления, которые изменяются в соответствии с весом разряда преобразуемого кода с произвольным основанием, но чаще с двоичным кодом, пропорциональным 2n-1, 2n-2, …, 20 соответственно. Здесь n - количество разрядов двоичного кода. Наибольший коэффициент пропорционального звена 2n-1 соответствует весу старшего разряда двоичного кода, а наименьший 20 - весу младшего разряда.

Сумматор 5 имеет n-е количество входов с единичным коэффициентом передачи по каждому из входов и выполняет операцию суммирования сигналов. Количество входов сумматора выбирается равным числу разрядов n преобразуемого двоичного кода.

Ключи 7-1, 7-2, …, 7-n преобразуют биполярные выходные импульсы релейных элементов 3-1, 3-2,…, 3-n в однополярные для последующего согласования выходов релейных элементов 3-1, 3-2, …, 3-n с цифровыми входами устройства вычитания кодов 8. Каждый ключ имеет нулевое значение порогов включения/выключения и неинвертирующую характеристику «вход-выход».

Устройство вычитания кодов 8 производит операцию поразрядного вычитания из кода N1, формируемого на выходе ключей 7-1, 7-2, …, 7-n, кода N2, задаваемого источником цифрового кода 9, и может выполняться как на основе стандартных микросхем, так и на базе программируемых контроллеров.

На фиг.1-6 приняты следующие обозначения:

Хвх - входной сигнал интегрирующего преобразователя («вход» устройства);

Yи - выходной сигнал интегратора 2;

Yвых - выходной сигнал сумматора 5 («аналоговый выход» устройства);

±А·2n-1, ±А·2n-2, ±А·2n-3, …, ±А·20 - максимальные уровни сигналов на выходе пропорциональных звеньев 4-1, 4-2, 4-3, …, 4-n соответственно;

±b - пороги переключения релейных элементов 3-1, 3-2, …, 3-n;

±А - амплитуда выходных импульсов релейных элементов 3-1, 3-2, …, 3-n;

Qn-1, Qn-2, Qn-3, …, Q0 - разряды цифрового кода на выходе интегрирующего преобразователя «Аналог-Цифра-Аналог»;

N1 - цифровой код на выходе ключей 7-1, 7-2, …, 7-n;

N2 - цифровой код, задаваемый источником цифрового кода 9;

N3 - цифровой код на выходе интегрирующего преобразователя «Аналог-Цифра-Аналог».

Принцип работы устройства следующий.

Интегрирующий преобразователь «Аналог-Цифра-Аналог» является замкнутой системой, поэтому в установившемся режиме работы уровень сигнала на входе преобразователя ХBX должен быть всегда уравновешен выходным напряжением YBЫХ ЦАП. Это возможно только при соответствующем (нужном) коде ЦАП. Когда разрядность ЦАП не обеспечивает нужную точность преобразования между уровнями, начинается режим частотно-широтно-импульсной модуляции между этими уровнями. Однако усредненная интегральная точность всегда обеспечивается из-за наличия интегратора в прямом канале регулирования. В результате амплитудная характеристика (фиг.6а) будет всегда линейной, а на появляющуюся частотно-широтно-импульсную модуляцию между дискретами указывает модуляционная характеристика на фиг.6б. Предельное быстродействие получается при нулевой ширине петель гистерезиса релейных элементов 3-1 - 3-n, когда частота автоколебаний получается предельно высокой (бесконечно большой). При этом порядок работы элементов будет самый неожиданный, неописуемый, хаотический, но соответствие выходного кода входному сигналу будет всегда обеспечено. Сказанное проверено путем экспериментальных исследований.

Видимо такой «неописуемый хаос» в работе предлагаемого устройства не позволил ранее подойти к подобному решению, так как всегда в АЦП вводили понятие «тактируемость», которая определяла жесткий порядок работы и иерархию элементов АЦП за цикл преобразования (см. Ф.Е.Темников).

Рассмотрим работу устройства при наличии гистерезиса у релейных элементов 3-1 - 3-n.

Для интегрирующего преобразователя входной сигнал можно представить в виде выражения ХBX=±Δ(k+0,5 m),

где - вес единицы младшего разряда преобразуемого кода в аналоговой форме; А - амплитуда выходных импульсов релейных элементов 3-1, 3-2, …, 3-n; - максимальное значение двоичного цифрового кода в десятичной системе счисления, формируемого на выходе ключей преобразователя 7-1, 7-2, …, 7-n; Аmax=А·Nmax - максимальная амплитуда на выходе преобразователя; k=0, 1, 2, …, - целые числа, соответствующие десятичным числам преобразуемого кода; m - коэффициент, учитывающий изменение входного сигнала на интервале Δ(-1,0≤m≤1,0).

Рассмотрим принцип работы преобразователя для входного сигнала XBX=0, когда числа k=0 и m=0.

Будем считать, что релейный элемент (РЭ) 3-1, формирующий старший разряд преобразуемого кода, находится в «положительном» состоянии (фиг.2б). Тогда амплитуда на выходе пропорционального звена (ПЗ) 4-1 равна А·2n-1. Для выполнения равенства XBX=Yвых все остальные РЭ 3-2, 3-3, …, 3-n в системе вынуждены переключиться в отрицательное положение (фиг.2в-д), тогда суммарный сигнал на выходе сумматора 5 YВЫХ=А(2n-1-2n-2-2n-3-, …, -20)=А (фиг.2е). Условие равенства ХВХ=YВЫХ является невыполнимым для XBX=0, поэтому сигнал YИ на выходе интегратора 2 начинает линейно спадать под действием напряжения -А с выхода первого сумматора 1 (фиг.2а), и при достижение равенства YИ(t)=-b первый РЭ 3-1 переключается в отрицательное состояние (фиг.2б), а остальные РЭ 3-2, 3-3, …, 3-n - в положительное (фиг.2в-д). Здесь b - порог переключения релейных элементов 3-1, 3-2, …, 3-n. В результате суммарный сигнал на выходе сумматора 5 YВЫХ=А(-2n-1+2n-2+2n-3-, …, +20)=-А

Таким образом, при XBX=0 интегрирующий преобразователь постоянно находится в режиме переключения всех релейных элементов с частотой несущих колебаний f0=1(4b ТИ,), где b=b, А - нормированное значение порогов переключения РЭ 3-1, 3-2, …, 3-n; ТИ - постоянная времени интегрирования интегратора 2.

Ключи 7-1, 7-2, …, 7-n преобразуют биполярные выходные импульсы релейных элементов 3-1, 3-2, …, 3-n в однополярные для последующего согласования выходов релейных элементов 3-1, 3-2, …, 3-n с цифровыми входами устройства вычитания кодов 8 (фиг.1). Положительному уровню сигнала на выходе РЭ 3-1, 3-2,…, 3-n соответствует сигнал логической «1» на выходе ключей 7-1, 7-2, …, 7-n, а отрицательному уровню - сигнал логического «0» (фиг.2б-д, ж-к). В результате при ХВХ=0 на выходе ключей 7-1, 7-2, …, 7-n формируется два значения двоичного кода N1 (фиг.2ж-к), равных: (Nmax+1)/2 и (Nmax-1)/2.

Устройство вычитания кодов (УВК) 8 производит операцию поразрядного вычитания из кода N1, формируемого на выходе ключей 7-1, 7-2, …, 7-n, кода N2, задаваемого источником цифрового кода (ИЦК) 9 так, чтобы цифровой код на выходе интегрирующего преобразователя N3=N1-N2 равнялся нулю. Примем значение кода N2=(Nmax+1)/2, тогда при ХВХ=0 выходной код преобразователя N3 в десятичной форме будет равен 0 или -1 (фиг.2л-о). В результате на выходе аналого-цифрового преобразователя (АЦП) формируется статическая ошибка, равная единице младшего разряда преобразуемого кода N3. При большом количестве разрядов интегрирующего преобразователя «Аналог-Цифра-Аналог» (n≥8) данная ошибка практически не оказывает никакого влияния на точность работы АЦП и ею можно пренебречь.

При других значениях k и m=0 преобразователь работает аналогично случаю с числами k=0 и m=0, когда в системе обязательно находятся в режиме переключения с несущей частотой f0=1/(4b TИ) хотя бы один из релейных элементов 3-1, 3-2, …, 3-n.

Рассмотрим работу преобразователя при других значениях m, отличных от нуля и изменяющихся в диапазоне - 1,0<m<1,0, и k=0, когда ХВХ=±А·m. Для данных значений устройство переходит в режим частотно-широтно-импульсной модуляции (ЧШИМ), при котором частота переключения РЭ 3-1, 3-2, …, 3-n уменьшается в соответствии с выражением f=f0·(1-m2) (фиг.3б-д). Состояние кодов N1 и N3 на выходе ключей 7-1, 7-2, …, 7-n и выходе преобразователя соответственно (фиг.3) сохраняется таким же, как и для случая k=0 и m=0 (фиг.2).

При m=1 и любых других целых значениях k частота переключения РЭ 3-1, 3-2, …, 3-n становится равной нулю и в АЦП возникает установившийся процесс, когда ХBX=YВЫХ. Так, например, при ХBX=А(k=0) первый РЭ 3-1 переключается в положительное состояние (фиг.4б), а остальные РЭ 3-2, 3-3, …, 3-n - в отрицательное положение (фиг.4в-д). В результате суммарный сигнал на выходе сумматора 5 YВЫХ=А(2n-1-2n-2-2n-3-, …, - 20)=А (фиг.4е) уравновешивается входным воздействием ХBX=А. Напряжение на выходе интегратора 2 достигает установившегося значения YИ{t)=b (фиг.4а) так, чтобы постоянно удерживать первый РЭ 3-1 в положительном состоянии (фиг.4б). Цифровой код N1 на выходе ключей 7-1, 7-2, …, 7-n равен значению (Nmax+1)/2 (фиг.4ж-к), а код на выходе преобразователя N3=0 (фиг.4л-о).

Аналогичным образом работает интегрирующий преобразователь при других значениях k и m=1. Например, максимально возможному значению k=(Nmax-1)/2 будет соответствовать максимальный уровень входного сигнала . Пусть XBX=А·Nmax, тогда все РЭ 3-1, 3-2, …, 3-n переключаются в положительное состояние (фиг.5б-д). В результате суммарный сигнал на выходе сумматора 5 YВЫХ=А(2n-1+2n-2+2n-3+, …, +20)=А·Nmax (фиг.5е) уравновешивается входным воздействием ХBX=А·Nmax. Напряжение на выходе интегратора 2 достигает установившегося значения Yи(t)=(Nmax-1)+b (фиг.5а) так, чтобы постоянно удерживать все РЭ 3-1, 3-2,…, 3-n в положительном состоянии (фиг.5б-д). Все выходы ключей 7-1, 7-2, …, 7-n находятся в состоянии логической «1» (фиг.5ж-к), что соответствует максимальному коду N1=Nmax. При вычитании из кода N1 кода N2=(Nmax+1)/2 получаем код на выходе преобразователя N3=(Nmax-1)/2 (фиг.5л-о).

При ХBX=-A·Nmax, наоборот, все РЭ 3-1, 3-2, …, 3-n переключаются в отрицательное состояние, когда напряжение на выходе сумматора 5 изменяет знак и становится равным YВЫХ=-А(2n-1+2n-2+2n-3+, …, +20)=-А·Nmax. Все выходы ключей 7-1, 7-2, …, 7-n находятся в состоянии логического «0», что соответствует минимальному коду N1=0. При вычитании из кода N1 кода N2=(Nmax+1)/2 получаем выходной код N3=-(Nmax+1)/2.

Амплитудная и модуляционная характеристики интегрирующего преобразователя «Аналог-Цифра-Аналог» в относительных единицах приведены на фиг.6а, б соответственно. Здесь - нормированное значение входного сигнала, отнесенного к максимальной амплитуде на выходе преобразователя Аmax=А·Nmax; f=f/f0 - нормированное значение частоты выходных импульсов РЭ 3-1, 3-2, …, 3-n, отнесенной к несущей частоте f0=1/(4b ТИ) при нулевом значении сигнала на входе АЦП.

На фиг.7 приведен фрагмент принципиальной схемы 4-х разрядного преобразователя (без устройства вычитания кодов). Там же указано функциональное назначение элементов принципиальной схемы, которое не требует дополнительных пояснений.

На фиг.8 приведены осциллограммы преобразователя. Фиг.8-а соответствует случаю нулевого значения входного сигнала. При гармоническом входном воздействии (фиг.8б) выходной сигнал ЦАП имеет форму ступенчато-аппроксимированной синусоиды. Искажения формы «ступенек» вызваны свойствами цифрового осциллографа.

Таким образом, введение в схему дополнительных сумматоров 6-1-6-n, пропорциональных звеньев 4-1 - 4-n, ключей 7-1 - 7-n и устройства вычитания кодов 8 с источником цифрового кода 9 позволяет реализовать интегрирующий метод АЦП и ЦАП с контуром обратной связи, что в значительной степени повышает точность работы преобразователя в целом.

Рассмотренный преобразователь предполагается предложить фирмам-изготовителям интегральных микросхем для его серийного производства на интегральной основе.

Интегрирующий преобразователь «Аналог-Цифра-Аналог», содержащий последовательно включенные источник входного сигнала, первый сумматор, интегратор и первый релейный элемент из группы, содержащей n-е число релейных элементов, причем n=1, 2, 3 … целое число, второй сумматор, выход которого подключен к аналоговому выходу устройства и соединен со вторым входом первого сумматора, цифровые выходы устройства, отличающийся тем, что в него введены n-е число пропорциональных звеньев, п-1 дополнительных сумматоров, n-е число ключевых элементов, источник опорного цифрового кода и устройство вычитания кодов, причем выход каждого релейного элемента через соответствующее пропорциональное звено подключен к соответствующему входу второго сумматора, а также соединен с входом соответствующего ключевого элемента, выход каждого ключевого элемента соединен с первой группой входов устройства вычитания кодов, вторая группа входов которого соединена с соответствующими выходами источника опорного цифрового кода, выходы устройства вычитания кодов подключены к соответствующим цифровым выходам преобразователя «Аналог-Цифра-Аналог», при этом выход каждого из дополнительных сумматоров подключен к входу каждого релейного элемента, начиная со второго, первый вход каждого из дополнительных сумматоров соединен с выходом предыдущего из n-го числа пропорциональных звеньев, второй вход первого дополнительного сумматора соединен с выходом интегратора, а второй вход каждого из последующих дополнительных сумматоров подключен к выходу предыдущего дополнительного сумматора.