Радиомодем

Иллюстрации

Показать всеИзобретение относится к технике электросвязи и может быть использовано в системах передачи данных по КБ и УКВ радиоканалам. Технический результат заключается в повышении помехоустойчивости устройства, в том числе и путем устранения влияния сосредоточенной по спектру помехи, попадающей в полосу частот одного из параллельных подканалов, на остальные подканалы. Технический результат достигается за счет использования в многочастотном модеме с дифференциальной многократной фазовой модуляцией и квадратурной реализацией модулятора и демодулятора процедур первоначальной оценки вносимого каналом частотного сдвига на основе пилот-сигнала; установления посимвольной синхронизации и слежения за положением посимвольной синхронизации и частотным сдвигом с применением рабочего сигнала. 38 ил.

Реферат

Предлагаемое изобретение относится к технике электросвязи и может быть использовано в системах передачи данных по KB и УКВ радиоканалам.

Уже известны радиомодемы, описанные, например, в работах [1, 2] и основанные на последовательной передаче данных по радиоканалу с замираниями. Наличие в таких каналах эффекта многолучевости, при котором задержка распространения отдельных лучей достигает нескольких миллисекунд, приводит к существенной межсимвольной интерференции (МСИ). Для борьбы с этим явлением используются адаптивные корректоры, основанные на периодическом оценивании характеристик канала путем тестирования его специальной последовательностью. Эта последовательность должна быть достаточно длинной, чтобы отразить все особенности характеристик канала, обусловленные наличием МСИ. Это приводит к снижению скорости передачи (также при этом уменьшается полезная мощность передаваемого сигнала). Поэтому как отмечается в работе [3], подобные устройства обладают относительно низкой информационной скоростью.

Известны параллельные радиомодемы [4], построенные с использованием нескольких десятков пилот-сигналов, параметры которых зависят только от состояния среды распространения и могут быть определены и использованы в процессе демодуляции на приемной стороне радиолинии. Наличие большого числа неинформативных сигналов существенно снижает как энергетическую эффективность подобных устройств, так и эффективность использования ими выделенной полосы частот, что в конечном итоге приводит к уменьшению помехоустойчивости.

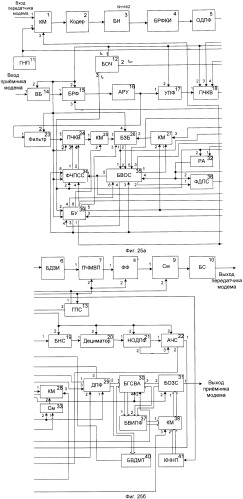

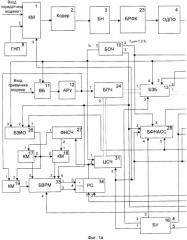

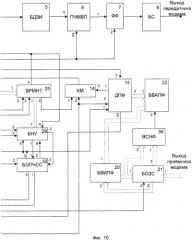

Известен параллельный радиомодем [5], наиболее близкий к предлагаемому изобретению. Структурная схема этого устройства приведена на фиг.1. Отметим, что с целью обеспечения возможности выявления существенных отличительных признаков заявляемого объекта на фиг.1 представлена функциональная схема устройства, построенная в строгом соответствии с приводимым в тексте работы [5] описанием принципов реализации и взаимодействия отдельных узлов данного устройства. Представленная функциональная схема является более полной и подробной, чем на фиг.12-17 вышеупомянутой работы [5]. Радиомодем содержит пять коммутаторов (КМ) 1, 14, 17, 18 и 19, кодер 2, буферный накопитель (БН) 3, блок 23 распределения и формирования кадров (БРФК), блок 4 вычисления обратного дискретного преобразования Фурье (ОДПФ), блок 5 добавления защитного интервала (БДЗИ), преобразователь числового массива во временную последовательность (ПЧМВП) 6, формирующий фильтр (ФФ) 7, блок 8 согласования (БС), генератор настроечной последовательности (ГНП) 9, блок 10 опорных частот (БОЧ), входной блок (ВБ) 11, блок 12 автоматической регулировки усиления (АРУ), блок 24 преобразователей частоты (БПЧ), буферный запоминающий блок 13 (БЗБ), вычислитель разностной мощности несигнального тона 25 (ВРМНТ), блок 15 дискретного преобразования Фурье (ДПФ), блок 22 вычисления аргумента и поворота фазы (БВАПФ), блок 26 задания интервала ортогональности (БЗИО), формирователь 27 отсчетов несущих со смещенными частотами (ФНСЧ), блок 28 формирования начального адреса при тестировании символьной синхронизации (БФНАСС), блок 29 накопления и усреднения (БНУ), блок 30 вычисления среднего набега фазы (ВСНФ), блок 31 цифровых синтезаторов частот (ЦСЧ), блок 32 определения оптимальных положений частотной и символьной синхронизации (БОПЧСС), блок 20 вычисления информативного приращения фазы (БВИПФ), блок 21 оценки значений символов и эталонной фазы (БОЗС), блок 33 вычисления разностной мощности и усреднения (БВРМ), реверсивный счетчик (PC) 34 и блок 16 управления (БУ), причем первый вход коммутатора 1 соединен со входом передатчика модема, второй вход этого коммутатора подключен к генератору настроечной последовательности 9, третий вход коммутатора 1 соединен с первым выходом БУ 16, третьим входом блока 31 цифровых синтезаторов частот, первым входом блока 28 формирования начального адреса, вторыми входами блока 29 усреднения и блока 32 определения оптимальных положений частотной и символьной синхронизации; выход коммутатора 1 подключен ко входу кодера 2, выход кодера 2 связан со входом буферного накопителя 3, выход буферного накопителя 3 соединен со входом блока 23 распределения и формирования кадров, выход которого подключен ко входу блока 4 вычисления ОДПФ, выход блока 4 вычисления ОДПФ связан со входом блока 5 добавления защитного интервала 5, выход которого соединен с первым входом преобразователя числового массива во временную последовательность 6, второй вход которого связан с первым выходом БОЧ 10, со вторыми входами формирующего фильтра 7 и входного блока 11, с четвертым входом буферного запоминающего блока 13, третьим входом блока 26 задания интервала ортогональности и первым входом блока 31 цифровых синтезаторов частот, выход преобразователя числового массива во временную последовательность 6 подключен к первому входу формирующего фильтра 7, выход которого соединен со входом блока 8 согласования, выход блока согласования связан со входом канала; выход канала связи подключен к первому входу входного блока 11, выход которого соединен со входом АРУ 12, выход АРУ связан с первыми входами блока 24 преобразователей частоты и коммутатора 19, второй вход блока 24 подключен к выходу блока 31 цифровых синтезаторов частот, выход блока 24 преобразователей частоты соединен с первым входом буферного запоминающего блока 13, второй вход которого связан с выходом второго коммутатора 14, третий вход буферного запоминающего блока 13 подключен ко второму выходу блока управления 16; первый и второй выходы буферного запоминающего блока 13 соединены соответственно с первым входом вычислителя разностной мощности несигнального тона 25 и третьим входом блока 15 ДПФ, второй вход вычислителя разностной мощности несигнального тона 25 связан с выходом блока 28 формирования начального адреса при тестировании символьной синхронизации, третий вход вычислителя разностной мощности несигнального тона 25 соединен с третьим входом блока 29 накопления и усреднения и четвертым выходом блока управления 16; четвертый вход вычислителя 25 разностной мощности несигнального тона подключен к четвертому входу блока 29 накопления и усреднения, третьему входу блока 28 формирования начального адреса при тестировании символьной синхронизации и второму выходу БОЧ 10, первый выход вычислителя разностной мощности несигнального тона 25 связан с первым входом блока 29 накопления и усреднения, второй выход вычислителя 25 соединен с первым входом коммутатора 14, второй вход коммутатора 14 подключен к пятому выходу БУ 16 и второму входу блока ДПФ 15, третий вход коммутатора 14 связан с первым выходом блока ДПФ 15, первый вход блока 15 ДПФ соединен с пятыми входами блока 28 формирования начального адреса при тестировании символьной синхронизации и блока 29 накопления и усреднения, первым входом блока 26 задания интервала ортогональности и третьим выходом блока 32 определения оптимальных положений частотной и символьной синхронизации, второй выход блока ДПФ 15 подключен к первому входу блока 22 вычисления аргумента и поворота фазы, третий выход блока ДПФ 15 соединен с четвертым входом блока 33 вычисления разностной мощности и усреднения, второй вход блока 22 вычисления аргумента и поворота фазы связан с выходом блока 30 вычисления среднего набега фазы, выход блока 22 вычисления аргумента и поворота фазы подключен к первому входу блока 20 вычислителей информативного приращения фазы, второй вход блока 26 задания интервала ортогональности соединен с третьим выходом БОЧ 10, вторыми входами блока 28 формирования начального адреса при тестировании символьной синхронизации, блока 21 оценки значений символов и эталонной фазы и пятым входом блока 33 преобразования частоты, выход блока 26 задания интервала ортогональности связан со вторыми входами коммутаторов 17, 18 и 19, вход формирователя 27 отсчетов несущих со смещенными частотами подключен к выходу реверсивного счетчика 34 и второму входу блока 31 цифровых синтезаторов частот, первый и второй выходы формирователя отсчетов несущих со смещенными частотами 27 соединены с первыми входами соответственно коммутаторов 17 и 18, четвертый вход блока 28 формирования начального адреса при тестировании символьной синхронизации связан с третьим выходом блока управления 16; шестой вход блока 29 накопления и усреднения подключен ко второму выходу блока 32 определения оптимальных положений частотной и символьной синхронизации; первый и второй выходы блока 29 усреднения соединены соответственно с первым и третьим входами блока 32 определения оптимальных положений частотной и символьной синхронизации; первый вход блока 30 вычисления среднего набега фазы связан с третьим выходом блока 31 оценки значений символов и эталонной фазы, второй вход блока 30 вычисления среднего набега фазы подключен к выходу блока 20 вычислителей информативного приращения фазы, соединенному с первым входом блока 21 оценки значений символов и эталонной фазы, выходы коммутаторов 17 и 18 связаны соответственно с третьим и вторым входами блока 33 вычисления разностной мощности и усреднения, второй вход блока 20 вычислителей информативного приращения фазы соединен со вторым выходом блока 26 оценки значений символов и эталонной фазы, первый выход которого является выходом модема, выход коммутатора 19 связан с первым входом блока 33 вычисления разностной мощности и усреднения, первый и второй выходы блока 33 вычисления разностной мощности и усреднения подключены соответственно к последовательным входам сложения 3 и вычитания 4 реверсивного счетчика 34, первый и второй входы параллельной записи кода которого соединены соответственно с первым и четвертым выходами блока 32 определения оптимальных положений частотной и символьной синхронизации.

Работа устройства осуществляется следующим образом. Подлежащие передаче данные поступают на первый вход коммутатора 1, на второй вход которого подается цифровой сигнал с выхода генератора настроечной последовательности 9. На третий вход коммутатора 1 с первого выхода блока 22 управления подается сигнал, изображенный на строке в временной диаграммы, представленной на фиг.2. Как будет показано ниже, в процессе работы модема можно выделить 2 режима (цикла): режим вхождения в связь (1-й цикл) и режим передачи данных (2-й цикл). В течение 1-го цикла под воздействием единичного уровня на управляющем входе 3 к выходу коммутатора 1 подключается выходной сигнал генератора настроечной последовательности 9, а в течение 2-го цикла («0» на входе 3) - подлежащие передаче данные. Выходной сигнал коммутатора поступает на вход кодера 2. В модеме предполагается использование дифференциальной многократной фазовой модуляции с квадратурной реализацией модулятора и демодулятора [6], возможно применение квадратурно-амплитудной модуляции. В кодере 2 последовательность символов данных разбивается на группы по q бит (значение q выбирается из условия применения 2q - кратной модуляции). Каждой из возможных m-разрядных двоичных кодовых комбинаций ставится в соответствие определенный фазовый сдвиг, выбираемый из ряда 0, ,…, ,…, . При этом i-й фазовый сдвиг φi может быть представлен на плоскости с помощью единичного радиус-вектора, образующего угол φi с осью абсцисс. Координаты этого вектора: абсцисса a сn (синфазная составляющая) и ордината a кв n (квадратурная составляющая). Анализируя состав образованной q-битной группы из поступивших данных, кодер 3 выбирает соответствующие группе данных значения a сn и a кв n и передает их в буферный накопитель 3. Отметим, что для дальнейшего описания работы схемы удобно ввести в рассмотрение комплексный сигнал:

содержащий одновременно информацию и об a сn и a кв n; при этом мнимая единица j в данном случае выполняет роль метки, отличающей квадратурную составляющую от синфазной. В буферном накопителе 3 осуществляется накопление NT последовательно поступающих на его вход символов сигнала , что необходимо для реализации параллельного способа передачи данных с использованием метода уплотнения с ортогонально-частотным разделением (OFDM - Orthogonal Frequency Division Multiplexing). Для обеспечения высокой скорости передачи данных число параллельных подканалов, а следовательно, и число поднесущих в спектре сигнала должно быть большим. Однако такую систему сложно реализовать по классической схеме с числом модуляторов, равным числу несущих. Вместе с тем существует возможность выполнить операцию модуляции во всех подканалах одновременно с гораздо меньшими реализационными затратами на основе эффективных методов цифровой обработки сигналов, а именно вычисляя ОДПФ с использованием алгоритма ОБПФ [7]. Если N/2 символов модулирующего сигнала дополнить N/2 комплексно сопряженными символами

то после вычисления N-точечного ОДПФ получаем массив вещественных чисел:

Элементы массива {а k, k=0÷{N-1)} можно рассматривать как дискретные отчеты суммы выходов всех модуляторов параллельных каналов, взятые в моменты времени:

kΔt=kTopm/N,

где Тopm - длительность интервала ортогональности. Отметим, что размер ОДПФ N равен числу дискретных отсчетов модулированного сигнала на интервале ортогональности. Эффективное вычисление суммы (3) возможно с помощью алгоритма БПФ, при этом желательно, чтобы размер ОДПФ N был целой степенью числа 2. При этом число NT накопленных в узле 2 символов сигнала по разным соображениям [5, §3.3.2, 3.3.3] выбирается меньшим N/2, т.е.

Это означает, что в передаваемом сигнале модема имеются неиспользуемые частоты. В блоке 23 производится дополнение NT накопленных блоком 3 символов до N/2 нулевыми значениями (соответствующими неиспользуемым частотам) и дополнение полученного массива еще N/2 символами , вычисляемыми по правилу (2). Сформированный таким образом N-точечный массив комплексных данных подается на вход блока 4. В блоке 4 формируется совокупность значений фигурирующих в сумме (3) комплексных экспонент . Эти сигналы образуются аналогично комплексному символу , задаваемому (1), в соответствии с формулой Эйлера:

Реализация этой операции может быть выполнена таким образом: в запоминающем устройстве записаны N равноудаленных отсчетов периода гармонического колебания. Меняя адреса считываемых отсчетов в соответствии со значениями n и k, предписываемыми формулой (3) (или алгоритмом БПФ), и учитывая, что адреса отсчетов синусоиды задержаны на N/4 относительно адресов косинусоиды с той же фазой, получают значения колебаний, объединение которых в соответствии с (5) дает С использованием этих значений и отсчетов входного сигнала в соответствии с выражением (3) (либо непосредственно по этой формуле либо с использованием алгоритма БПФ) в блоке 4 осуществляется вычисление ОДПФ. В результате по окончании вычисления ОДПФ на выходе блока 4 получается массив из N действительных чисел, равных отсчетам последовательности a(kΔt)=a k, определяемой (3). В блоке 5 добавления защитного интервала длина этого массива увеличивается путем его циклического расширения до S=N+NЗИ отсчетов, где NЗИ - количество отсчетов, содержащихся в защитном интервале OFDM-символа длительностью

где Δt - шаг дискретизации, определяемый соотношением (4).

Механизм формирования циклического расширения иллюстрируется фиг.3 и заключается в помещении копии NЗИ оконечных отсчетов выхода ОДПФ в начало OFDM-символа (формирование префикса).

Наличие защитного интервала необходимо для устранения межсимвольной интерференции, обусловленной многолучевостью, вследствие которой первые NЗИ отсчетов очередного OFDM-символа оказываются искаженными и при демодуляции просто отбрасываются. Восстановление принятой информации осуществляется по N отсчетам исходной части символа OFDM (фиг.3) с использованием для демодуляции N-точечного ДПФ.

Выходной массив блока 5 добавления защитного интервала, содержащий S отсчетов, поступает на первый вход преобразователя числового массива во временную последовательность 6, на второй вход которого с первого выхода блока опорных частот 8 поступают импульсы частоты дискретизации (строка а временной диаграммы, изображенной на фиг.2):

Выходной сигнал блока 6 поступает на формирующий фильтр (ФФ) 7, представляющий собой цифровой полосовой фильтр, который ограничивает спектр общего OFDM сигнала в соответствии с эффективной полосой пропускания телефонного канала. Выходной сигнал блока 7 поступает в блок согласования 8, где осуществляется цифроаналоговое преобразование и нормирование по уровню сформированного сигнала, после чего сигнал передается по каналу связи.

Прежде чем приступить к описанию работы структурной схемы приемника модема, изображенной на фиг.1, отметим, что задачей приемника является демодуляция принимаемого сигнала OFDM. Она может достаточно просто решена на основе вычисления дискретного преобразования Фурье (ДПФ) с использованием алгоритмов БПФ [7]. Однако при этом необходимо наличие совершенной символьной синхронизации и устранение частотного сдвига, вносимого радиоканалом.

Поскольку в KB модемах возможен значительный сдвиг частоты несущих передаваемого сигнала, который к тому же непрерывно изменяется во времени, оценка этого сдвига, необходимая для его устранения, обычно осуществляется в 2 этапа: вначале производиться грубая оценка, а затем точная. Таким образом, укрупненная структурная схема приемника модема имеет вид, показанный фиг.4 (в описании прототипа [5] она приведена на фиг.14). Обозначения узлов, приведенных фиг.4, расшифровываются следующим образом: ПЧ - преобразователь частоты, БВ - блок вычисления ДПФ.

В процессе работы системы синхронизации обычно выделяют 2 этапа: первоначальная оценка синхропараметров, имеющая место на этапе вхождения в связь, и слежение за изменяющимися значениями синхропараметров, производимое в процессе работы модема.

В устройстве-прототипе для установления символьной синхронизации используется метод «отстающего и опережающего окна», сущность которого иллюстрируется фиг.5.

На фиг.5 показано временное расположение двух последовательно поступивших OFDM-символов, содержащих по S отсчетов принимаемого сигнала (верхняя строка), а также соответствующее правильно установленной символьной синхронизации среднее положение блока из N отсчетов OFDM-символа и 2 его смещенных на NЗИ/2 отсчетов положения, причем первое смещено в сторону опережения (опережающее окно), а второе - отставания (отстающее окно).

Как отмечалось при описании передатчика в передаваемом сигнале имеются тоны, не используемые для передачи данных. Положим, что один из таких тонов находится в подканале с номером n.

Изображенная на фиг.5 ситуация характеризуется тем, что все отсчеты опережающего и отстающего окон принадлежат одному и тому же OFDM символу. При этом мощность n-го отсчета ДПФ, вычисленного по N отсчетам входного сигнала, входящим в опережающее окно, будет равна мощности n-го отсчета ДПФ, вычисленного по N отсчетам, принадлежащим отстающему окну. В итоге выходной сигнал узла вычитания УВ на фиг.5 будет равен нулю, что и говорит о наличии установленной символьной синхронизации. При нарушенной символьной синхронизации, отсчеты одного из окон выйдут за пределы одного OFDM-символа, баланс мощностей неиспользуемых отсчетов ДПФ, вычисленных на основе отстающего и опережающего окон, будет нарушен, и выходной сигнал узла вычитания будет отличен от нуля. Таким образом, по сигналу на выходе УВ можно судить о наличии символьной синхронизации.

Грубая оценка частотного сдвига в прототипе осуществляется методом, похожим на вышеописанный метод «опережающего» и «отстающего» окна, но реализуемым в частотной области. Идея метода иллюстрируется блок-схемой, представленной на фиг.6.

Эта схема включает в себя 2 преобразователя частоты ПЧ1 и ПЧ2, осуществляющих перенос спектра входного сигнала на частоты соответственно Δƒ+ΔƒD и Δƒ-ΔƒD, где Δƒ - значение тестируемой величины частотной расстройки, а ΔƒD - девиация частотной расстройки, необходимая для реализации данного метода (в работе [5] рекомендуется выбирать ΔƒD=0,1ΔFOFDM, где ΔFOFDM - ширина полосы пропускания одного подканала при OFDM передаче).

Вычислению мощности, например, выбранного для установления синхронизации, n-го неинформационного отсчета ДПФ должно предшествовать его выделение, осуществляемое путем вычисления n-го отсчета ДПФ входного сигнала.

При нулевой частотной расстройке, мощности, вычисленные в нижней и верхней ветвях схемы, являются одинаковыми и на выходе узла вычитания УВ присутствует нулевой сигнал, при наличии ухода частоты баланс мощностей нарушается и знак выходного сигнала УВ указывает знак частотной расстройки.

Идея выполнения точной оценки частотного сдвига основана на использовании решений о значении символа, переданного по i-му подканалу, и будет подробнее пояснена при описании реализации устройства-прототипа.

Необходимо отметить, что рассмотренный метод посимвольной синхронизации предполагает, что вносимый каналом частотный сдвиг спектра принимаемого сигнала полностью устранен. Аналогично иллюстрируемый на фиг.6 метод оценки частотного сдвига является корректным лишь при наличии установленной посимвольной синхронизации.

Вместе с тем, на этапе вхождения в связь оба названных условия не выполняются. В этой ситуации в прототипе реализуется алгоритм совместного оценивания посимвольной синхронизации и частотного сдвига, основанный на Nуср-кратном тестировании всех возможных сочетаний положений символьной синхронизации и значений частотного сдвига, усреднении и запоминании результатов и последующем отыскании оптимальных положений синхропараметров как координат ячейки таблицы с минимальным значением усредненного результата тестирования.

Рассмотрим далее, как все изложенное реализуется в схеме прототипа, представленной на фиг.1.

Сигнал, поступающий из канала связи, подается на первый вход входного блока 11, на второй вход которого с выхода БОЧ 10 подаются тактирующие импульсы, следующие с частотой дискретизации ƒd (строка а временной диаграммы фиг.2). В входном блоке 11 осуществляется фильтрация и аналого-цифровое преобразование. Далее отсчеты цифрового сигнала поступают на вход блока 12 АРУ, который нормализует уровень принимаемого сигнала. После этого отсчеты принятого цифрового сигнала s(kΔt) подаются на первый вход блока преобразователей частоты 24. Структурная схема блока 24 показана на фиг.7. Она представляет собой последовательное соединение преобразователя Гильберта ПГ и набора из Nчс параллельно включенных идентичных по построению преобразователей частоты ПЧ1, ПЧ2,…, ПЧNчс, где Nчc - число тестируемых на этапе вхождения в связь значений оценки частотного сдвига, вносимого каналом.

Необходимость параллельного включения такого большого числа преобразователей частоты обусловлена тем, что ввиду достаточно быстрого изменения во времени параметров радиоканала выбранный в прототипе алгоритм совместного оценивания посимвольной синхронизации и частотного сдвига, основанный на переборе всех возможных комбинаций и последующем усреднении, имеет практический смысл лишь в том случае, когда оценка всех тестируемых значений частотного сдвига выполняется одновременно. При этом в течение одной посылки OFDM символа появится возможность (при достаточном быстродействии выбранной элементной базы) оценки методом «отстающего» и «опережающего» окна всех Nпс тестируемых положений посимвольной синхронизации, и общее время вхождения в синхронизм будет определяться лишь числом Nуcp OFDM-посылок, на которых производится усреднение результатов тестирования. Попытка реализовать данный алгоритм путем последовательного тестирования разных значений частотного сдвига сделает данную процедуру бессмысленной, поскольку за время ее выполнения параметры канала изменятся столь существенным образом, что результат оценивания окажется недостоверным.

Схема конкретной реализации i-го преобразователя частоты ПЧi представлена на фиг.8. Она включает в себя два перемножителя и узел сложения. Выходной сигнал ПЧi sΔωi (kΔt) описывается выражением:

где Сигналы cos ΔωikΔt и sin ΔωikΔt, поступающие на вторые входы перемножителей схемы фиг.8, подаются на входы блока 24 с соответствующих выходов блока 31 цифровых синтезаторов частот. Структурная схема блока 31 представлена на фиг.9 и включает в себя ключ K и Nчс цифровых синтезаторов частоты ЦСЧ1, ЦСЧ2,…, ЦСЧNчс. Отметим, что схема ЦСЧ1 несколько отличается от схем остальных ЦСЧi, i≠1, поэтому на фиг.10 отдельно изображена структура ЦСЧi, i≠1, а на фиг.11 - ЦСЧ1.

Как уже отмечалось, в процессе работы модема можно выделить 2 режима: режим вхождения в связь, в котором осуществляется первоначальная оценка синхропараметров и режим работы, в котором осуществляется прием передаваемых данных и необходимое для этого отслеживание изменений синхропараметров (положения посимвольной синхронизации и частотного сдвига), обусловленных изменением во времени параметров канала.

В режиме вхождения в связь по сигналу с первого выхода блока управления 22, поступающему на третий вход блока 31, открывается ключ К в схеме фиг.9, и импульсы с частотой дискретизации ƒd, подаваемые на первый вход блока 31 с первого выхода блока опорных частот 10, поступают на входы всех ЦСЧi, i=1÷Nчс. Функциональная схема одного узла ЦСЧi, i≠1 (фиг.10) включает в себя два ЗУ, в одном из которых записаны Nп отсчетов дискретизированного периода косинусоиды, а в другом - синусоиды. Адрес считываемого на k-м шаге дискретизации отсчета определяется кодом на выходе соответствующего сумматора, этот код представляет собой сумму по модулю Nп числа, зарегистрированного в регистре адреса (Рг Адр) и некоторого числа ΔNi, хранящегося в регистре Pг ΔNi, и определяющего частоту Δωi, считываемых с ЦСЧ; дискретизированных гармонических колебаний cos ΔωikΔt и sin ΔωikΔt. Значение ΔNi определяется из соотношения:

где Δƒi=Δωi/2π. Через элемент задержки ЭЗ (см. фиг.10) выходной код сумматора подается на вход схемы переписи кода (СПК), посредством которой с приходом на первый вход ЦСЧ 31 очередного импульса дискретизации переписывается в Рг Адр. Элемент задержки ЭЗ обеспечивает возможность считывания отсчетов ЦСЧ (до их изменения), подготовленных аналогичным образом на предыдущем шаге дискретизации, соответствующим ПЧi (см. фиг.7).

Отличие схемы ЦСЧ1, изображенной на фиг.11, от рассмотренной схемы заключается в том, что посредством коммутатора, управляемого поступающим на третий вход блока 31 сигналом с первого выхода блока управления 16, в течение первого режима работы модема к одному из входов сумматоров подключается выход регистра Рг ΔN1 (так же как и в схеме фиг, 10), а во втором режиме - выход реверсивного счетчика 34, связанный со вторым входом блока 31 синтезатора частот.

Таким образом, в первом режиме работы модема на Nчс выходах блока 31 формируются Nчс вариантов дискретизированного выходного сигнала с устраненным в разной степени влиянием оцениваемого частотного сдвига, вносимого радиоканалом. Эти сигналы поступают через блок 24 преобразователей частот на Nчс входов Вх1,…, ВхNчс буферного запоминающего блока 13 (все они обозначены как первый вход). Функциональная схема буферного запоминающего блока 13 изображена на фиг.12. Она включает в себя Nчc идентичных буферных запоминающих узлов БЗУi… Блок-схема узла БЗУi показана на фиг.13, а алгоритм его работы - на фиг.14. Узел БЗУi изображенный на фиг.13, состоит из ЗУ1, содержащего S ячеек памяти, и ЗУ2, включающего 2 S ячеек. Для описания алгоритма работы БЗУi удобно в составе ЗУ2 выделить ЗУ2-1, включающее первые S ячеек памяти с адресами 0÷(S-1) и ЗУ2-2, включающее оставшиеся S ячеек с адресами S÷(2S-1). Процессами записи и считывания информации в БЗУi управляет узел управления УУ БЗУi. Поскольку форма реализации описываемого модема и входящих в его состав блоков предполагает использование программируемого многофункционального средства, на фиг.14 представлен алгоритм функционирования блока БЗУi, из которого становятся ясными функции, выполняемые узлом УУ БЗУi. В результате анализа сигнала, поступающего на третий вход буферного запоминающего блока 13 (фиг.12, фиг.13) со второго выхода блока управления 16 фиг.1 (см. строку д временной диаграммы работы устройства, изображенной на фиг.2), УУ БЗУi фиг.13 обеспечивает выполнение действий, предписываемых либо блоками 1 и 2 алгоритма фиг.14 (эти процедуры выполняются параллельно во времени) либо блоками 3 и 4 алгоритма фиг.14, реализуемыми последовательно во времени. Как видно из временной диаграммы, при этом в течение почти всей длительности TS=1/ƒS OFDM-символа (строка в диаграммы фиг.2) осуществляется считывание информации, зафиксированной в ЗУ2 и необходимой для тестирования различных положений посимвольной синхронизации, выполняемого в соответствии с описанным выше алгоритмом «отстающего» и «опережающего» окна (блок 1 алгоритма), и последовательная во времени запись в ЗУ1 новых отсчетов сигнала с выхода блока 10 преобразования частот, поступающих с частотой дискретизации ƒd (блок 2 алгоритма). Последовательность тактирующих запись импульсов с частотой ƒd подается на второй вход буферного запоминающего блока 13 фиг.1.

Для реализации использованного в данном устройстве и изложенного выше метода синхронизации необходимо на этапе вхождения в связь (т.е. в 1-м режиме работы модема) S раз в течение одного OFDM-символа обеспечить считывание N отсчетов, поступивших на буферный запоминающий блок 13 с блока 24 преобразования частоты сигнала, при этом начальный адрес каждой партии из N отсчетов должен последовательно инкрементироваться. Аналогичная ситуация имеет место и во втором (рабочем) режиме функционирования модема, в котором осуществляется слежение за оптимальным положением посимвольной синхронизации. Отличие от 1-го режима здесь состоит лишь в том, что число тестируемых положений может быть уменьшено с S вариантов до ±Nгр вокруг номинального (определенного в 1 цикле и в процессе предыдущего слежения).

Задачу формирования начальных адресов считываемых партий отсчетов в прототипе выполняет блок 28 фиг.1 формирования начального адреса при тестировании символьной синхронизации, алгоритм работы которого представлен на фиг.15. Алгоритм запускается при включении модема. В алгоритме показано «начало» и отсутствует «конец», поскольку его выполнение прекращается лишь с выключением модема. На вход 1 блока 28 фиг.1 с первого выхода блока управления 16 подается сигнал, показанный на строке г временной диаграммы фиг.2, который равен 1 в течение длительности 1-го режима и 0 - в течение 2-го.

Таким образом, левая часть алгоритма фиг.15 иллюстрирует функционирование блока 28 формирования начального адреса при тестировании символьной синхронизации в режиме вхождения в связь, а правая - в рабочем режиме. На второй вход блока 28 с третьего выхода БОЧ 10 (фиг.1) подаются короткие единичные импульсы с частотой ƒS (частотой следования OFDM-символов), показанные на строке в временной диаграммы (фиг.2). Появление каждого импульса на втором входе блока 28 фиг.1 соответствует началу очередного цикла тестирования положения посимвольной синхронизации, осуществляемого в течение длительности OFDM-символа при положительном результате проверки условия Вх.2=1. При отрицательном результате этого анализа (Вх.2=0) с помощью блока 1 алгоритма (фиг.15) «NOP» или «нет операции» производится ожидание прихода очередного единичного импульса на втором входе блока 28. При этом в блоке 2 алгоритма фиг.15 обнуляется значение переменной СА (счетчик адреса), затем анализируется сигнал, поступающий на третий вход блока 28 с второго выхода БОЧ (строка б временной диаграммы фиг.2). Этот сигнал представляет собой последовательность двухуровневых прямоугольных импульсов типа меандр (то есть со скважностью равной 2). Частота следования этих импульсов ƒвх3 незначительно превышает ƒd:ƒвх3=1,3 ƒd, что позволяет за время, меньшее длительности OFDM-символа Тc=S/ƒd, выполнять S тестирований.

В зависимости от того, какой из полупериодов описанного сигнала присутствует в данный момент на третьем входе блока 28 фиг.1 (в одном из полупериодов Вх.3=0, в другом - Вх.3=1), выполняется блок 3 или 4 алгоритма фиг.15. В каждом из этих блоков на первый выход блока 28 фиг.1 выдается значение начального адреса для тестирования в соответствии с правилом, иллюстрируемым фиг.5. Кроме того, вспомогательной переменной РОМ в каждом из блоков 3, 4 алгоритма фиг.15 присваивается значение, равное значению сигнала на Вх3. Это необходимо для того, чтобы с помощью последующего условного перехода (РОМ-Вх3=0) обеспечить ожидание момента смены сигналом на Вх.3 своего значения и сохранить неизменным в течение полупериода сигнала Вх3 начальное значение адреса на выходе. Процедура ожидания реализуется с помощью блока 5 алгоритма фиг.15. Далее в алгоритме осуществляется инкрементирование переменной СА и производится проверка количества тестирований. Если оно меньше предусмотренного числа тестов на данной посылке OFDM-символа Nпс=S, то вновь анализируется состояние Вх.3 и цикл повторяется. По окончании тестирования на очередном OFDM-символе (СА=-Nпс), вновь осуществляется проверка состояния сигнала на Вх1. По окончании первого цикла начинается второй, на Вх1 появляется «0» и работает правая часть алгоритма фиг.15. Напомним, что во втором цикле задачей блока 28 фиг.1 является формирование начальных адресов кадров из N отсчетов, извлекаемых из блока 13 фиг.1 в процессе тестирования положений посимвольной синхронизации, осуществляемого в рамках слежения за изменением параметров радиоканала в рабочем режиме. При этом первоначально осуществляется анализ состояния четвертого входа блока 28 фиг.1, на который с третьего выхода БУ 16 подается сигнал, изображенный на строке з временной диаграммы фиг.2 и представляющий собой короткие единичные импульсы, соответствующие началам допустимого интервала тестирования положений посимвольной синхронизации в рабочем режиме (строка ж временной диаграммы, фиг.2). Этот интервал во 2-м режиме начинается спустя время Δt после прихода очередного импульса с частотой ƒS и заканчивается на Δt раньше прихода последующего импульса ƒS. Блок 7 алгоритма «NOP» (фиг.15) используется для ожидания прихода очередного единичного импульса на вход 4 блока 28 фиг.1. Далее работа правой части алгоритма фиг.15 осуществляется аналогично его левой части, с той лишь разницей, что в блоке 8 алгоритма переменной СА присваивается значение:

а для подсчета числа тестирований вводится дополнительная переменная СТ, инициализируемая в том же блоке 8 фиг.14 нулевым значением. На вход 5 блока 28 фиг.1 под