Многоканальный цифровой интегратор

Иллюстрации

Показать всеРеферат

! >сбооюнад патент о-, .. „,л

А Н

О Il И Е 246159

Союз Советских

Социалистических

Республик

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 09 Ч111.1967 (№ 1178251/26-24) с присоединением заявки №

Приоритет

Опубликовано 11.Ч1.1969. Бюллетень № 20

Дата опубликования описания 31.Х.1969

Кл. 42птз, 15 36

42d, 10

Комитет по делам изобретений и открытий при Совете Министров

СССР

МПК б 06f

G Old

УДК 681.335.7(088.8) Автор изобретения

P. Г. Офенгенден

Институт физики АН Украинской CCP

Заявитель

МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР

Известны многоканальные цифровые интеграторы, содержащие преобразователь аналог — код, запоминающее устройство, счетчик кодовых импульсов, счетчик текущего времени, схемы сравнения, блок управления чтением и записью и сумматор.

Предлагаемый интегратор отличается тем, что в нем запоминающее устройство содержит несколько разной емкости групп динамических регистров, причем входы динамических регистров группы с наименьшей емкостью подключены через вентили, управляющие входы которых подсоединены к выходу схемы сравнения младших разрядов счетчика кодовых импульсов и счетчика текущего времени, к выходу регистра преобразователя аналог— код, выходы динамических регистров группы с наименьшей емкостью соединены через вентили, управляющие входы которых подключены к выходу схемы сравнения средних разрядов счетчика кодовых импульсов и счетчика текущего времени, со входами динамических регистров группы с емкостью, большей предыдущей группы динамических регистров, а выходы динамических регистров группы с наибольшей емкостью подсоединены через вентили, управляющие входы которых подключены к выходу схемы сравнения старших разрядов счетчика кодовых импульсов и счетчика текущего времени, ко входу сумматора, соединенного с блоком управления чтением и записью.

Такое выполнение устройства позволяет осуществлять фильтрацию сигналов с высоким быстродействием, большим объемом накопляемой информации при относительно несложной реализации устройства.

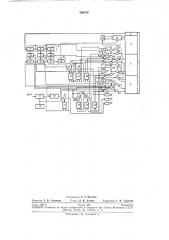

На чертеже представлена блок-схема описываемого многоканального цифрового интег10 р атор а.

Запоминающим устройством интегратора является магнитный барабан 1 или магнитный диск. Магнитный барабан имеет поле 2 для записи синхроимпульсов, информационное поле 8 для хранения в статическом состоянии накопленной информации, поля 4 и 5 для временного хранения данных в группах динамических регистров, при этом емкость динамических регистров поля 4 в целое число раз

20 меньше емкости динамических регистров поля 5. На поле 2 записаны кодовые импульсы, которые делят окружность барабана на и равных участков (в каждом участке на любой дорожке может храниться одно число). Кодовые импульсы непрерывно воспроизводятся и поступают на счетчик б кодовых импульсов, который разбит на три части 7 — 9 (младшие, средние и старшие разряды соответственно).

Интегратор имеет схему 10 дискретных

30 участков времени, с помощью которой выра246159 батываются через заданные периоды времени импульсы квантования по уровню. С помощью этих импульсов измерение непрерывной функции сводится к измерению амплитуд дискретных сигналов. Входная информация поступает на преобразователь 11 аналог — код, в котором непрерывная функция преобразуется в дискретную и каждая амплитуда импульса преобразуется в пропорциональный код, который регистрируется на регистре 12.

В преобразователе 11 после окончания преобразования очередного импульса вырабатывается сигнал окончания преобразования, который фазируется с ближайшим кодовым импульсом и устанавливает триггер 13 в единичное состояние.

Интегратор имеет счетчик 14 текущего времени, который разделен на четыре части.

В первой части 15 фиксируется количество чисел, хранимых в одном из динамических регистров емкостью d поля 4, во второй части

16 — число групп чисел по d, хранимых в одном из динамических регистров емкостью р поля 5, в третьей части 17 — текущий адрес по окружности барабана, по которому необходимо хранимую в поле 5 инфермацию переписывать в информационное поле 8. B четвертои части 18 хранится номер дорожки, на которую указанная выше информация должна быть переписана. Запись информации в поле 4 управляется с помощью триггеров 19 и 20, логических схем «И» 21 — 24 и схемы сравнения 25 младших разрядов. Чтение информации с поля 4 управляется с помощью триггеров 20 и 26, логических схем «И» 27 — 80 и схемы сравнения 31 средних разрядов. Схемами «ИЛИ» 82 и «И» 88 вырабатывается импульс окончания записи в поле 4, схемами

«ИЛИ» 84 и «И» 85 и 86 вырабатываются импульсы окончания чтения с поля 4. Запись в поле 5 управляется триггерами 87- и 88, схемами «И» 89 и 40 и схемой «ИЛИ» 41.

Чтение информации с поля 5 управляется триггерами 88 и 42, схемами «И» 48 — 46, схемой «ИЛИ» 47 и схемой сравнения 48 старших разрядов. Схемами «И» 49 и 50 и схемой «ИЛИ» 51 вырабатываются импульсы окончания чтения с поля 5. Информация, воспроизведенная с поля 5, поступает на один вход сумматора 52. На второй вход сумматора через блок 58 управления чтением и записью поступает накопленная ранее информация на дорожке, номер которой и место на ней определяются четвертой и третьей частями 18 и 17 счетчика 14 текущего времени.

Выходные сигналы с сумматора 52 поступают через блок 58 на поле 8.

Для контроля правильной работы интегратора имеются счетчики 54 — 56. Импульсы квантования со схемы 10 одновременно поступают на схему «И» 57, и если импульс проходит на вход этой схемы, то интегратор работает неправильно. Аналогичное назначение имеют схемы «И» 58, 59. Схемы «И» 60, 61 и 62, 68 предназначены соответственно для

15 гю

65 управления триггерами 19, 20, 26 и 87, 88, 42.

С помощью схемы «И» 64 создаются импульсы сдвига, поступающие на регистр 12.

Прохождение сигналов в интеграторе ос ществляется следующим образом.

Входная информация поступает на вход преобразователя 11. Схема дискретных участков времени вырабатывает импульсы квантования, которые поступают также на преобразователь 1(. В результате образуются импульсы, амплитудные значения которых пропорциональны мгновенным значениям входного сигнала. Каждый из этих импульсов преобразуется в серию высокочастотных импульсов, число которых пропорционально амплитуде импульса. Эта серия импульсов поступает на регистр 12. Ближайший кодовый импульс после окончания каждой серии поступает на триггер 18 и устанавливает его в единичное состояние. Это является критерием того, что на регистре 12 имеется информация. Эта информация должна быть переписана на один из динамических регистров поля 4.

В предлагаемом интеграторе на полях 4 и 5 имеется по два динамических регистра. На одном из свободных динамических регистров емкостью d поля 4 записываются d последовательно поступивших с регистра 12 чисел.

После этого накопление производится в другом динамическом регистре емкостью d до его заполнения, затем обратно в первый регистр. При этом соотношения между емкостями динамических регистров поля 4 и поля 5 выбираются таким образом, что в течение времени заполнения одного регистра емкостью d с другого регистра информация обязательно переписывается в поле 5. Вместо двух регистров каждого поля можно применять по одному регистру, однако при этом необходимо иметь дополнительные счетчики, в которых фиксировалось бы состояние каждого из регистров. Выбор одного из динамических регистров поля 4 осуществляется с помощью триггеров 19 и 20 и схем «И» 21 — 24.

Место, на котором записывается информация с регистра 12, определяется частями 7 и 15 счетчиков и схемой сравнения 25 младших разрядов. Для нормальной работы интегратора частота квантованных импульсов не

1 должна превышать —, где „вЂ” время цирсД куляции импульса в динамическом регистре поля 4. После переписи информации с регистра 12 через схему «И» 38 проходит ближайший кодовый импульс k на счетчик 14 и одновременно устанавливает триггер 13 в нулевое состояние. Устройство готово к принятию очередного импульса.

После заполнения динамического регистра поля 4 с выхода младших разрядов счетчика

14 поступает импульс, который устанавливает триггеры 19 и 26 в единичное состояние, если перед этим триггер 19 был в нулевом состоя246159 нии. Если он был в единичном состоянии, то импульсом с выхода младших разрядов счетчика 14 в единичное состояние устанавливается триггер 20, а в нулевое — триггер 19.

Единичное состояние триггеров 2б и 20 является критерием того, что в соответствующем динамическом регистре поля 4 накоплено чисел. Перепись этой информации в поле 5 осуществляется при выдаче сигнала со схемы сравнения 81. При этом в зависимости от состояния триггеров 87 и 88 перепись производится в соответствующий динамический регистр. После окончания указанной переписи трипер 20 или 2б устанавливается в нулевое состояние. После заполнения одного из динамических регистров поля 5 с выхода средних разрядов счетчика 14 поступает импульс для фиксации на триггерах 87, 42 или 88 указанного заполнения. Перепись с поля 5 в информационное поле 8 осуществляется при выдаче со схемы сравнения 48 сигнала равенства адресов на старших разрядах счетчиков б и

14. При этом по адресу, установленному в частях 17 и 18 счетчика 14, выбирается с поля 8 информация, к которой добавляется с помощью сумматора 52 считываемая с поля 5 информация, и результат через блок 58 управления чтением и записью записывается в поле 8.

В описываемом интеграторе предусмотрена возможность одновременно с накоплением информации осуществлять визуализацию накопленной информации.

Предмет изобретения

Многоканальный цифровой интегратор, содержащий преобразователь аналог — код, за5 поминающее устройство, счетчик кодовых импульсов, счетчик текущего времени, схемы сравнения, блок управления чтением и записью и сумматор, отличающийся тем, что, с целью повышения его быстродействия, в

10 нем запоминающее устройство содержит несколько разной емкости групп динамических регистров, причем входы динамических регистров группы с наименьшей емкостью подключены через вентили, управляющие входы

15 которых подсоединены к выходу схемы сравнения младших разрядов счетчика кодовых импульсов и счетчика текущего времени, к выходу регистра преобразователя аналог — код, выходы динамических регистров группы с

20 наименьшей емкостью соединены через вентили, управляющие входы которых подключены к выходу схемы сравнения средних разрядов счетчика кодовых импульсов и счетчика текущего времени, со входами динамических регистров группы с емкостью, большей предыдущей группы динамических регистров, а выходы динамических регистров группы с наибольшей емкостью подсоединены через вентили, управляющие входы которых подрр ключены к выходу схемы сравнения старших разрядов счетчика кодовых импульсов и счетчика текущего времени, ко входу сумматора, соединенного с блоком управления чтением и записью.

246159

Составитель А. А, Плащин

Редактор Е. В. Семанова Техрсд Л. Я. Левина Корректор Г, И. Тарасова

Заказ 2761/6 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2