Способ и устройство трансляции адреса

Иллюстрации

Показать всеИзобретение относится к трансляции адреса, и в частности относится к трансляции виртуальных адресов, которые создают условия пересечения границы страницы памяти. Технический результат - осуществление доступа к данным в процессе, при исключении выполнения множества трансляций виртуальных адресов в процессоре. Трансляция адреса, которая выполняется внутри процессора, улучшена идентификацией адреса, который вызывает пересечение границы между различными страницами в памяти и связывание информации трансляции адреса, ассоциированной с обеими страницами памяти. В соответствии с одним вариантом осуществления процессора, процессор содержит схему, выполненную с возможностью распознавания доступа к зоне памяти, пересекающей границу страницы между первой и второй страницами памяти. Схема также выполнена с возможностью связывания информации трансляции адреса, ассоциированной с первой и второй страницами памяти. Таким образом, в ответ на последующий доступ к такой же зоне памяти, информация трансляции адреса, ассоциированная с первой и второй страницами памяти, извлекается, основываясь на единичной трансляции адреса. 4 н. и 17 з.п. ф-лы, 5 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к трансляции адреса, и в частности относится к трансляции виртуальных адресов, которые создают условия пересечения границы страницы памяти.

Уровень техники

Виртуальная память - это методика управления памятью, посредством которой возможно фрагментированную физическую память (физическое адресное пространство) представить процессу (программному обеспечению) как непрерывную память (виртуальное адресное пространство). Даже если размещенная физическая память не всегда последовательно организована (или даже в одинаковых носителях, на пример SDRAM и ROM), процессы видят память как линейную последовательность, потому что они имеют дело с непрерывным виртуальным адресным пространством. Более того, программы обычно не знают, как размещена физическая память. Взамен процессор или другое устройство условно управляет размещением виртуальной памяти.

Управление памятью разделяет физическую память на страницы (или сегменты) и обеспечивает отображение виртуальных адресов на фактические страницы физической памяти, которые прозрачны для процессов, осуществляющих доступ к памяти. Процессы видят только виртуальное адресное пространство, в то время как физическое адресное пространство является местом, где соответствующие данные фактически постоянно находятся в памяти. Процессор условно отображает виртуальное адресное пространство на физическое адресное пространство, используя трансляцию адреса. Трансляция адреса затрагивает поиск физического адреса на основе данного виртуального адреса. Виртуальный адрес условно разделен на, по меньшей мере, две части - номер виртуальной страницы и смещение страницы. Номер виртуальной страницы идентифицирует конкретную страницу виртуальной памяти. Смещение страницы идентифицирует требуемую зону (или блок) внутри страницы.

Таблица страниц, поддерживаемая в основной памяти, обычно хранит список номеров виртуальных страниц и соответствующих номеров физических страниц. Таблица страниц просматривается, используя часть виртуального адреса номера виртуальной страницы. Если номер виртуальной страницы совпадает с элементом таблицы страниц, соответствующий номер физической страницы извлекается из таблицы. В противном случае, имеет место ошибка таблицы страниц. Извлеченный номер физической страницы, наряду со смещением страницы, формирует физический адрес, используемый для извлечения информации из памяти. Номер страницы идентифицирует правильную страницу физической памяти. К требуемой зоне памяти в странице затем осуществляется доступ, используя смещение страницы.

Для улучшения производительности часто запрашиваемые элементы таблицы страниц локально сохраняются в процессоре, например в буфере ассоциативной трансляции (TLB). TLB может поддерживать единственный уровень локальной кэш-памяти или множественные кэш-уровни, например кэши данных и команд первого уровня и кэш второго уровня. Так или иначе, TLB выполняет трансляцию адреса почти тем же способом, как делает таблица страниц. Если возникает совпадение во время просмотра TLB, используя номер виртуальной страницы, соответствующий номер физической страницы извлекается из TLB и предоставляется вместе со смещением страницы в физически меченый кэш. Если физический адрес попадает в кэш, строка кэша, соответствующая физическому адресу, извлекается из кэша. В противном случае, может иметь место просмотр кэша более высоко уровня.

Виртуальная память позволяет исполнять программы, не требуя того, чтобы их полное адресное пространство постоянно находилось в физической памяти. Таким образом, программа может быть исполнена, используя меньше физической памяти, чем фактически необходимо. Вдобавок, виртуальная память изолирует программы одну от другой, потому что каждое виртуальное адресное пространство программы может быть независимо отображено на одной или более страницах физической памяти, размещенных исключительно для той программы. Также прикладные программы упрощаются, потому что они не ответственны за управление памятью. Однако определенные типы доступа памяти требуют дополнительной обработки трансляции адреса для успешного завершения.

Например, когда возникает смещенный доступ к памяти, требуемое слово находится частично в одной строке и частично в другой. Если две строки размещаются в различных страницах памяти, возникает пересечение границы страницы. Команда, которая относится к зоне памяти, пересекающей границу между двух страниц памяти, условно дублируется и исполняется в двух частях. Часть первой страницы дублированной команды завершает исполнение, основываясь на физическом адресе, ассоциированном с первой страницей памяти, и часть второй страницы дублированной команды завершает исполнение, основываясь на адресе, ассоциированном со второй страницей памяти. Таким образом, к различным страницам памяти осуществляется доступ отдельно посредством дублирования команды.

Множественные трансляции адреса обычно требуются для получения адресов физической памяти, ассоциированных с различными страницами памяти. Первая трансляция адреса выполняется для извлечения физического адреса, ассоциированного с первой страницей памяти, и вторая трансляция адреса выполняется для извлечения физического адреса, ассоциированного со второй страницей памяти. Дополнительная обработка трансляции адреса, требуемая для команды, которая создает условия пересечения границы, уменьшает производительность процессора и увеличивает затраты мощности, особенно если необходим доступ к таблице страниц, обслуживающейся в основной памяти.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В соответствии со способами и устройством, раскрываемыми в данном документе, выполнение трансляции адреса внутри процессора улучшено идентификацией виртуальных и физических адресов, которые вызывают пересечение границ между различными страницами в памяти. То есть команда идентифицируется в случае, если она вызовет смещенный доступ к памяти, который также пересекает границу страницы. Когда такое условие распознается, информация трансляции адреса, ассоциированная с обеими страницами в памяти, связывается вместе воедино и сохраняется в процессоре. Информация трансляции адреса, ассоциированного с обеими страницами, может быть получена, используя единственную трансляцию адреса, отвечающую за такую же зону пересечения страницы в памяти, к которой впоследствии осуществляют доступ. Таким образом, избегают множественных трансляций адреса.

В соответствии с одним вариантом осуществления процессора, процессор содержит схему, выполненную с возможностью распознавать доступ к зоне памяти, пересекающей границы страницы между первой и второй страницами памяти. Схема также выполнена с возможностью связывать информацию трансляции адреса, ассоциированную с первой и второй страницами памяти. Таким образом, отвечающая за последующее обращение к той же зоне памяти, информация трансляции адреса, ассоциированная с первой и второй страницами памяти, извлекается, основываясь на единственной трансляции адреса.

Когда впоследствии к такой же зоне в памяти осуществляется доступ, схема процессора распознает соответствующую команду и транслирует виртуальный адрес, представленный командой, в физический адрес, ассоциированный с первой страницей памяти. Схема извлекает физический адрес, ассоциированный со второй страницей памяти, основываясь на ранее установленной информации, связывающей виртуальный адрес с физическим адресом, ассоциированным со второй страницей памяти. Таким образом, информация трансляции адреса, ассоциированная с первой и второй страницами памяти, извлекается, основываясь на единственной трансляции адреса.

Конечно, настоящее изобретение не ограничено вышеуказанными признаками и преимуществами. Специалистам в данной области техники будут понятны дополнительные признаки и преимущества после прочтения следующего подробного описания и просмотра сопроводительных чертежей.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

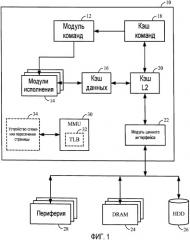

Фиг.1 представляет собой блок-схему, иллюстрирующую вариант осуществления процессора, имеющего схему для отслеживания пересечений границы страницы, во время трансляции адреса.

Фиг.2 представляет собой блок-схему, иллюстрирующую вариант осуществления схемы отслеживания пересечения страницы фиг.1.

Фиг.3 представляет собой логическую схему последовательности действий, иллюстрирующую вариант осуществления программной логики для хранения информации трансляции адреса в схеме отслеживания пересечения страниц фиг.1.

Фиг.4 представляет собой логическую схему последовательности действий, иллюстрирующую вариант осуществления программной логики для извлечения информации трансляции адреса из схемы отслеживания пересечения страницы фиг.1.

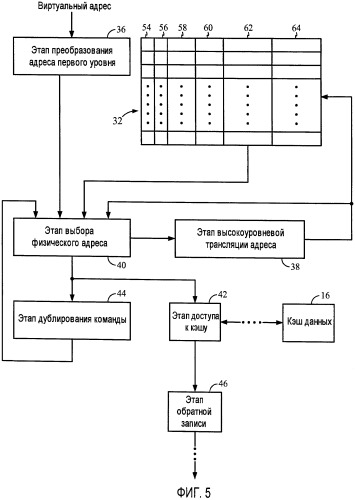

Фиг.5 представляет собой блок-схему, иллюстрирующую другой вариант осуществления схемы отслеживания пересечения страницы фиг.1.

ПОДРОБНОЕ ОПИСАНИЕ

Фиг.1 иллюстрирует вариант осуществления процессора 10, включающего в себя модуль 12 команд, модуль 14 исполнения, кэши 16 и 18 данных и команд, кэш 20 второго уровня и модуль 22 шинного интерфейса. Модуль 12 команд обеспечивает централизованное управление потоком команд в модуль 14 исполнения. Модуль 14 исполнения исполняет команды, отправленные модулем 12 команд, включающим в себя загрузку и сохранение информации в кэше 16 данных. Кэши 16 и 18 данных и команд хранят данные и команды, соответственно. Кэш 20 второго уровня обеспечивает высокоскоростной буфер памяти между кэшами 16 и 18 данных и команд и основной памятью, внешней к процессору, такой как DRAM 24 и/или одним или более жестким диском (HDD) 26. Модуль 22 шинного интерфейса обеспечивает механизм передачи данных, команд, адресов и сигналов управления между процессором 10 и устройствами, внешними к процессору, такими как периферия 28 и основная память.

Основная память представлена как виртуальная память в процессах, запущенных на процессоре 10. То есть страницы основной памяти размещаются как виртуальная память для пользования процессами во время исполнения программы. Управление памятью разделяет физическую память на страницы и обеспечивает отображение виртуальных адресов на страницы физической памяти, то есть прозрачно для процессов, осуществляющих доступ к памяти. Таблица страниц (не показана) обслуживается в основной памяти, чтобы сделать возможным отображение между адресами виртуальной и физической памяти. Модуль управления памятью (MMU) 30 или подобное устройство, входящее в состав процессора 10, обслуживает часто или недавно запрашиваемые элементы таблицы страниц, размещенные в процессоре 10 для улучшения выполнения трансляции адреса.

Остается добавить, что буфер ассоциативной трансляции (TLB) 32, входящий в состав или ассоциированный с MMU 30, хранит элементы таблицы страниц, к которым наиболее часто или недавно осуществлялся доступ. Трансляция адреса выполняется локально внутри процессора 10 посредством TLB. Если элемент TLB совпадает с данным номером виртуальной страницы, соответствующий номер физической страницы предоставляется TLB 32. Иначе выполняется высокоуровневая трансляция адреса, обычно программным обеспечением операционной системы, через таблицу страниц, обслуживаемую в основной памяти. Устройство 34 слежения пересечения страниц, входящее в состав или ассоциированное с MMU 30, улучшает выполнение трансляции адреса посредством уменьшения количества трансляций адреса, выполняемых для подгонки смещенного доступа к памяти, который пересекает границу страницы памяти.

Устройство 34 слежения пересечения страниц хранит информацию трансляции адреса, ассоциированную с одним или более виртуальными или физическими адресами, которые создают условие пересечения границы страницы. То есть если команда, исполняемая процессором 10, ссылается на зону памяти, пересекающую границу между двумя страницами физической памяти, то устройство 34 слежения пересечения страниц хранит информацию трансляции адреса, ассоциированную со второй страницей памяти, например физический адрес или номер страницы, идентифицирующий вторую страницу памяти, и связывает с виртуальным адресом. В этом случае, если последующая команда ссылается на такой же адрес, то устройство 34 слежения пересечения страницы может распознать адрес и предоставить соответствующую информацию о физическом адресе. Соответственно, TLB 32 выполняет только одну трансляцию адреса для извлечения номера физической страницы, ассоциированного с первой страницей памяти. Номер физической страницы, ассоциированный со второй страницей памяти, извлекается без трансляции из устройства 34 слежения пересечения страниц. То есть номер физической страницы, ассоциированный со второй страницей памяти, извлекается из устройства 34 слежения пересечения страниц вместо необходимости выполнения второго преобразования адреса. Команда дублируется и исполняется в двух частях, основываясь на соответствующих физических адресах. Команда может дублироваться множество раз, если команда вызывает пресечение нескольких строк кэша в одном из кэшей 16, 18, 22.

Фиг.2 иллюстрирует один способ осуществления устройства 34 слежения пересечения страниц и несколько этапов модуля загрузки-сохранения (то есть один из исполнительных модулей 14), входящий в состав процессора 10. В соответствии со способом осуществления, устройство 34 слежения пересечения страниц содержит регистр для сохранения информации трансляции адреса, ассоциированной с адресом, который создает условие пересечения границы страницы. В качестве альтернативы, устройство слежения пересечения границы может быть таблицей, имеющей множество элементов. В любом случае устройство 34 слежения пересечения страницы уменьшает обработку трансляции адреса посредством хранения информации трансляции адреса, ассоциированной с по меньшей мере одним виртуальным или физическим адресом, который вызывает пересечение границы страницы.

Работа устройства 34 слежения пересечения страницы в дальнейшем описывается, ссылаясь на программную логику фиг.3, и виртуальным адресом, представленным командой, который первоначально не совпадал ни с каким элементом из TLB 32. По существу, высокоуровневая трансляция адреса выполняется для получения физического адреса, соответствующего виртуальному адресу. Более детально, виртуальный адрес может содержать номер виртуальной страницы и смещение. Номер виртуальной страницы идентифицирует отдельную страницу памяти, в то время как смещение страницы идентифицирует положение внутри страницы. Так как не имеющий совпадения в TLB элемент первоначально существует в этом примере, этап 36 трансляции адреса первого уровня указывает необходимость высокоуровневой трансляции адреса, например, как проиллюстрировано блоком 100 фиг.3. Этап 38 высокоуровневой трансляции адреса требует трансляции виртуального адреса, например, посредством доступа к более высокоуровневой TLB (не показан), входящего в состав процессора 10 или таблицу страниц, обслуживаемую в основной памяти. В любом случае, в итоге будет получен физический адрес, связанный с виртуальным адресом.

Информация трансляции адреса хранится в элементе TLB, например, как проиллюстрировано блоком 102 фиг.3. В этом случае информация трансляции адреса более легкодоступна, в случае если такой же виртуальный адрес впоследствии запрошен. В одном варианте осуществления этап 40 выбора физического адреса, такой как схема мультиплексора или любой другой этап, в котором известен виртуальный адрес, также определяет, транслируется ли виртуальный адрес в физическую зону памяти, которая пересекает границу между двух страниц, например, как проиллюстрировано блоком 104 фиг.3. Например, часть смещения страницы виртуального адреса сравнивается с установочными параметрами размера страницы памяти, чтобы определить, возникнет ли пересечение границы страницы. Если адрес транслируется в зону памяти, расположенную внутри единственной страницы памяти, то исполнение инструкции завершается, основываясь на преобразованном физическом адресе, например, как проиллюстрировано блоком 106 фиг.3. Например, этап 42 доступа к кэшу определяет, содержит ли кэш 16 данных или кэш 20 L2 строку, помеченную физическим адресом, и если нет, то он извлекает ее из внешней памяти.

Однако если виртуальный адрес ссылается на зону памяти, охватывающую множество страниц памяти, этап 44 дублирования команды дублирует команду, например, как проиллюстрировано блоком 108 фиг.3. Например, если адрес ссылается на четверное слово, имеющее четыре байта, расположенных в одной странице физической памяти, и четыре байта, расположенных на другой странице, то ранее транслированный физический адрес используется для извлечения четырех байтов, постоянно находящихся в первой странице памяти. Для извлечения четырех байтов, расположенных во второй странице памяти, физический адрес, идентифицирующий вторую страницу, получают на этапе 38 высокоуровневой трансляции адреса, например, как проиллюстрировано блоком 110 фиг.3. Часть первой страницы дублированной команды завершает исполнение, основываясь на физическом адресе, идентифицирующем первую страницу памяти, например, как проиллюстрировано блоком 112 фиг.3. Часть второй страницы дублированной команды завершает исполнение, основываясь на физическом адресе, идентифицирующем вторую страницу памяти, например, как проиллюстрировано блоком 114 фиг.3. Этап 46 обратной записи гарантирует правильное хранение результатов исполнения команды.

Так как пересечение границы страницы обнаружено, то информация трансляции адреса, полученная для второй страницы памяти, хранится для последующего использования. Однако вместо хранения информации в различных элементах TLB, она хранится в поле 48 физического адреса устройства 34 слежения пересечения страницы, например, как проиллюстрировано блоком 116 фиг.3. Значение указателя хранится в поле 50 указателя. Значение указателя связывает элемент в устройстве слежения пересечения границы, содержащий информацию трансляции адреса второй страницы с элементом TLB, содержащим информацию трансляции адреса первой страницы.

В одном варианте осуществления поле 50 указателя хранит значение индекса элемента TLB, содержащего информацию трансляции адреса, ассоциированную с первой страницей памяти. В другом варианте осуществления поле 50 указателя хранит физический адрес или номер страницы, ассоциированный с первой страницей памяти. В еще одном варианте осуществления поле 50 указателя хранит виртуальный адрес, который создает условие пересечения границы. Специалисты в данной области техники легко признают, что широкое множество значений может храниться в поле 50 указателя для того, чтобы связать информацию 48 физического адреса с элементом TLB, ассоциированным с первой страницей памяти. Более того, этап 44 дублирования команды может идентифицировать пересечение границы страницы вместо этапа 40 выбора физического адреса, например, идентифицируя физические адреса, которые вызывают пересечения границ страницы. Безотносительно, если к такой же зоне памяти впоследствии осуществляется доступ, устройство 34 слежения пересечения страниц распознает условие пересечения границы, проверяя поле 50 указателя. В ответ устройство 34 слежения предоставляет информацию трансляции адреса, ассоциированную со второй страницей.

Работа устройства 34 слежения пересечения страниц описана ниже со ссылкой на программную логику фиг.4 и последующей командой, которая представляет такой же виртуальный адрес, который вызвал условие пересечения границы, ранее рассмотренное. Так как TLB 32 содержит элемент совпадения в этом примере, то физический адрес или номер страницы, ассоциированный с виртуальным адресом, предоставляется посредством TLB 32, например, как проиллюстрировано блоком 200 фиг.4. Этап 40 выбора физического адреса определяет, ссылается ли виртуальный адрес на зону в памяти, которая пересекает границу страницы, например, как проиллюстрировано блоком 202 фиг.4. В качестве альтернативы, этап 44 дублирования команды определяет, вызывает ли соответствующий физический адрес условие пересечения границы страницы. Безотносительно, если условие пересечения границы не обнаружено, команда завершает исполнение, основанное на информации физического адреса, предоставленного TLB 32, например, как проиллюстрировано блоком 204 фиг.4.

Однако в настоящем примере известно, что виртуальный адрес вызывает пересечение границы страницы между первой и второй страницами памяти. Таким образом, команда дублируется, как и ранее описано, например, как проиллюстрировано блоком 206 фиг.4. Более того, проверяется поле 50 указателя устройства 34 слежения пересечения страницы для определения, сформирована ли связь с виртуальным адресом. В одном варианте осуществления индекс элемента TLB совпадения сравнивается с одним или более значениями, хранящимися в поле 50 указателя. В другом варианте осуществления виртуальный адрес или соответствующий физический адрес (или номер страницы), предоставленный посредством TLB 32, сравнивается с одним или более значениями адресов, хранящимися в поле 50 указателя.

Безотносительно, информация, хранящаяся в поле 50 указателя, указывает, содержит ли устройство 34 слежения требуемую информацию физического адреса. Пока поле 52 действительности не указывает, что элемент недействительный, информация о физическом адресе, ассоциированная со второй страницей, извлекается из устройства 34 слежения пересечения страницы, например, как проиллюстрировано блоком 208 фиг.4. Поле 52 действительности указывает недействительность, когда соответствующий элемент в TLB объявлен недействительным.

Часть первой страницы дублированной команды завершает исполнение, основанное на физическом адресе, идентифицирующем первую страницу памяти, как предоставленным TLB 32, например, как проиллюстрировано блоком 210 фиг.4. Часть второй страницы дублированной команды завершает исполнение, основываясь на физическом адресе, идентифицирующем вторую страницу памяти, как извлеченную из устройства 34 слежения пересечения страницы, например, как проиллюстрированным блоком 212 фиг.4. Схема (не показана) предотвращает возникновение последующей трансляции адреса в случае, когда устройство 34 слежения пересечения страницы содержит информацию трансляции адреса для второй страницы. Таким образом, выполняется только единственная трансляция адреса, когда устройство 34 слежения пересечения страницы распознает условие пересечения границы страницы.

Фиг.5 иллюстрирует другой вариант осуществления устройства 34 слежения пересечения страницы. В соответствии с эти вариантом осуществления устройство 34 слежения реализуется как часть TLB 32. Каждый элемент TLB 32 имеет поле 54 действительности, поле 56 указателя, индекс 58, поле 60 метки и два поля физических адресов 62 и 64. Поле 60 метки хранит виртуальный адрес (или номер страницы) тех виртуальных адресов, чья информация физического адреса обслуживается TLB 32. По существу, поле 60 метки перебирается в течение выборки TLB для определения, хранится ли в TLB 32 запись, совпадающая с данным виртуальным адресом.

Первое поле 62 физического адреса содержит информацию физического адреса, такую как полный адрес или номер физической страницы, соответствующий каждому виртуальному адресу, имеющему запись, обслуживаемую TLB 32. Если известно, что конкретный виртуальный адрес вызывает пересечение границы между двумя страницами памяти, то второе поле 64 физического адреса содержит информацию физического адреса, ассоциированную со второй страницей памяти. Поле 56 указателя содержит один или более битов, связывающих два поля 62 и 64 физических адресов, в то время как соответствующий элемент TLB ассоциирован с виртуальным адресом, который создает условие пересечения границы.

Работа устройства 34 слежения пересечения страницы, реализованная как часть TLB 32, ниже описана со ссылкой на виртуальный адрес, представленный командой, который первоначально не совпадает ни с каким элементом из TLB 32. Высокоуровневая трансляция адреса выполняется для получения физического адреса, соответствующего виртуальному адресу, например, как проиллюстрировано блоком 100 фиг.3. Поле 62 физического адреса в соответствующем элементе TLB обновляется результатами трансляции, например, как проиллюстрировано блоком 102 фиг.3. Если этап 40 выбора физического адреса определяет то, что виртуальный адрес вызовет пересечение границы между двумя страницами памяти в течении доступа к памяти, то выполняется вторая высокоуровневая трансляция адреса. В качестве альтернативы, этап 44 дублирования команды может обнаружить условие пересечения границы страницы, основываясь на соответствующем физическом адресе. Безотносительно, физический адрес, идентифицирующий вторую страницу памяти, получают в течение второй высокоуровневой трансляции адреса, например, как проиллюстрировано блоком 110 фиг.3. В этом случае информация физического адреса для обеих страниц доступна для завершения исполнения команды.

Команда дублируется, и исполнение завершается, используя два адреса физической памяти, как ранее описано, например, как проиллюстрировано блоками 108, 112 и 114 фиг.3. В дополнение, информация физического адреса, ассоциированная со второй страницей памяти, хранится в таком же элементе TLB, содержащем информацию физического адреса, ассоциированную с первой страницей, например, как проиллюстрировано блоком 116 фиг.3. То есть в одном и том же элементе TLB информация физического адреса, ассоциированная с первой страницей, хранится в первом поле 62 адреса, а информация физического адреса, ассоциированная со второй страницей, хранится во втором поле 64 адреса. Поле 56 указателя в элементе TLB устанавливается для указания того, что два физических адреса связаны и ассоциированы с виртуальным адресом, который создает условие пересечения границы страницы. В этом случае, если последующая команда ссылается на такой же виртуальный или физический адрес, необходима только единственная трансляция адреса для получения информации физического адреса, ассоциированной с первой и второй страницами памяти.

Работа устройства 34 слежения пересечения страницы, выполненная как часть TLB 32, ниже описана со ссылкой на последующую команду, осуществляющую доступ к такому же виртуальному адресу, который создает условие пересечения границы страницы, которое ранее описано. Когда осуществляется доступ к TLB 32, элемент совпадения идентифицируется сравнением виртуального адреса со значением метки, хранящимся в TLB 32, например, как проиллюстрировано блоком 200 фиг.4. В настоящем примере известно, что виртуальный адрес вызывает пересечение границы страницы между первой и второй страницами памяти. Таким образом, команда дублируется, как ранее описано, например, как проиллюстрировано блоком 206 фиг.4. Более того, поле 62 первого адреса элемента TLB совпадения предоставляет информацию физического адреса, ассоциированную с первой страницей памяти. Исполнение части первой страницы дублированной команды завершается, основываясь на информации физического адреса, полученного из поля 62 первого адреса, например, как проиллюстрировано блоком 210 фиг.4.

В дополнение поле 56 указателя в элементе TLB совпадения указывает, что связаны первое и второе поля 62 и 64 физического адреса. Соответственно информация физического адреса, хранящаяся во втором поле 64 адреса, извлекается, например, как проиллюстрировано блоком 208 фиг.4. Информация физического адреса, извлеченная из второго поля 64 адреса, идентифицирует вторую страницу памяти. Исполнение части второй страницы дублированной команды завершается, основываясь на информации физического адреса, полученной из второго поля 64 адреса, например, как проиллюстрировано блоком 212 фиг.4. В этом случае выполняется только единственная трансляция адреса в течение исполнения последующей команды.

Если поле 54 действительности указывает, что элемент TLB недействителен, то трансляция адреса не выполняется, и этап 38 высокоуровневой трансляции адреса получает необходимые физические адреса, как ранее описано, например, как проиллюстрировано блоками 100 и 110 фиг.3. Более того, поле 56 указателя может также указывать, что связь между двумя страницами памяти недействительна в ответ на сконфигурированный регистр, что повлияет на то, что трансляция адреса будет обновлена или элемент TLB будет перезаписан. Когда встречается недействительное соединение пересечения страницы, информация трансляции адреса, ассоциированная со связанной страницей, не используется. Вместо этого выполняется последующая трансляция адреса.

Принимая во внимание вышеописанные варианты и применения, должно быть понятно, что настоящее изобретение не ограничено вышеупомянутым описанием, так же не ограничено сопроводительными чертежами. Вместо этого настоящее изобретение ограничено только следующей формулой изобретения и ее законными эквивалентами.

1. Способ доступа к данным, осуществляемый в процессоре, содержащий этапы, на которых:получают представление виртуального адреса данных на этапе трансляции адреса первого уровня, причем данные сохраняют в физической памяти, причем данные имеют первую часть данных и вторую часть данных, причем первую часть данных сохраняют в первом физическом адресе на первой странице в физической памяти, причем вторую часть данных сохраняют во втором физическом адресе на второй странице в физической памяти, причем виртуальный адрес данных соответствует первому физическому адресу и второму физическому адресу;извлекают первый физический адрес на этапе трансляции адреса первого уровня;предоставляют первый физический адрес;извлекают второй физический адрес посредством доступа к этапу трансляции адреса второго уровня;предоставляют второй физический адрес;создают связь между вторым физическим адресом и первым физическим адресом;получают второе представление виртуального адреса данных на этапе трансляции адреса первого уровня;извлекают первый физический адрес на этапе трансляции адреса первого уровня; иизвлекают на этапе трансляции адреса первого уровня второй физический адрес из регистра, используя связь между вторым физическим адресом и первым физическим адресом.

2. Способ по п.1, дополнительно содержащий этап, на котором сохраняют информацию трансляции адреса первой части данных в буфере ассоциативной трансляции (TLB), причем информация трансляции адреса включает в себя виртуальный адрес и первый физический адрес.

3. Способ по п.2, дополнительно содержащий этап, на котором сохраняют второй физический адрес в устройстве слежения пересечения страниц, которое может осуществлять доступ к TLB.

4. Способ по п.1, дополнительно содержащий этап, на котором дублируют команду, ассоциированную с виртуальным адресом, посредством извлечения первой части данных и второй части данных.

5. Способ по п.3, в котором этап, на котором создают связь между вторым физическим адресом и первым физическим адресом, содержит этап, на котором ассоциируют информацию трансляции адреса второй части данных с информацией трансляции адреса первой части данных посредством сохранения значения указателя в поле индикатора устройства слежения пересечения страниц, причем поле указателя ассоциировано со второй частью данных.

6. Способ по п.5, в котором значение указателя включает в себя значение индекса элемента TLB, причем элемент TLB включает в себя информацию трансляции адреса первой части данных.

7. Способ по п.5, в котором значение указателя включает в себя первый физический адрес.

8. Способ по п.1, дополнительно содержащий этап, на котором обрывают связь, установленную в ответ на первое представление, причем обрыв связи включает в себя этап, на котором объявляют недействительной информацию, связывающую информацию о физическом адресе, ассоциированную со второй страницей, с информацией о виртуальном адресе, ассоциированной с первой страницей.

9. Способ по п.8, в котором связь обрывают в ответ на перезапись элемента буфера ассоциативной трансляции (TLB).

10. Процессор для доступа к данным, причем процессор выполнен с возможностью:получения первого представления виртуального адреса данных на этапе трансляции адреса первого уровня, причем данные сохранены в физической памяти, причем данные имеют первую часть данных и вторую часть данных, причем первая часть данных сохранена в первом физическом адресе на первой странице в физической памяти, причем вторая часть данных сохранена во втором физическом адресе на второй странице в физической памяти, причем виртуальный адрес данных соответствует первому физическому адресу и второму физическому адресу;извлечения первого физического адреса на этапе трансляции адреса первого уровня;предоставления первого физического адреса;извлечения второго физического адреса посредством доступа к этапу трансляции адреса второго уровня;предоставления второго физического адреса;сохранения второго физического адреса в таблице устройства слежения пересечения страниц; создания связи между вторым физическим адресом и первым физическим адресом;получения второго представления виртуального адреса данных на этапе трансляции адреса первого уровня;извлечения первого физического адреса на этапе трансляции адреса первого уровня; и извлечения на этапе трансляции адреса первого уровня второго физического адреса из таблицы устройства слежения пересечения страниц, используя связь между вторым физическим адресом и первым физическим адресом.

11. Процессор по п.10, причем процессор дополнительно выполнен с возможностью дублирования команды, ассоциированной с виртуальным адресом посредством извлечения первой части данных и второй части данных.

12. Процессор по п.10, причем процессор дополнительно выполнен с возможностью хранения информации о виртуальном адресе и информации о физическом адресе, ассоциированной с первой страницей памяти в элементе буфера ассоциативной трансляции.

13. Процессор по п.12, причем процессор дополнительно выполнен с возможностью хранения информации о физическом адресе, ассоциированной со второй страницей памяти, и информации, идентифицирующей элемент буфера ассоциативной трансляции.

14. Способ выполнения трансляции адреса, осуществляемый в процессоре, содержащий этапы, на которых:определяют, что виртуальный адрес, ассоциированный с командой, соответствует зоне памяти, причем эта зона памяти охватывает границу страницы между первой страницей памяти и второй страницей памяти;транслируют виртуальный адрес в первый физический адрес, ассоциированный с первой страницей памяти; иизвлекают второй физический адрес, ассоциированный со второй страницей памяти на основании ранее установленной информации, связывающей виртуальный адрес со вторым физическим адресом без выполнения второй трансляции адреса.

15. Способ по п.14, дополнительно содержащий этап, на котором дублируют команду, причем дублированная команда завершает исполнение, основываясь на первом физическом адресе и основываясь на втором физическом адресе.

16. Способ по п.14, в котором этап, на котором транслируют виртуальный адрес, содержит этапы, на которых:идентифицируют элемент буфера ассоциативной трансляции (TLB) в TLB, причем элемент TLB соответствует виртуальному адресу; иизвлекают первый физический адрес из элемента TLB.

17. Способ по п.14, в котором извлечение второго физического адреса включает в себя этапы, на которых:определяют, содержит ли первый элемент буфера ассоциативной трансляции (TLB) в TLB указание на связь между первой страницей памяти и второй страницей памяти; иизвлекают второй физический адрес из первого элемента TLB, если первый элемент TLB содержит указание на связь между первой страницей памяти и второй страницей памяти.

18. Процессор для выполнения трансляции адреса, причем процессор выполнен с возможностью:определения, что виртуальный адрес, ассоциированный с командой, соответствует зоне памяти, причем эта зона памяти охватывает границу страницы между первой страницей памяти и второй страницей памяти;т