Система стереотелевидения

Иллюстрации

Показать всеИзобретение относится к технике радиосвязи и может быть использовано дли цифрового телевещания. Техническим результатом является формирование цифрового видеоизображения с аналого-цифровым преобразованием его в двоичный код 30-битной глубины цвета. Результат достигается тем, что на передающей стороне системы вводится фотоэлектрический преобразователь /ФЭП/, содержащий два приемника изображения, каждый из которых включает матрицу из преобразователей "яркость излучения - код", шесть блоков импульсных усилителей, шесть блоков выделения сигналов старших разрядов в коде, шесть блоков шифраторов и шесть блоков четырехразрядных регистров. 1 табл., 22 ил.

Реферат

Изобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания.

Прототипом принята "Универсальная система телевидения" [1], содержащая на передающей стороне два фотоэлектрических преобразователя, первый формирует сигналы трех цветов правого кадра и сигналы трех цветов левого кадра стереопар, включает шесть АЦП видеосигналов, шесть кодеров, выполняющих сжатие потока кодов кадра с коэффициентом сжатия 4 за кадр, формирователь потока кодов, два триггера, два самоходных распределителя импульсов /СРИ/, два АЦП сигналов звука, синтезатор частот и одноканальный передатчик радиосигналов, на приемной стороне содержащая блок управления, тракт приема кодов видеосигналов, первый канал обработки кодов из трех каналов цветовых сигналов R1, G1, B1, второй канал обработки кодов из трех каналов цветовых сигналов R2, G2, B2, первый и второй плоскопанельные экраны. Кадры стереопар идут параллельно, применяется полярное разделение сигналов. На приемной стороне сжатая видеоинформация восстанавливается декодерами, на правом и левом экранах воспроизводятся правый и левый кадры, которые зритель наблюдает через очки раздельных полей зрения. Недостатками прототипа являются длительный процесс считывания видеосигналов при использовании датчиком изображения матричного прибора с зарядовой инжекцией, заряды, накопленные каждым пикселом датчика ПЗИ [2, с.830], считываются в последовательном порядке по отсчетам в строке и по строкам в кадре. Каждый элемент матрицы преобразует величину светового потока в напряжение пропорционально яркости потока, которое для перевода его в цифровой видеосигнал требует еще и аналого-цифровое преобразование. Чем ниже частота считывания сигналов, тем больше величина напряжения сигнала, с увеличением частоты кадров снижается величина сигнала, снижается и качество изображения, передаваемого на приемную сторону.

Цель изобретения - применение на передающей стороне системы приемников изображения, формирующих цифровой видеосигнал, не зависящий от частоты считывания, и получение на передающей стороне 30-битной глубины цвета: десять разрядов в кодах красного, зеленого и синего цветов, на приемной стороне воспроизведение изображения с 30-битной глубиной цвета.

Техническим результатом является формирование цифрового видеоизображения кадра со скоростью распространения света с одновременным аналого-цифровым преобразованием его в двоичные коды 30-битной глубины цвета. Сущность изобретения в том, что на передающей стороне системы стереотелевидения вводится фотоэлектрический преобразователь /ФЭП/, содержащий два приемника изображения, каждый из которых включает матрицу из соответствующего числа преобразователей "яркость излучения - код", шесть блоков импульсных усилителей, шесть блоков выделения старших разрядов кода, шесть блоков шифраторов и шесть блоков четырехразрядных регистров, на приемной стороне в каждый канал обработки кодов цветового сигнала вводятся последовательно соединенные блок дешифратора и блок восстановления десятиразрядного кода. В заявляемой системе видеорежим 1000 строк × 1100 отсчетов × 25 Гц, где 1000 - число строк в кадре, 1100 - число отсчетов в строке, 25 Гц - частота стереопар. Правый и левый кадры идут параллельно. Частота дискретизации кодов видеосигналов:

fд=25 Гц × 1100 × 1000=27,5 МГц,

частота строк fc=25 Гц × 1000=25 кГц. В системе используются кодеры, выполняющие сжатие потока кодов с коэффициентом 4 за кадр. При коэффициенте сжатия 4 частота выдачи кодов из кодеров составляет: fд=27,5 МГц : 4=6,875 МГц. Частота тактовых синусоидальных колебаний при формировании потоков кодов кадра составляет:

fт=6,875 МГц × 16=110 МГц,

где 6,875 МГц - частота выдачи кодов с кодеров, 16 - число разрядов в кодах звука, в кодах цветовых сигналов по пять разрядов, суммарный код в правом и левом кадрах из 15-ти разрядов /пять разрядов цвета R, пять разрядов цвета G, пять разрядов цвета В, итого в сумме 15 разрядов/. Период следования кодов , период разрядов в коде .

Несущая частота передатчика приемной стороны принимается fн=110 МГц × 16=1760 МГц/λ=17 см дециметровый диапазон/.

Верхняя боковая частота fнв=1760+110=1870 МГц,

нижняя боковая частота fнн=1760-110=1650 МГц /λ=18 см/.

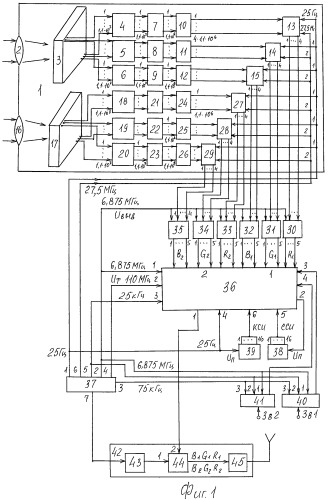

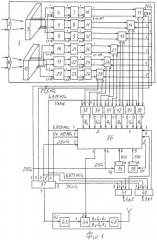

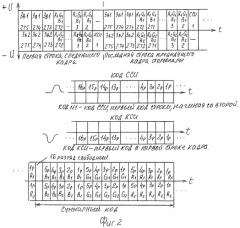

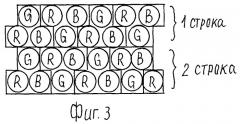

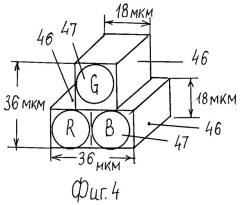

С передатчика радиосигналов параллельно передаются два потока кодов: правого кадра R1, G1, В1 и левого кадра R2,G2,B2 стереопар. На приемной стороне сжатая видеоинформация восстанавливается на 100%, на двух экранах параллельно воспроизводятся два изображения: на правом экране правый кадр, на левом экране - левый. Разрешение экранов 1100 отсч × 1000 строк = 1,1×106 пикселов. Из 1100 отсчетов в каждой строке уходит по три отсчета на передачу трех кодов звука /фиг.2/. Передающая сторона на фиг.1, структура цифрового потока на фиг.2, расположение элементов в матрице приемника изображения на фиг.3, триада одного элемента матрицы на фиг.4, преобразователь "яркость излучения - код" на фиг.5, блок выделения старшего разряда в коде на фиг.6, блок регистров на фиг.7, формирователь потока кодов на фиг.8, спектр амплитудно-модулированного сигнала на фиг.9, двухполярный амплитудный детектор на фиг.10, кодер на фиг.11, приемная сторона на фиг.12, декодер на фиг.13, блок восстановления десятиразрядного кода на фиг.14, накопитель кодов кадра на фиг.15, блоки регистров на фиг.16, 17, блок выделения ССИ, КСИ на фиг.18, один элемент матрицы и вид его внутри сверху на фиг.19, излучающая ячейка на фиг.20, размещение элементов матрицы в строке экрана на фиг.21, временные диаграммы работы системы на фиг.22.

Передающая сторона содержит /фиг.1/ фотоэлектрический преобразователь 1 /ФЭП/, являющийся датчиком сигналов трех цветов правого кадра и трех цветов левого кадра, и включает первый объектив 2 и первый приемник 3 изображения, приемная сторона которого расположена в фокальной плоскости первого объектива 2, оптическое разрешение приемника 3 изображения 1100×1000 /1,1×106/ пикселов, три группы выходов с которого 1 - 1,1×107 /10 разр × 1,1×106/ подключены к входам соответственно 1,1×107 блоков 4, 5, 6 импульсных усилителей, а выходы их 1 - 1,1×107 с каждого из блоков 4-6 подключены соответственно к входам 1 - 1,1×107 блоков 7, 8, 9 выделения сигнала старшего разряда кода, дешифраторов в блоках 7, 8, 9 соответствует разрешению кадра 1,1×106, выходы 1,1×106 блоков 7-9 подключены к стольким же входам блоков 10, 11, 12 шифраторов, каждый из которых включает шифраторы [3, с.207, рис.8.6] по числу разрешения кадра 1,1×106, выходы шифраторов подключены к входам соответствующих четырехразрядных регистров блоков 13, 14, 15 регистров, каждый из этих блоков включает четырехразрядные регистры по числу разрешения 1,1×106 кадра /фиг.7/. ФЭП 1 включает второй объектив 16, второй приемник 17 изображения, приемная сторона его расположена в фокальной плоскости объектива 16, разрешение матрицы 1,1×106 /1100×1000/, три группы выходов с которой 1,1×107 подключены к входам 1,1×107 блоков 18, 19, 20 импульсных усилителей, выходы каждого блока 18, 19, 20 подключены соответственно к входам 1,1×107 блоков 21, 22, 23, содержащие дешифраторы, выделяющие старшие сигналы в кодах, выходы 1,1×106 блоков 21-23 подключены к входам соответственно 1,1×106 блоков 24, 25, 26 шифраторов, каждый из которых содержит шифраторы по числу разрешения кадра 1,1×106, первый - четвертый выходы каждого шифратора подключены к своим четырехразрядным регистрам в блоках 27, 28, 29, каждый из которых содержит регистры по числу разрешения кадра 1,1×106, Первые - четвертые выходы блоков 13-15 и 27-29 являются выходами ФЭП 1. Передающая сторона включает шесть кодеров 30, 31, 32, 33, 34, 35, выполненных аналогично кодерам аналога [4, с.6, фиг.5, 6], включает формирователь 36 потока кодов, синтезатор 37 частот, выдающий с первого выхода импульсы частоты стереопар 25 Гц, со второго выхода импульсы Uвыд 6,875 МГц, с третьего - импульсы дискретизации кодов звука 75 кГц, с четвертого - тактовые синусоидальные колебания 110 МГц, с пятого - импульсы частоты строк 25 кГц, с шестого - импульсы частоты дискретизации кодов 27,5 МГц, с седьмого - синусоидальные колебания несущей частоты 1760 МГц. Все сигналы со стабильностью 10-7 включают первый 38 и второй 39 самоходные распределители импульсов /СРИ/, выполненные идентично [5, с.269, 274, рис.9.7], первый 40 и второй 41 АЦП сигналов звука, выполненные идентично АЦП сигналов звука в аналоге [6, с.5, фиг.7]. АЦП 40, 41 преобразуют звуковые сигналы 3в1 и 3в2 в 16-разрядные коды с частотой 75 кГц. СРИ 38 выдает код строчного синхроимпульса из 16 единиц подряд, СРИ 39 формирует код кадровых синхроимпульсов КСИ из 16 единиц подряд, при передаче коды ССИ и КСИ разделяются по полярному признаку. Передающая сторона содержит передатчик 42 радиосигналов из последовательно соединенных усилителя 43 несущей частоты, амплитудного модулятора 44, включающего последовательно соединенные кольцевой модулятор, подавляющий несущую 1760 МГц [7, с.234, 235], и полосовой фильтр, отфильтровывающий ненужную верхнюю боковую частоту 1870 МГц. Нижняя боковая частота 1650 МГц с видеоинформацией кодов стереопар поступает в выходной усилитель 45 и излучает в эфир со стабильностью 10-7, отсюда занимаемая в эфире полоса ±165 Гц или 330 Гц. Первый 3 и второй 17 приемники изображения дают "начальный продукт" системе стереотелевидения - правый и левый кадры стереопары для передачи и воспроизведения их на приемной стороне. Приемники 3, 17 изображения выполняются идентично и со скоростью распространения света формируют цифровые видеокадры правого и левого кадров, каждый включает матрицу из 1,1×106 /1100×1000/ элементов, расположенных последовательно по 1100 штук в строке, кадр включает 1000 строк. Изображения кадров проецируются объективами 2, 16 на приемные поверхности приемников 3, 17 изображения. Каждый отдельный элемент матрицы представляется триадой /фиг.4/ из трех преобразователей "яркость излучения - код" /фиг.5/. Левый инжний преобразователь принимает красное R излучение, верхний преобразователь принимает зеленое G излучение, правый нижний принимает синее В излучение. Преобразователь "яркость излучения - код" /фиг.4, 5/ включает непрозрачный корпус 46 формой прямоугольного параллелепипеда из изоляционного материала, в переднем торце корпуса 46 расположен цветной светофильтр 47 одного из базовых цветов R, G, В, за цветным светофильтром 47 в непрозрачной перегородке 48 закреплен микрообъектив 49, по оптической оси которого и под углом 45° к ней последовательно друг за другом размещены и жестко закреплены с первого по десятый полупрозрачные микрозеркала 501-10, на стороне корпуса, к которой повернуты микрозеркала, расположены с первого по десятый соответствующие фотоприемники 511-10, принимающие отраженные полупрозрачными микрозеркалами излучение и выдающие электрические импульсы в свой импульсный усилитель блока 4 /5, 6/ или 15 /16, 17/. Световой поток после цветного светофильтра поступает в микрообъектив 49, направляющий его по своей оси на центры полупрозрачных микрозеркал 501-10. Принцип преобразования "яркость излучения - код" основан на том, что каждое впереди расположенное микрозеркало 50 пропускает на следующее за ним поток света, ослабленный в два раза, что соответствует принципу двоичного кода. В микрозеркалах светоделительное покрытие, выполняющее отношение отраженного излучения к пропущенному как 1:0,5 [8, c.223]. Число полупрозрачных микрозеркал 50 соответствует получению десятиразрядных кодов. Электрический сигнал с фотоприемников 51 /фиг.5/ усиливается в импульсных усилителях блоков 4-6 и 18-20, формируется по амплитуде и длительности и поступает на входы блоков 7-9 /21-23/, дешифраторы в которых выделяют в каждом десятиразрядном коде сигнал "1" старшего разряда кода. Коды с преобразователей представляют последовательно следующие единицы, исходя из этого принимается вариант не передавать целиком десятиразрядные коды из единиц, а передать только двоичный код сигнала единицы старшего разряда в коде. В этом случае код содержит не десять разрядов, а только четыре: код единицы старшего разряда будет от 0001 до 1010 /от 1 до 10/. В этом случае уменьшается число передаваемых сигналов в 2,5 раза и можно снизить несущую частоту в 1,875 раза: вместо 30 разрядов в посылке /10×3/ передаются 16 разрядов /сигнал звука/, частота тактовых колебаний при 30 разрядах составляет 6,875 МГц × 30=206,25 МГц, несущая будет 206,25 МГц × 16=3300 МГц. На приемной стороне код восстанавливается в первоначальный вид дешифратором и блоком восстанавления кода.

| Таблица 1 | ||

| Коды с преобразователя "яркость излучения - код" | Коды сигналов старших разрядов с шифраторов блоков 10-12, 24-26 | |

| 0000000001 | 0001 | /1/ |

| 0000000011 | 0010 | /2/ |

| 0000000111 | 0011 | /3/ |

| 0000001111 | 0100 | /4/ |

| 0000011111 | 0101 | /5/ |

| 0000111111 | 0110 | /6/ |

| 0001111111 | 0111 | /7/ |

| 0011111111 | 1000 | /8/ |

| 0111111111 | 1001 | /9/ |

| 1111111111 | 1010 | /10/ |

Выделение "1" старшего разряда в кодах выполняется параллельно и одновременно во всех кодах блоков 7-9, 21-23 схемами дешифраторов 52 /фиг.6/, включающих 20 элементов НЕ и 10 элементов И по числу разрядов в коде. Десятиразрядные коды в параллельном виде поступают с выходов блоков 4-6 /18-20/ на первый - десятый входы дешифратора 52, который выдает с выхода сигнал с одного разряда - старшего разряда в каждом коде в блоки 10-12 /24-26/ шифраторов, которые, в свою очередь, выдают двоичный код этого старшего разряда в блоки регистров 13-15 /27-29/, число шифраторов в блоках 10-12 /24-26/ по 1,1×106. Блоки регистров 13-15, 27-29 идентичны, каждый включает по 1,1×106 четырехразрядных регистров /фиг.7/ 55 и последовательно соединенные ключ 56 и распределитель 57 импульсов, имеющий с первого по 1,1×106 выходы. Информационными входами блока регистров 13-15 /27-29/ являются первый - четвертый входы всех регистров, подключенные к выходам 4×1,1×106 блоков 10-12, 24-26. Выходами блоков регистров 13-15, 27-29 являются поразрядно объединенные первый-четвертый выходы всех регистров 55. Первым управляющим входом блока регистров 13-15 /27-29/ является сигнальный вход ключа 56 /27,5 МГц/, вторым управляющим входом Uот /25 Гц/ является управляющий вход ключа 56, выход которого подключен к входу распределителя 57 импульсов, выходы которого с первого по 1,1×106 последовательно подключены к управляющим входам регистров 551-1,1×10 6 и являются сигналами выдачи Uвыд кодов из регистров 55. Ключ 56 открывается передним фронтом импульса частоты кадров 25 Гц на длительность 40 мс, за которое сигналы выдачи с распределителя 57 импульсов выдают с частотой 27,5 МГц коды из регистров 55 последовательно в соответствующий кодер 30-35. Кодеры выполнены идентично кодерам аналога [2, с.6, фиг.5, 6]. Передающая сторона включает шесть кодеров 30-35, формирователь 36 потока кодов, синтезатор 37 частот, первый 38 и второй 39 самоходные распределители импульсов /СРИ/, выполненные идентично [5, с.269, 274], первый 40 и второй 41 АЦП сигналов звука, выполненные идентично АЦП сигнала звука аналога [6, с.5, фиг.7]. Кодеры идентичны, каждый включает /фиг.11/ последовательно соединенные регистр 79, схему сравнения 80, счетчик 81 импульсов и дешифратор 82, последовательно соединенные блок 83 элементов задержек, блок 84 ключей и буферный накопитель 85 кодов кадра. Первым - четвертым информационными входами являются поразрядно объединенные входы регистра 79, первые входы схемы 80 сравнения и входы блока 83 элементов задержек. Выходами являются с первого по пятый выходы буферного накопителя 85 кодов кадра, объем которого 302500 пятиразрядных кодов /275отсч×1100строк/. Поочередная выдача кодов с блоков 13-15, 27-29 в кодеры 30-32, 33-35 выполняется сигналами дискретизации кодов 27,5 МГц. Четырехразрядные коды в параллельном виде поступают на первый - четвертый входы регистра 79, на первые входы схемы 80 сравнения и на входы блока 83 элементов задержек. Исходное состояние ключей в блоке 84 открытое. Код в блоке 83 задерживается на 18 нс на время срабатывания схемы 80 сравнения и поступает через открытые ключи блока 84 на первый - четвертый разряды буферного накопителя 85 кодов кадра емкостью 302500 пятиразрядных кодов. Схема сравнения 79 выполняет сравнение по величине каждого предыдущего с последующим кодов для выявления их равенства или неравенства. При следовании неравных кодов они проходят через блок 83, открытые ключи блока 84 и поступают на первый - четвертые входы первого - четвертого разрядов буферного накопителя 85 кодов. Выдача кодов из блока 85 выполняется сигналами 6,875 МГц с блока 37. Поступление кодов в блок 85 при следовании неравных кодов идет с частотой 27,5 МГц. В общем потоке кодов имеется большое число и равных кодов по величине, чем выше частота дискретизации, тем равных кодов больше. Кодер сжимает поток с плавющим коэффициентом сжатия от 1 до 15. Средний коэффициент сжатия за кадр принимается в 4, поэтому сигналы выдачи с блока 85 осуществляются с частотой 6,875 МГц. При коэффициенте сжатия более 4 эта частота будет тем более удовлетворять. Схема 80 сравнения выполняет сравнение кодов и представляется двумя микросхемами 530СП1 с временем сравнения 18 нс [9, с.279]. При неравенстве кодов А>В появляется сигнал на выходе 2 блока 80, при равенстве кодов А=В появляется сигнал на выходе 1 блока 80, при А<В, сигнал с выхода 3. При равенстве кодов сигнал с выхода 1 закрывает ключи в блоке 84, поступает счетным импульсом Uсч на вход счетчика 81 и на первый управляющий вход Uвыд регистра 79. Счетчик 81 ведет счет импульсов с выхода 1 блока 80 пока идут равные коды. Счетчик 81 четырехразрядный, максимальный код в нем 1111 /15/, отсюда и плавающий коэффициент сжатия от 1 до 15. Счетчик 81 из микросхем К500ИЕ160 с временем срабатывания 8 нс [9, с.428]. При появлении неравных кодов со схемы 80 следует сигнал с выхода 2 или 3, которые объединены, сигнал с них используется для выдачи кода числа равных кодов из счетчика 81 через диоды в 1-4 разряды блока 85 и для заполнения в блоке 85 пятого разряда, который используется при декодировании для опознания по нему кода числа равных кодов, этот же сигнал открывает ключи в блоке 84 /вход 1/ и обнуляет регистр 79 /вход 2/. Выданный перед этим с блока 85 код является первым кодом в последовательности, на диаграмме 1 /фиг.11/ они помечены крестиками. Коды, равные по величине и подсчитанные счетчиком 81, исключаются из потока кодов, диаграмма III. Исключение равных кодов из потока определяет коэффициент сжатия. Емкость буферного накопителя 85 кодов соответствует числу пятиразрядных кодов кадра 302500 и обеспечивает темп прохода кодов с частотой 6,875 МГц. При следовании подряд кодов, равных по величине более 15 штук, в работу вступает дешифратор 82: при коде 1111 со счетчика 81 дешифратор 82 выдает импульс, который одновременно открывает ключи в блоке 84 /вход 1/, обнуляет регистр 79, выдает сигнал Uвыд кода из счетчика 81 /вход 1/ и обнуляет счетчик 81 /вход 2/, а в пятый разряд блока 85 поступает сигнал опознания кода числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы сравнения 80 /18 нс/ и составляет до 50×106 четырехразрядных кодов. С выходов кодеров 30-32 коды в параллельном виде поступают на первый информационный вход блока 36 /фиг.1/, с кодеров 33-35 коды поступают на второй информационный вход блока 36. Формирователь потока 36 кодов выдает первым код строчного синхроимпульса ССИ /фиг.2/, из сжатого потока кодов формирует и выдает со второго по 272 коды сигналов B1, G1, R1 и B2, G2, R2, и в конце каждой строки три кода 273-275 звука. Формирователь 36 потока кодов /фиг.8/ включает три канала, первый и второй идентичны. Первый канал включает последовательно соединенные первый блок 58 элементов И из 15-ти элементов И, первый 59 и второй 60 элементы ИЛИ, первый выходной ключ 61 и первый СРИ 62, второй канал включает второй блок 63 элементов И из 15-ти элементов И /три кода цветовых сигналов, каждый по пять разрядов/, третий 64 и четвертый 65 элементы ИЛИ, второй выходной ключ 66 и второй СРИ 67. Третий канал включает два блока 68, 71 элементов И по 16 элементов в каждом, пятый элемент 69 ИЛИ, шестой элемент 72 ИЛИ, третий СРИ 70 и четвертый СРИ 73. Формирователь 36 потока кодов включает первый 74, второй 75 и третий 76 ключи, последовательно соединенные 16-разрядный счетчик 77 импульсов и дешифратор 78. Информационными входами блока 36 являются: первым -первые входы элементов И блока 58, вторым - первые входы элементов И блока 63, третьим - первые /с 1 по 16/ входы элементов И блока 68, четвертым - первые /с 1 по 16/ входы элементов И блока 71, пятым - сигнальный вход третьего ключа 76, шестым - третий вход четвертого элемента ИЛИ 65. Первым выходом являются объединенные выходы выходных ключей 61, 66, вторым - третий выход дешифратора 78, подключенный к входу СРИ 38. Управляющими входами являются: первым - объединенные входы ключей 74, 75 и счетный вход счетчика 77 импульсов, вторым - объединенные входы /110 МГц/ выходных ключей 61, 66, третьим - управляющий вход 25 кГц счетчика 77, четвертым - управляющий вход Uо 25 Гц третьего ключа 76. Первый выход дешифратора подключен к первому управляющему входу Uот первого ключа 74, второй выход подключен к второму управляющему входу Uз ключа 74 и к первому управляющему входу Uот второго ключа 75, третий выход подключен к второму управляющему Uз входу второго ключа 75 и является вторым выходом блока 36. Вторые входы элементов И блоков 58, 63, блоков 68, 71 подключены к выходам СРИ соответственно 62, 67 и 70, 73, имеющие по 16 выходов, шестнадцатые выходы в СРИ 62, 67 не используются. Выход первого ключа 74 подключен к входам СРИ 62, 67, выход второго ключа 75 подключен к входам СРИ 70 и 73. Выход третьего ключа 76 подключен к третьему входу второго элемента ИЛИ 60 /фиг.8/.

Приемная сторона содержит /фиг.12/ антенну, блок 86 управления /выбор каналов/, один тракт приема и обработки кодов видеосигналов, канал формирования управляющих сигналов, первый и второй плоскопанельные экраны, два канала воспроизведения звука и очки 140 раздельных полей зрения. Тракт приема и обработки кодов видеосигналов содержит последовательно соединенные блок 87 приема радиосигналов, усилитель 88 радиочастоты и двухполярный амплитудный детектор 89 /фиг.10/, первый и второй каналы обработки кодов видеосигналов: первый канал обработки кодов включает последовательно соединенные первый формирователь 90 импульсов, вход которого подключен к первому выходу двухполярного амплитудного детектора 89, первый приемный регистр 91 из пятнадцати разрядов и три канала цветовых сигналов: канал сигнала R1, канал сигнала G1, канал сигнала В1, второй канал обработки кодов включает последовательно соединенные второй формирователь 111 импульсов, вход которого подключен к второму выходу двухполярного амплитудного детектора 89, второй приемный регистр 112 из 15-ти разрядов и три канала цветовых сигналов: канал сигнала R2, канал сигнала G2, канал сигнала В2. Канал сигнала R1 включает последовательно соединенные пятиразрядный регистр 92, декодер 93, дешифратор 94, блок 95 восстановления десятиразрядного кода, накопитель 96 кодов кадра и блок 97 импульсных усилителей, включающий импульсные усилители по числу выходов накопителя 96 кодов кадра и разрядов в коде 10×1,1×106 /1100×1000/, канал сигнала G1 включает последовательно соединенные регистр 98, декодер 99, дешифратор 100, блок 101 восстановления 10-разрядного кода, накопитель 102 кодов кадра и блок 103 импульсных усилителей из 1,1×107 импульсных усилителей, канал сигнала В1 включает пятиразрядный регистр 104, декодер 105, дешифратор 106, блок 107 восстановления 10-разрядного кода, накопитель 108 кодов кадра и блок 109 импульсных усилителей из 1,1×107 импульсных усилителей. Выходы блоков 97, 103, 109 импульсных усилителей подключены к входам 3×1,1×107 первого плоскопанельного экрана 110. Канал сигнала R2 включает регистр 113, декодер 114, дешифратор 115, блок 116 восстановления 10-разрядного кода, накопитель 117 кодов кадра и блок 118 импульсных усилителей из 1,1×107, канал G2 включает пятиразрядный регистр 119, декодер 120, дешифратор 121, блок 122 восстановления 10-разрядного кода, накопитель 123 кодов кадра и блок 124 импульсных усилителей, канал сигнала B2 включает пятиразрядный регистр 125, декодер 126, дешифратор 127, блок 128 восстановления 10-разрядного кода, накопитель 129 кодов кадра и блок 130 импульсный усилителей из 1,1×107 импульсных усилителей. Выходы блоков 118, 124, 130 подключены к входам 3×1,1×107 второго плоскопанельного экрана 131. Порядок работы приемной стороны задает канал формирования управляющих сигналов, включающий блок 132 выделения строчных синхроимпульсов /ССИ/, синтезатор частот 133, ключ 134, счетчик 135 импульсов и дешифратор 136, и блок 137 выделения кадровых синхроимпульсов /КСИ/. Приемная сторона включает идентичные первый 138 и второй 139 каналы воспроизведения звука, каждый из которых содержит преобразователь 16-разрядных кодов звука в аналоговые сигналы /ЦАП/, усилитель мощности и громкоговоритель. Зритель воспринимает изображение объемным через очки 140 раздельных полей зрения. Очки содержат /Фиг.12/ оправу с дужками для ушей, окна очков без стекол, между собой соединены подвижно вертикальной осью для поворота их относительно друг друга в горизонтальной плоскости, для разделения полей зрения глаз каждое окно очков имеет съемную конусную бленду на конце прямоугольной формы и под форму экрана. Бленда из двух частей: первая часть вкручивается в окно очков, вторая часть подвижная, выдвигается и вдвигается в первую, изменяя длину бленды. При просмотре зритель разворотом окон очков и изменением длин бленд настраивает поля зрений глаз так, чтобы каждый глаз видел только свой экран. Декодеры 93, 99, 105, 114, 120, 126 идентичны, каждый содержит последовательно соединенные первый пятиразрядный регистр 141, накопитель 142 кодов кадра емкостью 299200 /272 отсчета × 1100 строки/ пятиразрядных кодов, второй пятиразрядный регистр 143, первый блок 144 ключей из четырех ключей и третий четырехразрядный регистр 145, последовательно соединенные второй блок 146 ключей из четырех ключей, четырехразрядный вычитающий счетчик 147 импульсов и дешифратор 148, первый 149, второй 150, третий 151 и четвертый 152 ключи. Информационным входом являются первый - пятый входы регистра 141, выходом являются первый - четвертый выходы третьего регистра 145. Управляющими входами являются: первым - объединенные управляющие входы регистра 141 и сигнальный вход 6,875 МГц третьего ключа 151, вторым - объединенные сигнальные входы 27,5 МГц ключей 149, 150, 152. Выход пятого разряда регистра 143 подключен параллельно к первому управляющему входу второго ключа 150, к вторым управляющим входам ключей 151, 152 и 149, к второму управляющему входу Uз блока 144 и к первому управляющему Uот входу второго блока 146 ключей. Выход ключа 149 подключен к первому управляющему входу Uвыд1 регистра 145, второй управляющий вход Uвыд2 которого подключен к выходу второго ключа 150, к которому подключен и счетный вход вычитающего счетчика 147 импульсов. Выход дешифратора 148 подключен параллельно к первому управляющему входу первого блока 144 ключей, к второму управляющему входу Uз блока 146 ключей, к первым управляющим входам Uот ключей 149, 151, 152 и к второму управляющему вxoду Uз ключа 150. Выход третьего ключа 151 подключен к управляющему входу Uвыд накопителя 142 кодов кадра, выход ключа 152 подключен к управляющему входу Uвыд второго регистра 143.

Работа декодера, фиг.13

Коды в параллельном виде поступают в первый регистр 141, с которого выдаются в накопитель 142 кодов кадра емкостью 299200 пятиразрядных кодов, из которого выдаются коды сигналами 6,875 МГц с ключа 151. При закрытом ключе 151 накопитель 142 сосредотачивает коды в себе. Исходное состояние ключей в блоке 144 открытое, в блоке 146 закрытое, ключей 149, 151, 152 открытое, ключа 150 закрытое. В первый - пятый разряды второго регистра 143 поступают сигналы 1-4 разрядов, а при наличии сигнала в пятом разряде кода /сигнал опознания кода числа равных кодов/ он поступает в пятый разряд регистра 143, с которого выдается сигналом Uвыд с ключа 152 с частотой 27,5 МГц. Пока в регистр 143 поступают коды без сигнала опознания, они поступают через открытые ключи в блоке 144 в третий регистр 145, а с него выдаются сигналом Uвыд1 с ключа 149 на выход декодера с частотой 27,5 MГц. Сигнал Uвыд1 при выдаче кода и обнуляет 1-4 разряды регистра 145. При поступлении в регистр 143 кода с сигналом опознания в пятом разряде сигнал с пятого разряда закрывает ключи в блоке 144, открывает ключи в блоке 146, закрывает ключи 149, 151, 152 и открывает ключ 150. Выдача кодов с регистра 143 прерывается, а накопитель 142 производит накопление кодов кадра, так как в него продолжают поступать коды. Код числа равных кодов через открытые ключи блока 146 поступает в вычитающий счетчик 147 импульсов, на счетный вход которого с ключа 150 поступают импульсы 27,5 МГц. Импульсы с ключа 150 поступают сигналом выдачи Uвыд2 на второй управляющий вход регистра 145 и выдают содержащийся в нем код, но при этом не обнуляют его. Поэтому пока идет работа счетчика 147 на вычитание из регистра 145 выдается один и тот же код, эти коды были изъяты при сжатии потока кодов в кодере на передающей стороне. С выхода регистра 145 идет восстановленный на 100% поток кодов. С регистра 145 идут четырехразрядные коды с частотой 27,5 МГц. По окончании вычитания в счетчике 147 в дешифратор 148 поступает код из нулей, с выхода дешифратора 148 сигнал закрывает ключи в блоке 146 /вход 2/, закрывает ключ 150, открывает ключи в блоке 144 и ключи 149, 151, 152. С накопителя 142 кодов опять выдаются коды в регистр 143, с него через открытые ключи блока 144 в регистр 145, далее процессы повторяются. Пропускная способность декодера задается временем срабатывания счетчика 147 /10,5 нс/, микросхема 100ИЕ137 [9, с.428] плюс время срабатывания дешифратора 148 /микросхема 100ИД161 [9, с.433]/, скорость восстановления до 50 Мбайт/с. Восстановленный поток с частотой 27,5 МГц поступает на входы дешифраторов 94, 100, 106, 115, 121, 127. На входы дешифраторов поступают комбинации двоичных кодов от 0001 до 1010 /от 1 до 10/, которым с выходов дешифраторов соответствует один соответствующий выход [3, с.202]. При дешифрировании соответственно двоичному коду на одном из десяти выходов дешифратора появляется сигнал, поступающий на соответствующий вход блока 95 /101, 107, 116, 122, 128/ восстановления десятиразрядного кода. Блоки восстановления десятиразрядных кодов идентичны /фиг.14/, каждый включает десять входов, девять групп диодов, подключенных к соответствующим группам диодов, и десять выходов, на которых появляется восстановленный десятиразрядный код. На фиг.14 приведен пример восстановления кода 0000111111: на вход дешифратора поступил двоичный код 0110, на пятом выходе дешифратора 94 появляется сигнал, который поступает на пятый вход блока 95 /фиг.14/, и на пятом-десятом выходах блока 95 появляются сигналы, представляющие восстановленный код 0000111111, полученный на передающей стороне преобразователем "яркость излучения - код". Первая группа диодов в блоке 95 из одного диода, вход его подключен к первому входу /старшему/ блока 95, а выход диода подключен к второму выходу блока 95. Вторая группа диодов из двух диодов, выходы их объединены и подключены к третьему выходу блока 95, а входы их раздельно подключены к первому и второму входам блока 95. Третья группа диодов из трех диодов, выходы их объединены и подключены к четвертому выходу блока 95, а входы подключены раздельно к первому - третьему входам блока 95, четвертая группа из четырех диодов, выходы их подключены к пятому выходу блока 95, входы их подключены раздельно к первому - четвертому входам блока 95, пятая группа из пяти диодов, выходы их подключены к шестому выходу блока 95, а входы подключены раздельно к первому - пятому входам блока 95, шестая группа диодов из шести диодов, выходы их подключены к седьмому выходу блока 95, а входы раздельно подключены к первому - шестому входам блока 95, седьмая группа диодов из семи диодов, выходы их объединены и подключены к восьмому выходу блока 95, а входы подключены раздельно к первому - седьмому входам блока 95, восьмая группа диодов из восьми диодов, выходы их подключены к девятому выходу блока 95, а входы их подключены раздельно к первому - восьмому входам блока 95, девятая группа из девяти диодов, выходы их объединены и подключены к десятому выходу блока 95, а входы раздельно подключены к первому - девятому входам блока 95. Блоки 95, 101, 107, 116, 122, 128 востановления дестиразрядных кодов восстанавливают коды в первоначальный вид, которыми они были на выходах преобразователей "яркость излучения - код" приемников 3, 17 изображения /фиг.1/. Восстановленные десятиразрядные коды поступают в свои накопители 96, 102, 108, 117, 123, 129 кодов кадра, выполненные идентично, каждый включает (фиг.15) блоки 1531-1000 регистров по числу строк в кадре /1000/. Информационным входом накопителя кодов кадра являются поразрядно объединенные первый - десятый входы блоков 1531-1000 регистров. Выходами являются параллельные выходы всех блоков 153 регистров, которых 10×1,1×106 или 1,1×107. Управляющими входами каждого блока накопителя кодов кадра являются: первым - первый управляющий вход 25 Гц первого блока 1531 регистров, вторым - объединенные вторые управляющие входы 25 кГц Uвыд блоков 153 регистров, третьим - объединенные третьи управляющие входы Uд 27,5 МГц блоков 153 регистров. Каждый управляющий выход предыдущего блока регистров является первым управляющим входом для каждого последующего блока 153 регистров /фиг.15/, управляющий выход последнего блока 1531000 регистров подключен параллельно к четвертым управляющим входам всех блоков 153 регистров, всего выходов с накопителя 96 кодов кадра 1,1×107. Блоки 153 регистров выполнены идентично, каждый включает /фиг.16, 17/ первый 154, второй 155 ключи, распределитель 156 импульсов и десять регистров 1571-10, каждый из 1100 разрядов по числу отсчетов в строке. Информационными входами блока 153 регистров являются поразрядно объединенные первый - десятый третьи входы разрядов десяти регистров 157. Выходами являются параллельные выходы всех 1100 разрядов десяти регистров 157: всего выходов 11000 /10×1100/. Управляющими входами являются: первым - первый управляющий вход Uот 25 Гц первого ключа 154, вторым - сигнальный вход 25 кГц Uвыд второго ключа 155, третьим - сигнальный вход Uд 27,5 МГц первого ключа 154, четвертым - первый управляющий вход Uот ключа 155. Последний выход распределителя 156 импульсов является управляющим выходом блока 1531 в следующий блок 1532 регистров и подключен к его первому управляющему входу первого 154 ключа. Выход ключа 154 подключен к входу распределителя 156 импульсов, выходы которого последовательно с первого по 1100-й подключены параллельно к первым /тактовым/ входам разрядов десяти регистров 157. Выход второго ключа 155 подключен параллельно к вторым входам разрядов десяти регистров 157 и к второму управляющему Uз входу своего ключа 155, прошедший один импульс Uвыд закрывает ключ 155. Выходы накопителей 96, 102, 108, 117, 123, 129 подключены к информационным входам своих блоков 97, 103, 109, 118, 124, 130 импульсных усилителей, каждый из которых включает импульсные усилители по числу разрешения кадра и числу разрядов в коде: 10×1,1×106 или 1,1×107. С приходом сигнала с последнего блока 1531000 регистров на четвертые управляющие входы всех блоков 1531-1000 регистров все коды правого и левого кадров выдаются в блоки импульсных усилителей, с выходов которых сигналы единиц в кодах, усиленные до необходимой величины и длительностью 40 мс, параллельно поступают на входы соответственно экранов 110, 131. Блок 132 выделения строчных синхроимпульсов ССИ и блок 137 выделения кадровых синхроимпульсов КСИ выполнены идентично, каждый включает /фиг.18/ пятиразрядный счетчик 158 импульсов, дешифратор 159, элемент НЕ 160 и два диода Д1, Д2. Счетчик 158 ведет счет 16-ти импульсов /код 10000/. Информационным входом блока 132 является счетный вход счетчика 158, подключенный к выходу формирователя 90 импульсов, управляющим входом является вход диода Д1, подключенный к выходу второго формирователя 111 импульсов /Фиг.12/. В блоке 137 информационный вход подключен к выходу второго формирователя 111 импульсов, а управляющий вход подк