Интегрирующий число-импульсный аналого-цифровой преобразователь

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и может быть использовано в системах автоматизации для преобразования аналогового сигнала в цифровой код. Техническим результатом является повышение помехоустойчивости устройства. Устройство содержит преобразователь напряжения в частоту импульсов, два логических элемента «2И», двоичный счетчик, регистр памяти, устройство сравнения кодов, генератор тактовых импульсов, логический элемент «НЕ» и элемент задержки. 3 ил.

Реферат

Изобретение относится к области вычислительной техники и может использоваться в системах автоматизации для преобразования аналогового сигнала в цифровой код.

Известен аналого-цифровой преобразователь (АЦП) с поразрядным уравновешиванием (Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника (полный курс): учебник для вузов. Под. ред. О.П.Глудкина. - М.: Горячая линия. - Телеком, 2007, - 768 с.), содержащий регистр памяти и регистр последовательных приближений, аналоговый компаратор, цифроаналоговый преобразователь, логические элементы, генератор тактовых импульсов, источник входного сигнала.

Известный АЦП обладает низкой помехоустойчивостью, что требует включения на входе сглаживающего фильтра, ограничивающего полосу пропускания АЦП.

Известен многозонный развертывающий преобразователь, содержащий последовательно включенные источник входного сигнала, первый сумматор и интегратор, выход которого подключен к входам группы из нечетного числа релейных элементов, выходы которых соединены с входами второго сумматора, выход которого соединен с выходом устройства и со вторым входом первого сумматора (SU 1183988 СССР, G06G 7/12. Развертывающий усилитель / Цытович Л.И. - №3734334/24, заявлено 27.04.84. Опубл. 07.10.85. Бюл. №37).

При определенных схемных дополнениях данное интегрирующее устройство может работать в режиме АЦП, однако его полоса пропускания будет определяться не только частотой, но и амплитудой преобразуемого сигнала.

Наиболее близким к предлагаемому техническому решению является АЦП число-импульсного типа (Волович Г.И. Схемотехника аналоговых и аналогово-цифровых электронных устройств. - М.: Издательский дом «Додэка-XXI», 2005, - 459 с.), содержащий последовательно включенные преобразователь напряжения в частоту импульсов (ПНЧ), двоичный счетчик, регистр памяти, а также генератор тактовых импульсов, подключенный к R-входу двоичного счетчика и к С-входу регистра памяти.

Недостатком устройства-прототипа является асинхронная перезапись данных из двоичного счетчика в регистр памяти, когда синхроимпульсы перезаписи формируются в произвольные периоды времени и определяются параметрами генератора тактовых импульсов. Такой режим работы АЦП приводит к формированию «лишних» тактов перезаписи, которые возникают при равенстве кодов в двоичном счетчике и регистре памяти.

В то же время очевидно, что избыточные переключения в цифровых схемах приводят к снижению не только их помехоустойчивости, но и к помехоустойчивости соседних функциональных узлов, так как в процессе формирования импульсного сигнала всегда возникает импульсная помеха, например, по цепям электропитания.

Таким образом, устройство-прототип характеризуется низкой помехоустойчивостью.

В основу изобретения положена техническая задача, направленная на повышение помехоустойчивости число-импульсного АЦП за счет оптимизации числа циклов перезаписи данных из двоичного счетчика в регистр памяти.

Указанная техническая задача решается тем, что в интегрирующий число-импульсный аналого-цифровой преобразователь, содержащий преобразователь напряжения в частоту импульсов, вход которого является «входом» устройства, генератор тактовых импульсов, а также последовательно включенные двоичный счетчик и регистр памяти, выходы которого являются цифровым «выходом» устройства, согласно изобретению введены элемент задержки, последовательно включенные логический элемент «НЕ» и первый логический элемент «2И», а также последовательно включенные устройство сравнения кодов и второй логический элемент «2И», выход которого подключен к С-входу регистра памяти, причем первая группа входов устройства сравнения кодов соединена с выходами двоичного счетчика, а вторая группа входов устройства сравнения кодов подключена к выходам регистра памяти, выход генератора тактовых импульсов одновременно соединен со вторым входом второго логического элемента «2И», входом логического элемента «НЕ» и входом элемента задержки, выход которого подключен к R-входу двоичного счетчика, выход преобразователя напряжения в частоту импульсов соединен со вторым входом первого логического элемента «2И», выход которого подключен к С-входу двоичного счетчика.

В результате поставленная техническая задача достигается за счет того, что в устройство введены элемент задержки, последовательно включенные логический элемент «НЕ» и первый логический элемент «2И», а также последовательно включенные устройство сравнения кодов и второй логический элемент «2И». Элемент задержки устраняет одновременную установку в двоичном счетчике нулевых начальных условий и запись данных в регистр памяти из-за их различного времени переходного процесса. Логические элемент «Не» и первый логический элемент «2И» препятствуют прохождению импульсов с выхода преобразователя напряжения в частоту импульсов на счетный С-вход двоичного счетчика в моменты времени формирования синхроимпульсов с выхода генератора тактовых импульсов. Перенос данных из счетчика в регистр памяти производится только в случае неравенства их содержимого, что достигается за счет введения устройства сравнения кодов и второго логического элемента «2И». В результате оптимизируется число включений элементов, осуществляющих перезапись данных в АЦП, и повышается его помехоустойчивость.

Таким образом, предлагаемое устройство обладает повышенной помехоустойчивостью.

Изобретение поясняется чертежами:

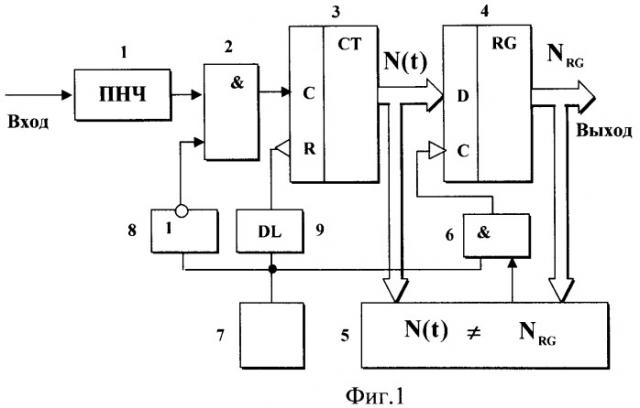

Фиг.1 - функциональная схема предлагаемого устройства;

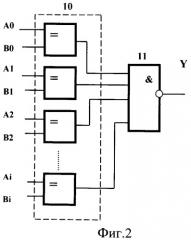

Фиг.2 - пример реализации устройства сравнения кодов;

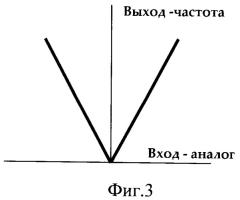

Фиг.3 - характеристика «вход-выход» ПНЧ.

В состав интегрирующего число-импульсного аналого-цифрового преобразователя (фиг.1) входят последовательно включенные ПНЧ 1, первый логический элемент 2 функции «2И», двоичный счетчик 3, регистр памяти 4, устройство сравнения кодов (УСК) 5 и второй логический элемент 6 функции «2И», выход которого подключен к С-входу регистра памяти 4, а также генератор тактовых импульсов 7, логический элемент 8 функции «Не» и элемент задержки 9, выход которого соединен с R-входом двоичного счетчика 3. Причем вторая группа входов устройства сравнения кодов 5 подключена к выходам двоичного счетчика 3, выход регистра памяти 4 является цифровым «выходом» устройства. Выход генератора тактовых импульсов 7 одновременно соединен со вторым входом второго логического элемента 6 функции «2И», входом логического элемента 8 функции «НЕ» и входом элемента задержки 9, выход которого подключен к R-входу двоичного счетчика 3. Выход логического элемента 8 функции «НЕ» соединен со вторым входом первого логического элемента 2 функции «2И», вход ПНЧ 1 является «входом» устройства.

УСК 5 (фиг.2), например, содержит группу логических элементов 10 функции «Равнозначность», выходы которых подключены к входам логического элемента 11 функции «nИ-НЕ», выход которого является выходом УСК 5. Первые входы А0, А1, …, Ai группы логических элементов 10 функции «Равнозначность» соединены с соответствующими выходами регистра памяти 4, а вторые входы В0, В1, …, Bi группы логических элементов 10 функции «Равнозначность» - с соответствующими выходами двоичного счетчика 3.

Элементы АЦП имеют следующие характеристики.

ПНЧ 1 является реверсивным и преобразует аналоговый входной сигнал в частоту импульсов, которая линейно возрастает с ростом амплитуды входного воздействия (фиг.3). Контур формирования знакового разряда на структуре АЦП (фиг.1) не показан с целью ее упрощения.

Логические элементы 2, 6 функции «2И» формируют на выходе сигнал логической «1» только в том случае, когда входные сигналы имеют уровень логической «1».

Двоичный счетчик 3 является суммирующим и увеличивает свое содержимое на единицу младшего разряда синхронно с передним фронтом импульса на С-входе. При воздействии заднего фронта импульса на R-вход счетчик 3 переходит в «нулевое» состояние по всем разрядам.

Регистр памяти 4 записывает данные со своих D-входов синхронно с передним фронтом импульса на С-входе.

УСК 5 переключается в состояние логической «1» в случае неравенства кодов, поступающих с выходов двоичного счетчика 3 и регистра памяти 4.

Генератор тактовых импульсов 7 формирует высокочастотные импульсы малой длительности со стабильной частотой для перезаписи данных из двоичного счетчика 3 в регистр памяти 4.

Уровень сигнала на выходе логического элемента 8 функции «НЕ» противоположен по отношению к уровню входного сигнала.

Элемент задержки 9 сдвигает во времени импульс синхронизации с выхода генератора тактовых импульсов 7 на величину «τ», оставляя без изменений его амплитуду и длительность.

Логические элементы «Равнозначность» группы 10 (фиг.2) формируют на выходе сигнал логической «1» при совпадении уровней разрядов Ai, Bi сравниваемых кодов.

Логический элемент 11 функции «nИ-НЕ» переключается в состояние логической «1» при условии наличия «1» на всех его входах. Если хотя бы на одном из входов логического элемента 11 формируется логический «0», выходной сигнал принимает состояние «1».

Принцип работы устройства следующий.

ПНЧ 1 преобразует входной аналоговый сигнал в частоту импульсов, которые через логический элемент 2 функции «2И» подаются на С-вход двоичного счетчика 3. Логический элемент 2 функции «2И» открыт сигналом логической «1» с выхода логического элемента 8 функции «Не», так как отсутствует сигнал на выходе генератора тактовых импульсов 7.

При неравенстве кодов с выходов двоичного счетчика 3 и регистра памяти 4 УСК 5 находится в состоянии логической «1», но эта «1» не проходит на С-вход регистра памяти 4 из-за нулевого значения сигнала на выходе генератора тактовых импульсов 7, при котором логический элемент 6 функции «2И» формирует сигнал логического «0».

В момент формирования синхроимпульса с выхода генератора тактовых импульсов 7 закрывается логический элемент 2 функции «2И» сигналом логического «0» с выхода логического элемента 8 функции «НЕ» и открывается логический элемент 6 функции «2И», в результате чего данные из двоичного счетчика 3 переписываются в регистр памяти 4. Как только содержимое двоичного счетчика 3 и регистра памяти 4 становятся равными, УСК 5 переключается в состояние логического «0».

С задержкой времени «τ» двоичный счетчик 3 «обнуляется», и процесс счета повторяется. При этом запись данных в регистр памяти 4 производится только в том случае, когда содержимое последующего такта преобразования входного сигнала в код отличается от содержимого регистра памяти 4 за предыдущий такт работы АЦП.

Таким образом, за счет оптимизации циклов перезаписи данных из двоичного счетчика 3 в регистр памяти 4 повышается помехоустойчивость АЦП.

Промышленная применимость.

Рассмотренное устройство предполагается использовать в регуляторе температуры сушильной камеры электроцеха на ОАО «Челябинский трубопрокатный завод».

Интегрирующий число-импульсный аналого-цифровой преобразователь, содержащий преобразователь напряжения в частоту импульсов, вход которого является «входом» устройства, генератор тактовых импульсов, а также последовательно включенные двоичный счетчик и регистр памяти, выходы которого являются цифровым «выходом» устройства, отличающийся тем, что в него введены элемент задержки, последовательно включенные логический элемент «НЕ» и первый логический элемент «2И», а также последовательно включенные устройство сравнения кодов и второй логический элемент «2И», выход которого подключен к С-входу регистра памяти, причем первая группа входов устройства сравнения кодов соединена с выходами двоичного счетчика, а вторая группа входов устройства сравнения кодов подключена к выходам регистра памяти, выход генератора тактовых импульсов одновременно соединен со вторым входом второго логического элемента «2И», входом логического элемента «НЕ» и входом элемента задержки, выход которого подключен к R-входу двоичного счетчика, выход преобразователя напряжения в частоту импульсов соединен со вторым входом первого логического элемента «2И», выход которого подключен к С-входу двоичного счетчика.