Твердотельное устройство формирования изображения и способ возбуждения для твердотельного устройства формирования изображения

Иллюстрации

Показать всеИзобретение относится к твердотельному устройству формирования изображения. Сущность изобретения: твердотельное устройство формирования изображения содержит первую часть фотоэлектрического преобразования, узел с плавающей диффузионной областью, первый транзистор передачи для передачи электрона, генерируемого в первой части фотоэлектрического преобразования, к узлу с плавающей диффузионной областью, транзистор усиления для вывода сигнала на основании величины заряда узла с плавающей диффузионной областью, управляемый напряжением узел и часть управления напряжением для управления напряжением управляемого напряжением узла. Транзистор усиления сконфигурирован для вывода первого сигнала в первом состоянии, в котором напряжение узла с плавающей диффузионной областью сброшено, а также для вывода второго сигнала во втором состоянии, в котором электрон передается к узлу с плавающей диффузионной областью, а управляемый напряжением узел подсоединен к узлу с плавающей диффузионной областью через емкость связи, часть управления напряжением сконфигурирована для управления напряжением управляемого напряжением узла так, что напряжение управляемого напряжением узла является первым напряжением, когда транзистор усиления выводит первый сигнал, напряжение управляемого напряжением узла является вторым напряжением в течение по меньшей мере части периода, в котором первый транзистор передачи находится в проводящем состоянии, и напряжение управляемого напряжением узла является третьим напряжением, когда транзистор усиления выводит второй сигнал, и в котором второе напряжение выше, чем каждое из первого напряжения и третьего напряжения. Изобретение обеспечивает хорошую линейность выходного сигнала, улучшая эффективность передачи заряда от части фотоэлектрического преобразования к плавающей диффузионной области. 10 н. и 22 з.п. ф-лы, 10 ил.

Реферат

ОБЛАСТЬ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Настоящее изобретение относится к твердотельному устройству формирования изображения.

ОПИСАНИЕ УРОВНЯ ТЕХНИКИ

[0002] Твердотельное устройство формирования изображения увеличивающего типа, являющееся одним типом твердотельного устройства формирования изображения, передает заряд, генерируемый в части фотоэлектрического преобразования каждого пикселя, к входному узлу транзистора усиления через часть передачи.

[0003] Когда заряд передается, шум может быть уменьшен, если заряд части фотоэлектрического преобразования полностью передан. Выложенная японская заявка на патент 2005-192191 описывает способ, полезный для увеличения максимальной величины заряда, который может быть передан из части фотоэлектрического преобразования.

[0004] Согласно твердотельному устройству формирования изображения, описанному в выложенной японской заявке на патент № 2005-192191, прежде чем начать передачу заряда от фотодиода к плавающей диффузионной области (FD), напряжение FD устанавливается равным более высокому значению, чем напряжение FD, когда оно сброшено. Однако управление напряжением FD, когда сигнал выводится из транзистора усиления после того, как заряд был передан, не описано.

[0005] Согласно твердотельному устройству формирования изображения увеличивающего типа желательно управлять схемой усилителя в пределах рабочего диапазона, где линейность выходного сигнала является хорошей. Согласно твердотельному устройству формирования изображения, описанному в выложенной японской заявке на патент № 2005-192191, если напряжение FD высоко, в некоторых случаях транзистор усиления работает в линейной области или транзистор усиления работает в граничной области области насыщения и линейной области. Чтобы поддержать линейность выходного сигнала, желательно управлять транзистором усиления в области насыщения. Таким образом, твердотельное устройство формирования изображения, описанное в выложенной японской заявке на патент № 2005-192191, имеет возможность усовершенствования с точки зрения линейности выходного сигнала из транзистора усиления.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0006] Настоящее изобретение относится к твердотельному устройству формирования изображения, которое реализует хорошую линейность выходного сигнала, улучшая эффективность передачи заряда от части фотоэлектрического преобразования к плавающей диффузионной области.

[0007] Согласно аспекту настоящего изобретения твердотельное устройство формирования изображения включает в себя первую часть фотоэлектрического преобразования, плавающую диффузионную область, первый транзистор передачи, сконфигурированный, чтобы передавать электрон, генерируемый в первой части фотоэлектрического преобразования, к плавающей диффузионной области, транзистор усиления, сконфигурированный для вывода сигнала на основании величины заряда плавающей диффузионной области, управляемый напряжением узел и часть управления напряжением, конфигурируемую для управления напряжением управляемого напряжением узла. Транзистор усиления выводит первый сигнал в первом состоянии, когда напряжение плавающей диффузионной области сброшено, и транзистор усиления выводит второй сигнал во втором состоянии, когда электрон передается к плавающей диффузионной области, и управляемый напряжением узел является узлом, отличным от узла, к которому подается напряжение, используемое для управления проводящим состоянием первого транзистора передачи, и подсоединен к плавающей диффузионной области через емкость связи. Часть управления напряжением управляет напряжением управляемого напряжением узла так, чтобы напряжение управляемого напряжением узла было первым напряжением, когда транзистор усиления выводит первый сигнал, вторым напряжением в течение по меньшей мере части периода, в котором первый транзистор передачи находится в проводящем состоянии, и третьим напряжением, когда транзистор усиления выводит второй сигнал и второе напряжение является напряжением более высоким, чем каждое из первого напряжения и третьего напряжения.

[0008] Согласно примерному варианту осуществления настоящего изобретения линейность может быть улучшена, и таким образом твердотельное устройство формирования изображения, которое реализует улучшенное качество изображения, может быть обеспечено.

[0009] Дополнительные признаки и аспекты настоящего изобретения станут очевидными из нижеследующего подробного описания примерных вариантов осуществления со ссылками на прилагаемые чертежи.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0010] Прилагаемые чертежи, которые включены в и составляют часть описания, иллюстрируют примерные варианты осуществления, признаки и аспекты изобретения и вместе с описанием служат, чтобы объяснить принципы изобретения.

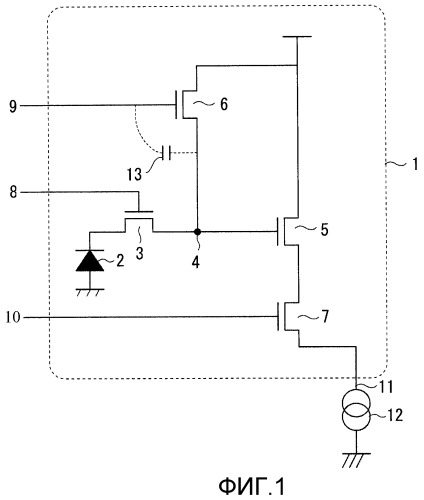

[0011] Фиг. 1 является эквивалентной схемой пикселя согласно первому примерному варианту осуществления настоящего изобретения.

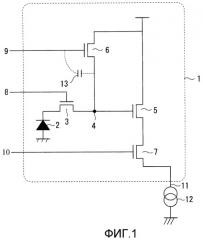

[0012] Фиг. 2 является схемой пиксельной области и части хранения сигнала согласно первому примерному варианту осуществления.

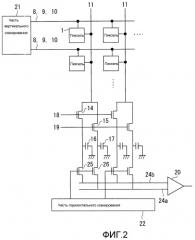

[0013] Фиг. 3 иллюстрирует импульсы возбуждения для возбуждения твердотельного устройства формирования изображения согласно первому примерному варианту осуществления.

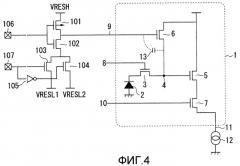

[0014] Фиг. 4 иллюстрирует схему, которая реализует эквивалентную схему пикселя, и импульсы возбуждения, иллюстрированные на Фиг. 3, согласно первому примерному варианту осуществления.

[0015] Фиг. 5 является эквивалентной схемой пикселя согласно второму примерному варианту осуществления настоящего изобретения.

[0016] Фиг. 6 иллюстрирует импульсы возбуждения для возбуждения твердотельного устройства формирования изображения согласно второму примерному варианту осуществления.

[0017] Фиг. 7 является эквивалентной схемой пикселя согласно третьему примерному варианту осуществления настоящего изобретения.

[0018] Фиг. 8 иллюстрирует импульсы возбуждения, используемые для возбуждения твердотельного устройства формирования изображения согласно третьему примерному варианту осуществления.

[0019] Фиг. 9 иллюстрирует импульсы возбуждения, используемые для возбуждения твердотельного устройства формирования изображения согласно третьему примерному варианту осуществления.

[0020] Фиг. 10 иллюстрирует эквивалентную схему пикселя согласно альтернативной версии первого примерного варианта осуществления.

ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0021] Различные примерные варианты осуществления, признаки и аспекты изобретения описаны подробно ниже со ссылками на чертежи.

[0022] Фиг. 1 иллюстрирует эквивалентную схему пикселя согласно первому примерному варианту осуществления настоящего изобретения. Согласно первому примерному варианту осуществления электрон несет заряд сигнала.

[0023] На Фиг. 1 пиксель 1 включает в себя фотодиод (PD) 2, являющийся частью фотоэлектрического преобразования, транзистор 3 передачи, FD 4, транзистор 5 усиления, транзистор 6 сброса и транзистор 7 выбора. Падающий свет фотоэлектрически преобразуется посредством PD 2. Согласно настоящему варианту осуществления электрон рассматривают как заряд сигнала относительно генерирования пары электрон-дырка в PD 2. Транзистор 3 передачи передает заряд сигнала от PD 2 к FD 4. FD 4 связана с затвором транзистора 5 усиления.

[0024] Транзистор 5 усиления выводит сигнал на основании величины заряда FD 4. Согласно настоящему варианту осуществления транзистор 5 усиления является транзистором металл-окисел-полупроводник (MOS) с n-каналом со скрытым каналом типа. Транзистор 6 сброса подает напряжение на основании мощности сброса к FD 4 и сбрасывает напряжение FD 4. Посредством транзистора 7 выбора строка пикселей, которая должна быть считана, выбирается из множества строк пикселей.

[0025] Линии управления 8, 9 и 10 связаны с затворами транзистора 3 передачи, транзистора 6 сброса и транзистора 7 выбора соответственно. Затворы транзисторов электрически не закорочены друг с другом. Хотя емкость связи может быть обеспечена между каждым из затворов, проводящим состоянием каждого транзистора нужно управлять независимо. Выходной усиленный сигнал из транзистора 5 усиления выводится к вертикальной выходной линии 11. Источник 12 постоянного тока связан с вертикальной выходной линией 11. Схема истокового повторителя конфигурируется транзистором 5 усиления и источником 12 постоянного тока.

[0026] Конденсатор 13, который обеспечен между затвором транзистора 6 сброса и FD 4, является емкостью связи между затвором и истоком транзистора 6 сброса. Так как конденсатор 13 обеспечен, напряжение FD 4 может быть изменено согласно напряжению, подаваемому на затвор транзистора 6 сброса.

[0027] Хотя детали описаны ниже, согласно настоящему варианту осуществления напряжением FD 4 может управлять посредством управления напряжением линии 9 управления, соединенной с затвором транзистора 6 сброса. Более конкретно, напряжением линии 9 управления, когда электрон передается от PD 2 к FD 4, управляют так, чтобы оно было выше, чем напряжение линии 9 управления, когда транзистор 5 усиления выводит сигнал.

[0028] Фиг. 2 является схемой пиксельной области и части хранения сигнала согласно настоящему варианту осуществления. Пиксельная область конфигурируется матрицей из множества пикселей 1, иллюстрированных на Фиг. 1. Линии 8, 9 и 10 управления обычно соединены с множеством пикселей, включенных в одну строку пикселей. Часть 21 вертикального сканирования подает заранее определенное напряжение к каждой из линий 8, 9 и 10 управления. Далее, часть 21 вертикального сканирования управляет проводящим состоянием соответствующего транзистора. Так как короткозамкнутое соединение не установлено между затворами транзисторов пикселей, проводящим состоянием каждого транзистора можно управлять независимо. Часть 21 вертикального сканирования конфигурирует часть части управления напряжением, описанной ниже.

[0029] Вертикальная выходная линия 11 обычно подсоединена к выходным узлам множества пикселей, включенных в один столбец пикселей. Как иллюстрировано на Фиг. 1, выходным узлом пикселя является, например, исток транзистора 7 выбора. В другом случае выходным узлом является исток транзистора усиления. Каждый из сигналов, выведенный из множества вертикальных выходных линий 11, подается на часть хранения сигнала при приблизительно одинаковом тактировании и сохраняется в части хранения сигнала.

[0030] Согласно настоящему варианту осуществления часть хранения сигнала обеспечена для каждого столбца пикселей. Часть хранения сигнала согласно настоящему варианту осуществления включает в себя два переключателя 14 и 15, так же как два конденсатора 16 и 17 выборки-и-запоминания. Переключатели 14 и 15 управляют электрическим соединением между вертикальной выходной линией 11 и конденсаторами 16 и 17 выборки-и-запоминания. Линии управления 18 и 19 соединены с каждым из затворов переключателей 14 и 15. Далее, импульсы возбуждения, используемые для управления проводящим состоянием соответствующего переключателя, подаются на линии управления 18 и 19.

[0031] Конденсатор 17 выборки-и-запоминания удерживает сигнал (в дальнейшем называемый сигналом N), выведенный из транзистора 5 усиления, когда напряжение FD 4 сброшено. Согласно настоящему варианту осуществления FD 4 находится в состоянии сброшенного напряжения с того момента, когда транзистор 6 сброса подает напряжение на основании мощности сброса к FD 4, до того момента, когда заряд сигнала передается к FD 4. По меньшей мере при некотором тактировании во время этого периода осуществление выборки сигнала N может быть выполнено в конденсаторе 17 выборки-и-запоминания. Шум сброса, который генерируется, когда транзистор 6 сброса выключается, может быть включен в сигнал N.

[0032] Конденсатор 16 выборки-и-запоминания удерживает сигнал (в дальнейшем называемый сигналом S), выведенный из транзистора 5 усиления, когда заряд сигнала передается к FD 4. Согласно настоящему варианту осуществления FD 4 находится в состоянии передачи заряда с того момента, когда заряд сигнала передается к FD 4, до того момента, когда напряжение, основанное на сбросе электропитания, подается на FD 4. По меньшей мере при некотором тактировании во время этого периода осуществление выборки сигнала S может быть выполнено.

[0033] Переключатели 25 и 26 управляют соединением конденсаторов 16 и 17 выборки-и-запоминания и горизонтальных выходных линий 24a и 24b. Импульсы возбуждения, используемые для управления проводящим состоянием переключателей 25 и 26, подаются на соответствующий переключатель от части 22 горизонтального сканирования. Посредством части 22 горизонтального сканирования сигнал S, удерживаемый конденсатором 16 выборки-и-запоминания, и сигнал N, удерживаемый конденсатором 17 выборки-и-запоминания, последовательно вводятся в каждый столбец в дифференциальном усилителе 20.

[0034] Дифференциальный усилитель 20 усиливает разность между сигналами S и N и выводит полученный результат. Шум фиксированного образца из-за изменения в пороговом значении транзистора 5 усиления удаляется посредством обработки вычисления разности между сигналами S и N. Если сигналы S и N включают в себя шум сброса, относящийся друг к другу, этот шум сброса, который генерировался, когда FD 4 был сброшен, может быть удален.

[0035] Фиг. 3 иллюстрирует импульсы возбуждения, используемые для возбуждения твердотельного устройства формирования изображения согласно настоящему варианту осуществления. Дополнительно Фиг. 3 схематично иллюстрирует изменение в напряжении FD 4 согласно работе твердотельного устройства формирования изображения из настоящего варианта осуществления.

[0036] На Фиг. 3 PRES обозначает импульс возбуждения, подаваемый на затвор транзистора 6 сброса через линию 9 управления. PTX обозначает импульс возбуждения, подаваемый на затвор транзистора 3 передачи через линию 8 управления. PTS обозначает импульс возбуждения, подаваемый на переключатель 14 через линию 18 управления. PTN обозначает импульс возбуждения, подаваемый на переключатель 15 через линию 19 управления. Когда напряжение импульса возбуждения имеет высокий уровень, соответствующий транзистор и переключатель включены. Когда напряжение импульса возбуждения имеет низкий уровень, соответствующий транзистор выключен.

[0037] Далее, согласно настоящему варианту осуществления, два различных напряжения VRESL1 и VRESL2 могут быть установлены как напряжения низкого уровня PRES, подаваемого от линии 9 управления. Хотя и VRESL1 и VRESL2 являются напряжениями, которыми транзистор 6 сброса выключается, VRESL2 выше, чем VRESL1. Другими словами, транзистор 6 сброса включен, когда напряжение, подаваемое на PRES, является напряжением высокого уровня VRESH, и выключен, когда напряжение, подаваемое на PRES, является напряжением низкого уровня VRESL1 или VRESL2 (VRESL2 > VRESL1).

[0038] Затем способ возбуждения твердотельного устройства формирования изображения согласно настоящему варианту осуществления описан со ссылками на Фиг. 3. На Фиг. 3 уже было начато воздействие, и PD 2 имеет заряд сигнала. Далее, транзистор 7 выбора из строки пикселей, которая должна быть считана, включен.

[0039] Сначала PTX, PTS и PTN имеют низкий уровень и транзистор 3 передачи и переключатели 14 и 15 выключены. Так как PRES имеет высокий уровень и транзистор 6 сброса включен, напряжение FD 4 сбрасывается. В этом состоянии напряжение Vrs сброса FD 4 получают следующим уравнением (1), используя напряжение VRESH, подаваемое на затвор транзистора 6 сброса, и пороговое напряжение Vth_res транзистора 6 сброса. Напряжение мощности сброса выше, чем

VRESH-Vth_res:

Vrs=VRESH-Vth_res. (1)

[0040] В момент T101 PRES изменяется от VRESH на VRESL1. Согласно этому изменению в напряжении затвора транзистора 6 сброса напряжение FD 4 уменьшается на ΔV1 через конденсатор 13. После того как транзистор 6 сброса выключился в момент времени T101, сигнал N, который является сигналом, выведенным, когда напряжение FD 4 сброшено, выводится к вертикальной выходной линии 11. Шум сброса, такой как шум kTC, который генерируется, когда транзистор 6 сброса выключается, включают в сигнал N.

[0041] Затем в момент T102, PTS и PTN изменяются на высокий уровень, переключатели 14 и 15 включаются, и вертикальная выходная линия 11 и конденсаторы 16 и 17 выборки-и-запоминания проводят. Соответственно конденсаторы 16 и 17 выборки-и-запоминания сбрасываются сигналом N, выведенным к вертикальной выходной линии 11. В момент времени T103, PTS и PTN изменяются на низкий уровень, и вертикальная выходная линия 11 и конденсаторы 16 и 17 выборки-и-запоминания не проводят.

[0042] В момент времени T104 PTN изменяется на высокий уровень. Затем переключатель 15 включается, и начинается запись сигнала N в конденсаторе выборки-и-запоминания 17. В момент времени T105 PTN изменяется на низкий уровень, переключатель 15 выключается, и запись сигнала N в конденсаторе выборки-и-запоминания 17 завершается. Как иллюстрировано на Фиг. 3, желательно иметь возможность управлять напряжением затвора транзистора 6 сброса в VRESL1 и иметь период (T104 к T105), во время которого PTN имеет высокий уровень, достаточно долго, так чтобы этого было достаточно для стабилизации изменения напряжения FD.

[0043] Затем в момент времени T106 PTS изменяется на высокий уровень, переключатель 14 включается, и начинается запись сигнала S на конденсатор выборки-и-запоминания 16.

[0044] В момент времени T107 напряжение PRES изменяется от VRESL1 на VRESL2. Согласно этому изменению в напряжении напряжение FD 4 увеличивается на ΔV2 через конденсатор 13. Даже если напряжение PRES увеличится до VRESL2, транзистор 6 сброса не будет включен.

[0045] В момент времени T108 PTX изменяется на высокий уровень, и транзистор 3 передачи включается. В данный момент начинается передача заряда сигнала PD 2 к FD 4. В момент времени T109 PTX изменяется на низкий уровень, транзистор 3 передачи выключается, и передача заряда сигнала завершается. Желательно иметь возможность иметь время между T108 и T109 достаточно долгим так, чтобы весь заряд сигнала, накопленный в PD 2, мог быть передан.

[0046], Если весь заряд сигнала передан, другими словами, если заряд сигнала полностью передан, передача заряда сигнала может быть закончена перед временем T109. Далее, согласно величине заряда сигнала, переданного к FD 4, напряжение FD 4 уменьшается на напряжение Vsig. После того как заряд сигнала передан к FD 4, этот сигнал S, который является сигналом, выведенным в состоянии, когда заряд сигнала передается к FD 4, выводится к вертикальной выходной линии 11.

[0047] В момент времени T110, когда напряжение PRES изменяется от VRESL2 на VRESL1, напряжение FD 4 уменьшается на ΔV2.

[0048] Затем в момент времени T111 PTS изменяется на низкий уровень. Затем переключатель 14 выключается, и запись сигнала S на конденсатор выборки-и-запоминания 16 завершается. Желательно иметь возможность управлять напряжением затвора транзистора 6 сброса в VRESL1 и иметь период (T110 до T111), во время которого PTS имеет высокий уровень достаточно долго так, чтобы этого было достаточно для стабилизации изменения напряжения FD. В момент времени T112 PRES изменяется на VRESH, и напряжение FD 4 сбрасывается.

[0049] Есть два важных замечания относительно настоящего варианта осуществления. Первое замечание - это то, что напряжением, подаваемым на затвор транзистора 6 сброса, управляют при VRESL1 в момент времени T105 и момент времени Т111. Второе замечание - это то, что напряжением, подаваемым на затвор транзистора 6 сброса от момента времени T107 до момента времени T110, управляют при VRESL2, являющимся напряжением выше, чем VRESL1.

[0050] Согласно второму замечанию заряд сигнала может быть передан в FD 4 при напряжении ΔV2 выше, чем когда VRESL1 выводится. Напряжение PD 2 уменьшается с напряжения в момент времени, когда оно сброшено перед фотоэлектрическим преобразованием согласно величине заряда сигнала, генерируемого фотоэлектрическим преобразованием. В таком состоянии, так как напряжение FD 4 увеличивается на ΔV2, разность напряжений между PD 2 и FD 4 может быть увеличена. Соответственно, максимальная величина заряда, которая может быть передана от PD 2 к FD 4, может быть увеличена, и полная передача заряда сигнала может быть выполнена более просто.

[0051] Далее, согласно первому замечанию, так как напряжение FD 4 уменьшается, транзистор 5 усиления может работать более легко в области насыщения. Таким образом, линейность выходного сигнала от транзистора усиления может быть улучшена.

[0052] Согласно операции, иллюстрированной на Фиг. 3, в то время как транзистор 3 передачи включен, напряжение затвора транзистора 6 сброса непрерывно поддерживается при напряжении выше, чем напряжение, выведенное транзистором усиления. Однако эта операция может быть выполнена, пока период, в течение которого напряжением, подаваемым на затвор транзистора 6 сброса, управляют при VRESL2, накладывается на часть периода, во время которого включен транзистор 3 передачи.

[0053] Фиг. 4 иллюстрирует пример схемы, используемой для подачи трех значений VRESH, VRESL1 и VRESL2 к линии 9 управления. P-канальный MOS (PMOS) транзистор 101 включен, когда напряжение низкого уровня подается на затвор, и выключен, когда подается напряжение высокого уровня. N-канальные MOS (NMOS) транзисторы 102, 103 и 104 включены, когда напряжение высокого уровня подается на каждый из затворов, и выключены, когда напряжение низкого уровня подается на каждый из затворов. Схема также включает в себя инвертор 105.

[0054] Если напряжение первого узла 106 установлено в низкий уровень, VRESH выводится на линию 9 управления независимо от напряжения второго узла 107. Если напряжения и первого узла 106 и второго узла 107 установлены равными высокому уровню, VRESL1 выводится на линию 9 управления. Если напряжение первого узла 106 установлено в высокий уровень и напряжение второго узла 107 установлено в низкий уровень, VRESL2 выводится на линию 9 управления.

[0055] Транзисторы 101-104 и инвертор 105 размещены в каскаде, следующем за частью 21 вертикального сканирования, иллюстрированной на Фиг. 2, или интегрированы в часть 21 вертикального сканирования. Импульс от части 21 вертикального сканирования подается к по меньшей мере любому из первого узла 106 и второго узла 107. Другими словами, импульс от части 21 вертикального сканирования может подаваться и к первому узлу 106 и ко второму узлу 107, но может подаваться к одному из узлов. Когда импульс подается только к одному из узлов, импульс может подаваться другому узлу непосредственно извне микросхемы или извне микросхемы через простую логическую схему.

[0056] Таким образом, так как напряжения трех значений могут подаваться к линии 9 управления по меньшей мере частью 21 вертикального сканирования, транзисторами 101-104 и инвертором 105, эти компоненты функционируют как часть управления напряжением узла, который связан с FD через емкость связи. Далее, генератор тактирования может быть включен в часть управления напряжением.

[0057] Ниже эффект, полученный настоящим вариантом осуществления, описан подробно. Сначала описаны условия, требуемые при выполнении полной передачи заряда сигнала части фотоэлектрического преобразования, и условия, требуемые при благоприятном поддержании линейности выходного сигнала датчика.

[0058] В нижеследующем описании максимальная величина заряда, которая может быть накоплена в PD 2, называется как величина насыщенного заряда. Если величина насыщенного заряда сигнала накоплена в PD 2, условие, необходимое при выполнении полной передачи заряда сигнала, выражается следующим уравнением (2):

Vrs-Vsat>Vdep, (2)

где Vsat - величина изменения напряжения FD 4, когда величина насыщенного заряда сигнала PD 2 передается в FD 4, и Vdep - напряжение FD 4, необходимое для выполнения полного истощения PD 2.

[0059] Из полупроводниковых областей, которые конфигурируют PD 2, область, которая полностью истощена, является по меньшей мере полупроводниковой областью n-типа. Vdep - напряжение, которое может полностью истощить полупроводниковую область n-типа, которая конфигурирует PD 2. Как можно видеть из уравнения (2) относительно полной передачи заряда сигнала, желательно более высокое напряжение сброса Vrs для FD 4.

[0060] Чтобы получить хорошую линейность, основанную на хорошем соотношении между количеством падающего света и выходным сигналом транзистора усиления, транзистор 5 усиления должен удовлетворять следующему уравнению (3), являющемуся условием для работы истокового повторителя (условие для работы в области насыщения):

Vg-Vd<Vth_sf, (3)

где Vg, Vd и Vth_sf являются напряжением затвора, напряжением стока и пороговым напряжением транзистора 5 усиления соответственно.

[0061] Как проиллюстрировано на Фиг. 1, так как затвор транзистора 5 усиления соединен с FD 4, Vg является напряжением FD 4. Точно так же, так как сток транзистора 5 усиления соединен с электропитанием, Vd является напряжением электропитания. Так как напряжение FD 4 уменьшается, когда заряд сигнала передается к FD 4, если уравнение (3) удовлетворено, когда Vg является Vrs, являющимся напряжением сброса FD 4, хорошая линейность может быть поддержана по широкой области светимости. Таким образом, условие для хорошей линейности в широкой области светимости может быть выражено следующим уравнением (4):

Vrs-Vd<Vth_sf. (4)

[0062] Как показывает уравнение (4), чтобы улучшить линейность, желательно более низкое напряжение FD 4. Другими словами, желательно более низкое напряжение сброса FD 4. Однако, если напряжение сброса Vrs уменьшается, чтобы удовлетворить уравнение (4), становится трудным удовлетворить уравнение (2), являющееся условием для полной передачи.

[0063] Способ для увеличения напряжения FD 4 для полной передачи заряда сигнала описан в выложенной японской заявке на патент № 2005-192191. Однако, если сигнал выводится от транзистора 5 усиления в состоянии, когда напряжение FD 4 является высоким, так как трудно удовлетворить уравнение (3), становится трудным получить линейность.

[0064] Как описано выше, существует компромисс между полной передачей заряда сигнала или передачей заряда с высокой эффективностью и линейностью выходных сигналов из транзистора усиления. Таким образом, фокусом внимания является момент, когда уравнение (2), являющееся условием для реализации полной передачи заряда сигнала, и уравнение (4), являющееся условием для реализации хорошей линейности, должны быть удовлетворены.

[0065] Уравнение (2) должно быть удовлетворено, только когда заряд передается (с момента времени T108 до T109 на Фиг. 3) и не обязательно удовлетворено, когда передача заряда не выполняется. С другой стороны, уравнение (4) должно быть удовлетворено, только во время T111 и T105, когда сигнал S и сигнал N записаны в соответствующих конденсаторах 16 и 17 выборки-и-запоминания, и не обязательно удовлетворено в другие периоды. Таким образом, чтобы удовлетворить эти два условия, напряжением FD 4 управляют при низком уровне во время T111 и T105 и управляют при высоком уровне в по меньшей мере части времени между T108 и T109.

[0066] Согласно настоящему варианту осуществления VRESL1 подается на затвор транзистора 6 сброса в момент времени T105 и Т111, и VRESL2 подается на затвор транзистора 6 сброса между временем T107 и T110. Напряжение FD 4 в момент времени T107 выражается как Vrs-ΔV1+ΔV2. Напряжение FD 4 в момент времени T105 выражается как Vrs-ΔV1. Таким образом, условие для полной передачи заряда сигнала и условие для того, чтобы получить хорошую линейность могут быть выражены следующими уравнениями (5) и (6) посредством использования уравнения (1):

VRESH-Vth_res-ΔV1+ΔV2-Vsat>Vdep, (5)

VRESH-Vth_res-ΔV1-Vd<Vth_sf. (6)

[0067] Напряжение FD 4 во время Т111 выражено как Vrs-ΔV1-Vsig. Vsig - величина изменения напряжения FD 4 из-за передачи заряда сигнала. Если зарядом сигнала является электрон, так как напряжение FD 4 уменьшается согласно передаче заряда сигнала, хорошая линейность может быть получена, если уравнение (6) удовлетворено.

[0068] Например, фиксируя VRESH и фиксируя VRESL2, которое обеспечивает ΔV2, которое удовлетворяет уравнение (5) после установки VRESL1, которое обеспечивает ΔV1, которое удовлетворяет уравнение (6), оба уравнения (5) и (6) могут быть удовлетворены. Таким образом, согласно настоящему варианту осуществления, даже если напряжение FD 4 увеличивается, когда заряд сигнала передается так, чтобы максимальная величина заряда, которая может быть передана, увеличивается, хорошая линейность выходного сигнала датчика может быть получена. Хотя желательно полностью удовлетворить уравнения (5) и (6), управляя напряжением FD 4 при низком уровне во время Т111 и T105 и управляя напряжением FD 4 при высоком уровне в по меньшей мере части времени между T108 и T109, некоторый эффект может быть получен, даже если уравнения (5) и (6) полностью не удовлетворены.

[0069] Далее, посредством использования транзистора со скрытым каналом типа в качестве транзистора 5 усиления, шум, такой как шум случайного телеграфного сигнала (RTS), может быть уменьшен. Чем глубже скрыт канал в канальной части из интерфейса изолятора затвора и канальной части, тем больше получается эффект снижения шума. Однако, если транзистор со скрытым каналом типа будет использоваться как транзистор 5 усиления, то Vth_sf будет уменьшен. Так как Vth_sf уменьшается, когда канал скрыт глубже в части канала, становится трудным удовлетворить уравнение (4). Таким образом, когда конфигурация настоящего варианта осуществления применяется к транзистору со скрытым каналом типа, используемому как транзистор усиления, эффект усовершенствования относительно линейности может быть распознан более ясно.

[0070] Каждое из уравнений (2) и (4) может быть модифицировано как следующие уравнения (7) и (8). Если пороговое напряжение транзистора 5 усиления является низким, особенно когда оно становится отрицательным, Vsat+Vdep может быть меньше, чем Vd + Vth_sf. Напряжение сброса Vrs, который удовлетворяет оба уравнения (7) и (8) одновременно, не существует. Если настоящее изобретение реализовано таким образом, эффект усовершенствования относительно линейности в низкой области светимости может быть распознан более ясно:

Vsat+Vdep<Vrs, (7)

Vrs<Vd+Vth_sf. (8)

[0071] Далее, в качестве способа для решения проблемы полной передачи способ, который увеличивает напряжение FD, когда заряд передается, описан в выложенной японской заявке на патент № 2005-192191. Этот способ использует емкость связи, обеспеченную между линией выходного сигнала усиленного выходного сигнала от транзистора усиления и FD. Эта емкость связи может быть конденсатором, который преднамеренно встроен, но может также быть паразитной емкостью.

[0072] Если емкость связи является паразитной емкостью, так как изменение вследствие производственного процесса будет существенным, точность в управлении напряжением также изменяется. Емкость FD состоит из многих компонентов, таких как емкость p-n перехода, емкость, обеспеченная между линией (проводной) от FD к затвору транзистора усиления и другой линией или кремниевой подложкой, и емкость затвора транзистора усиления.

[0073] Среди этих емкостей емкость, обеспеченная между линией от FD к затвору транзистора усиления и между линией верхнего уровня, имеет тенденцию изменяться согласно изменению по толщине пленки межслойного диэлектрика. Изменение особенно заметно, когда используется общий метод многослойного соединения, который использует химическую механическую планаризацию (CMP) в процессе планаризации.

[0074] Согласно настоящему варианту осуществления исток транзистора 6 сброса соединен с FD 4, и напряжение FD 4 управляется емкостью связи, обеспеченной между затвором и истоком транзистора 6 сброса. Емкость связи между затвором и истоком транзистора 6 сброса является главным компонентом конденсатора 13.

[0075] Так как изменение в производстве из-за процесса формирования электрода затвора транзистора MOS меньше, чем изменение в производстве из-за процесса CMP, согласно конфигурации, описанной выше, напряжением FD 4 можно точно управлять. Согласно конфигурации, которая управляет напряжением затвора транзистора MOS, исток или сток которого соединены с FD, линейность выходного сигнала может быть улучшена посредством использования способа, оказывающего меньшее влияние из-за производственного процесса на изменение.

[0076] Далее, существующий вариант осуществления может быть реализован, преднамеренно обеспечивая емкость для FD 4. Однако в этом случае область расположения пиксельной части будет затронута. Согласно настоящему варианту осуществления, так как напряжением FD 4 управляют посредством использования емкости связи, обеспеченной между затвором и истоком транзистора 6 сброса, это не будет влиять на расположение пиксельной части.

[0077] Преимущество малого изменения из-за процесса изготовления получают, когда емкость связи соединена с затвором транзистора MOS и FD. Преимущество неоказания воздействия на расположение пиксельной части получают, когда емкость связи соединена с затвором транзистора MOS и FD, включенного в пиксель. Транзистором MOS является, например, транзистор сброса, транзистор передачи или транзистор выбора.

[0078] Согласно настоящему варианту осуществления управляют напряжением, подаваемым на затвор транзистора 6 сброса так, чтобы VRESL1 подавалось в момент времени T105 и Т111. Однако, если напряжение, подаваемое на затвор транзистора 6 сброса, ниже, чем VRESL2, отличные напряжения могут подаваться на затвор транзистора 6 сброса в момент времени T105 и Т111. Это имеет место потому, что усовершенствование линейности может быть получено, пока, когда сигналы S и N выдаются, напряжением затвора транзистора 6 сброса управляют при напряжении ниже, чем напряжение, которое используется, когда выполняется передача заряда.

[0079] Как с настоящим вариантом осуществления, если напряжения одного и того же значения подаются на затвор транзистора 6 сброса в момент времени T105 и Т111, разность в опорных напряжениях сигналов S и N не имеет места. Таким образом, выходной сигнал датчика с малым смещением может быть получен, когда выполняется обработка разности сигналов S и N.

[0080] Если заряд сигнала переносится электроном, может использоваться p-канальный транзистор усиления. Фиг. 10 является эквивалентной схемой пикселя согласно альтернативной версии первого примерного варианта осуществления. На Фиг. 10 компоненты, подобные проиллюстрированным на Фиг. 1, обозначены такими же цифровыми ссылками, и подробные описания не повторяются.

[0081] Согласно альтернативной версии первого примерного варианта осуществления p-канальный транзистор усиления 100 является транзистором MOS. Сток p-канального транзистора 100 усиления соединен с узлом, который подает напряжение земли (GND). Исток p-канального транзистора 100 усиления соединен с вертикальной выходной линией 11 через транзистор 7 выбора. Источник 12 постоянного тока соединен с вертикальной выходной линией 11. Схема истокового повторителя конфигурируется p-канальным транзистором 100 усиления и источником 12 постоянного тока.

[0082] Согласно такой конфигурации, так как напряжение вертикальной выходной линии 11 увеличивается, когда увеличивается напряжение FD 4, напряжения обоих концов источника 12 постоянного тока будут уменьшаться. Таким образом, транзистор, который включен в источник 12 постоянного тока, может работать более легко в линейной области. Если транзистор в источнике 12 постоянного тока работает в линейной области, так как значение тока, который течет через вертикальную выходную линию 11, изменяется, линейность выходного сигнала ухудшается.

[0083] Далее, когда заряд сигнала переносится дыркой, эффект, подобный первому примерному варианту осуществления, получают, если транзистор с p-каналом используется как транзистор усиления.

[0084] Фиг. 5 иллюстрирует эквивалентную схему пикселя согласно второму примерному варианту осуществления настоящего изобретения. Компоненты, подобные таковым в первом примерном варианте осуществления, обозначены теми же самыми цифровыми ссылками, и их описания не повторяются.

[0085] Согласно настоящему варианту осуществления PD 2 и PD 31 соединены с одним FD 4 через транзистор 3 передачи и транзистор 32 передачи. Два пикселя совместно используют один FD 4 и один транзистор 5 усиления. Согласно вышеописанной конфигурации заряд сигнала двух пикселей может быть суммирован и считан. Далее, заряд сигнала, накопленный в каждом PD, может быть независимо считан. Хотя один FD 4 иллюстрирован на Фиг. 5, случай, когда одна полупроводниковая область обеспечена для каждого пикселя и полупроводниковые области электрически соединены так, чтобы сформировать один узел FD 4, также рассматривается как совместное использов