Устройство для моделирования процесса принятия решения в условиях неопределенности

Иллюстрации

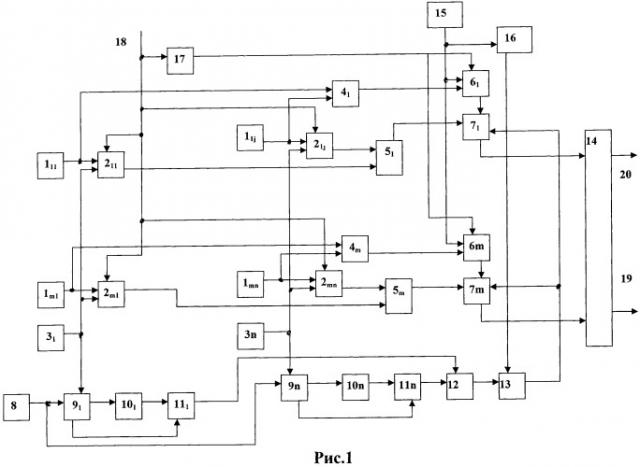

Показать всеИзобретение относится к автоматике и вычислительной технике. Техническим результатом является повышение быстродействия работы устройства для моделирования процесса принятия решения в условиях неопределенности. Устройство содержит первые регистры 1ij (i=1,…,m, j=1,…,n), вторые блоки умножения 2ij (i=1,…,m, j=1,…,n), вторые регистры 3j (j=1,…,n ), первые сумматоры 4i (i=1,…,m), вторые сумматоры 5i (i=1,…,m), первые блоки умножения 6i (i=1,…,m), четвертые сумматоры 7i (i=1,…,m), 9j (j=1,…,n), первые элементы задержки 10j (j=1,…,n), элементы И 11j (j=1,…,n), пятый сумматор 12, третий блок умножения 13, схему выбора максимального кода 14, третий регистр 15, шестой сумматор 16, второй элемент задержки 17, вход 18, выходы 19 и 20. 1 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является разработка устройства для моделирования процесса принятия решения в условиях неопределенности, обеспечивающего более высокое быстродействие.

Наиболее близким по технической сущности является устройство [1], содержащее матрицу m*n первых регистров 1ij (i=1,…,m, j=1,…,n), группу из n вторых 3j регистров, группу из m первых сумматоров 4i, группу из m первых блоков умножения 6 i , третий 15 и четвертый регистры 8, шестой сумматор 16.

Недостатком данного устройства является низкое быстродействие из-за применения аналого-цифровых преобразователей, функционирующих по сигналам от генератора тактовых импульсов [1].

Задача изобретения - создать устройство, обеспечивающее моделирование процесса принятия решения в условиях неопределенности с более высоким быстродействием.

Сущность изобретения состоит в том, что в устройство для моделирования процесса принятия решения, содержащее матрицу m*n первых регистров 1ij (i=1,…,m, j=1,…,n), группу из n вторых 3j регистров, группу из m первых сумматоров 4i, группу из m первых блоков умножения 6i, третий 15 и четвертый регистры 8, шестой сумматор 16, введены матрица m*n вторых блоков умножения 2ij (i=1,…,m, j=1,…,n), группу из m вторых сумматоров 5i, группу из n третьих сумматоров 9j, группу из m четвертых сумматоров 7i, группу из n первых элементов задержки 10j, второй элемент задержки 17, группу из n элементов И 11j, пятый сумматор 12, третий блок умножения 13, блок выбора максимального кода 14, выход каждого регистра 1ij (i=1,…,m, j=1,…,n) подсоединен к одноименному входу первого сумматора 4i и к первому входу второго блока умножения 2ij, второй вход которого подсоединен к выходу второго 3j регистра, вход устройства 18 подсоединен к третьему входу второго блока умножения 2ij и через второй элемент задержки 17 подсоединен к первым входам первых блоков умножения 6i (i=1,…,m), выход каждого первого сумматора 4i подсоединен во второму входу первого блока умножения 6i, выход каждого второго блока умножения 2ij подсоединен к одноименным входам вторых сумматоров 5i, выход которого подсоединен к первому входу четвертого сумматора 7i, второй вход которого подсоединен к выходу одноименного первого блока умножения 6i, выход четвертого регистра 8 подсоединен к первым входам третьих сумматоров 9j, второй вход которого подсоединен к выходу одноименного второго регистра 3j, первый выход третьего сумматора 9j через первый элемент задержки 10j подсоединен к первому входу группы элементов И 11j, второй вход которой подсоединен к второму выходу сумматора 9j, выход группы элементов И 11j подсоединен к одноименному входу пятого сумматора 12, выход которого подсоединен к первому входу третьего блока умножения 13, выход третьего регистра 15 подсоединен к третьим входам первых блоков умножения 6i и к входу шестого сумматора 16, выход которого подсоединен к второму входу третьего блока умножения 13, выход которого подсоединен к третьим входам четвертых сумматоров 7i, выход каждого из которых подсоединен к одноименным входам блока выбора максимального кода 14, на выходе 20 которого появляется максимальное значение кода, а на выходе 19 - его порядковый номер.

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

Новизна предлагаемого устройства заключается в том, что новое техническое устройство отличается от прототипа тем, что дополнительно в него введены матрица m*n вторых блоков умножения 2ij (i=1,…,m, j=1,…,n), группу из m вторых сумматоров 5i, группу из n третьих сумматоров 9j, группу из m четвертых сумматоров 7i, группу из n первых элементов задержки 10j, второй элемент задержки 17, группу из n элементов И 11j, пятый сумматор 12, третий блок умножения 13, блок выбора максимального кода 14, выход каждого регистра 1ij (i=1,…,m, j=1,…,n) подсоединен к одноименному входу первого сумматора 4i и к первому входу второго блока умножения 2ij, второй вход которого подсоединен к выходу второго 3j регистра, вход устройства 18 подсоединен к третьему входу второго блока умножения 2ij и через второй элемент задержки 17 подсоединен к первым входам первых блоков умножения 6i (i=1,…,m), выход каждого первого сумматора 4i подсоединен во второму входу первого блока умножения 6i, выход каждого второго блока умножения 2ij подсоединен к одноименным входам вторых сумматоров 5i, выход которого подсоединен к первому входу четвертого сумматора 7i, второй вход которого подсоединен к выходу одноименного первого блока умножения 6i, выход четвертого регистра 8 подсоединен к первым входам третьих сумматоров 9j второй вход которого подсоединен к выходу одноименного второго регистра 3j, первый выход третьего сумматора 9j через первый элемент задержки 10j подсоединен к первому входу группы элементов И 11j, второй вход которой подсоединен к второму выходу сумматора 9j, выход группы элементов И 11j подсоединен к одноименному входу пятого сумматора 12, выход которого подсоединен к первому входу третьего блока умножения 13, выход третьего регистра 15 подсоединен к третьим входам первых блоков умножения 6i и к входу шестого сумматора 16, выход которого подсоединен к второму входу третьего блока умножения 13, выход которого подсоединен к третьим входам четвертых сумматоров 7i, выход каждого из которых подсоединен к одноименным входам блока выбора максимального кода 14, на выходе 20 которого появляется максимальное значение кода, а на выходе 19 - его порядковый номер.

Изобретательский уровень достигается тем, что ввод соответствующих элементов в известный прототип вместе со связями позволяет решить новую техническую задачу, решение которой в известных технических решениях и в литературе, в настоящее время не отражено.

Предлагаемое устройство позволяет быстро решить задачу моделирования процесса принятия решения в условиях неопределенности.

Сущность изобретения поясняется чертежом (фиг.1), на котором приведена структурная схема заявленного устройства.

Предполагается, что имеется m допустимых стратегий (управляющих воздействий А={ai}(i=1,2,…m) на систему). При этом вероятность наступления исхода sj из множества исходов S={sj}, (j=1,2,…n) в результате применения стратегии ai задается распределением вероятностей на множестве возможных исходов Psj/ai. Кроме того, каждому исходу sj приписывается некоторая субъективная ценность исхода wj∈W, W={wj}, (j=1,2,…n).

Известен некоторый уровень притязаний Qp, соответствующий наименьшему значению полезности, при котором исход события удовлетворяет лицо, принимающее решение (ЛПР). Известен также коэффициент β (0<=β<=1), характеризующий отношение ЛПР к риску. Вводится в рассмотрение величина Qj=(Qp-wj)(j=1,2,…n) для случая, при котором Qp >wj, и Qj=0 для случая, при котором Qp =<wj.

Устройство позволяет в результате просмотра всех альтернативных и возможных вариантов выбрать наилучшую альтернативу ai∈A(i=1,2,…m), для которой выполняется максимум целевой функции:

.

Устройство для решения задачи моделирования процесса принятия решения в условиях неопределенности, показанное на фиг.1, содержит: первые регистры 1ij (i=1,2,…m, j=1,2,…n), вторые блоки умножения 2ij (i=1,2,…m, j=1,2,…n), вторые регистры 3j (j=1,2,…n), первые сумматоры 4i (i=1,2,…m), вторые сумматоры 5i (i=1,2,…m), первые блоки умножения 6i (i=1,2,…m), четвертые сумматоры 7i (i=1,2,…m), четвертый регистр 8, третьи сумматоры 9j (j=1,2,…n), первые элементы задержки 10j, элементы 11j (j=1,2,…n), пятый сумматор 12, третий блок умножения 13, схему выбора максимального кода 14, третий регистр 15, шестой сумматор 16, второй элемент задержки 17, вход 18, выходы 19 и 20.

Устройство работает следующим образом.

В исходном состоянии (см. рис.1) на регистрах 1ij (i=1,2,…m, j=1,2,…n) находятся коды значений Psj/ai, на регистре 15 - код значения β, на регистре 8 - код значения Qp , на регистрах 3j (j=1,2,…n) коды значений wj, (j=1,2,…n). (Установочные входы на регистрах 1, 3, 8 и 15, на рис.1 не показаны).

Работа устройства начинается после подачи пускового сигнала на его вход 18, после чего этот сигнал поступает на управляющие входы блоков умножения 2ij (i=1,2,…m, j=1,2,…n). На выходе каждого блока умножения 2ij появляется код значения (Psj/ai*wj) как результат умножения значения Psj/ai на регистре 1ij со значением wj на регистре 3j. Коды с выходов блоков 2ij (i=1,2,…m, j=1,2,…n) поступают на одноименные входы вторых сумматоров 5i (i=1,2,…m). С выхода сумматора 5i инверсное значение суммы поступает на первый вход четвертого сумматора 7i (i=1,2,…m). Одновременно значение Psj/ai на регистре 1ij поступает на одноименный вход первого сумматора 4, (i=1,2,…m), с выхода которого значение суммы поступает на первый вход первого блока умножения 6i.

Элемент задержки 17 обеспечивает задержку входного сигнала на суммарное время надежного срабатывания блока умножения 2ij и сумматора 5i. С появлением сигнала задержки на выходе элемента 17 в блоке умножения 6i происходит умножение значения коэффициента β с выхода третьего регистра 15 на значение кода с выхода первого сумматора 4i (i=1,2,…m).

Также одновременно значение Qp с выхода четвертого регистра 8 поступает на первые входы третьих сумматоров 9j (j=1,2,…n), на второй вход которого поступает код с выхода второго регистра 3j. На сумматоре 9j вычисляется значение (Qp-wj), которое поступает на вход группы элементов задержки 10j. Элемент 10j задерживает сигнал на время надежного срабатывания сумматора 9j. На втором выходе сумматора 9j (j=1,2,…n) появляется единичный сигнал в случае, если значение (Qp-wj), (j=1,2,…n) будет положительным, и нулевой сигнал в случае, если значение (Qp-wj) будет нулевым или отрицательным. Сигнал со второго выхода сумматора 9j поступает на разрешающий вход группы элементов И 11j, на второй вход которого поступает код с выхода элемента задержки 10j . Код с выхода элемента И 11j поступает на одноименный вход пятого сумматора 12, с выхода которого код поступает на первый вход блока умножения 13.

Значение коэффициента β с выхода третьего регистра 15 поступает также на вход шестого сумматора 16, с выхода которого полученное значение (1-β) поступает на второй вход блока умножения 13, с выхода которого инверсный код поступает на третьи входы четвертых сумматоров 7j, выходы которых подсоединены к одноименным входам схемы выбора максимального кода 14.

На выходе четвертого сумматора 7i (i=1,2,…m) появляется значение .

На выходе схемы выбора максимального кода 14 появляется значение максимального кода , а на выходе 19 появляется его порядковый номер i (i=1,…,m). Схема выбора максимального кода широко известна и может быть выполнена так, как описано в [2].

Литература

1. Патент 2335016. Устройство для моделирования системы защиты вычислительной сети. Опубл. 27.09.2007.

2. Авторское свидетельство 1128249. Устройство для выделения экстремального кода. Опубл. 08.08.1984.

Устройство для моделирования процесса принятия решения, содержащее матрицу m*n первых регистров 1ij (i=1,…,m,j=1,…,n), группу из n вторых 3j регистров, группу из m первых сумматоров 4i, группу из m первых блоков умножения 6i, третий 15 и четвертый регистры 8, шестой сумматор 16, отличающееся тем, что в него введены матрица m*n вторых блоков умножения 2ij (i=1,…,m,j=1,…,n), группа из m вторых сумматоров 5i, группа из n третьих сумматоров 9, группа из m четвертых сумматоров 7i, группа из n первых элементов задержки 10j, второй элемент задержки 17, группа из n элементов И 11j, пятый сумматор 12, третий блок умножения 13, блок выбора максимального кода 14, выход каждого регистра 1ij (i=1,…,m, j=1,…,n) подсоединен к одноименному входу первого сумматора 4i, и к первому входу второго блока умножения 2ij, второй вход которого подсоединен к выходу второго 3j регистра, вход устройства 18 подсоединен к третьему входу второго блока умножения 2ij и через второй элемент задержки 17 подсоединен к первым входам первых блоков умножения 6i (i=1,…,m), выход каждого первого сумматора 4i подсоединен во второму входу первого блока умножения 6i, выход каждого второго блока умножения 2ij подсоединен к одноименным входам вторых сумматоров 5i, выход которого подсоединен к первому входу четвертого сумматора 7i, второй вход которого подсоединен к выходу одноименного первого блока умножения 6i, выход четвертого регистра 8 подсоединен к первым входам третьих сумматоров 9j, второй вход которого подсоединен к выходу одноименного второго регистра 3j, первый выход третьего сумматора 9 через первый элемент задержки 10j подсоединен к первому входу группы элементов И 11j, второй вход которой подсоединен к второму выходу сумматора 9j, выход группы элементов И 11j подсоединен к одноименному входу пятого сумматора 12, выход которого подсоединен к первому входу третьего блока умножения 13, выход третьего регистра 15 подсоединен к третьим входам первых блоков умножения 6 и к входу шестого сумматора 16, выход которого подсоединен к второму входу третьего блока умножения 13, выход которого подсоединен к третьим входам четвертых сумматоров 7i, выход каждого из которых подсоединен к одноименным входам блока выбора максимального кода 14, на выходе 20 которого появляется максимальное значение кода, а на выходе 19 - его порядковый номер.