Вычитающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

246926

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №вЂ”

Кл. 42m>, 7/50

Заявлено 29.1Ч.1968 (№ 1237283/18-24) с присоединением заявки ¹â€”

Приоритет

Опубликовано 20.V1.1969. Бюллетень № 21

Дата опубликования описания 18.XI.1969

МПК С 061

УДК 681.325.54 (088.8) Комитет ло делам . изобретений и открытий ори Совете Министров

СССР

Автор изобретения

А, С. П риходь ко

Заявитель

ВЫЧИТАЮЩЕЕ УСТРОЙСТВО

Известны устройства для получения арифметической или алгебраической разности двух последовательностей электрических импульсов, используемые в электронных устройствах различного назначения.

Однако такие схемы требуют тщательной наладки и чувствительны к изменению режимов, так как в них используется принцип компенсации одних электрических импульсов другими.

Это снижает надежность устройства и усложняет его изготовление.

В предлагаемом вычитающем устройстве, более надежном и простом в изготовлении, каждая из вычитаемых последовательностей импульсов подается после дифференцирования на выход устройства через один из ключевых транзисторов, подсоединенных раздельно к выходам статического триггера. В базовую цепь каждого транзистора включена дифференцирующая цепочка, а входы триггера через интегрирующие цепочки связаны со входными шинами. Определение знака разности осуществляется путем инвертирования импульсов, поступающих на выход с одного из ключевых транзисторов, к выходу которого подсоединен инвертирующий каскад.

Схема, в которой информация передается только наличием импульса, а изменение величины его несущественно, обеспечивает создание импульсного вычитающего устройства, не требующего наладки, и нечувствительна к изменению в широких пределах электрических режимов схемы.

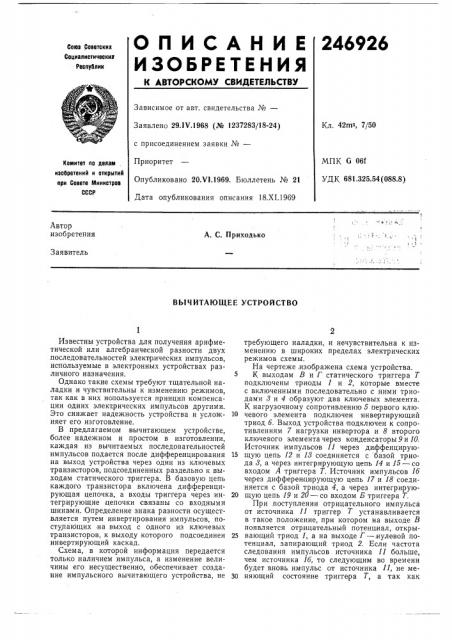

На чертеже, изображена схема устройства.

К выходам В и Г статического триггера Г подключены триоды 1 и 2, которые вместе с включенными последовательно с ними триодами 8 и 4 образуют два ключевых элемента.

К нагрузочному сопротивлению 5 первого клю-.

1О чевого элемента подключен инвертирующий триод б. Выход устройства подключен к сопротивлениям 7 нагрузки инвертора и 8 второго ключевого элемента через конденсаторы 9 и 10.

Источник импульсов 11 через диффенцирую15 щую цепь 12 и 18 соединяется с базой триода 3, а через интегрирующую цепь 14 и 15 — со входом А триггера Т. Источник импульсов lб через дифференцирующую цепь 17 и 18 соединяется с базой триода 4, а через интегрирую20 щую цепь 19 и 20 — со входом Б триггера Т.

При,поступлении отрицательного импульса от источника 11 триггер T устанавливается в такое положение, при котором на выходе Б появляется отрицательный потенциал, откры25 вающий триод 1, а на выходе à —,нулевой потенциал, запирающий триод 2. Если частота следования импульсов источника 11 больше, чем источника 1б, то следующим во времени будет вновь импульс от источника 11, не ме30 няющий состояние триггера Т, а так как

246926

Составитель Л. В. Скобелева

Редактор Б. С. Нанкина Техред Л. В. Куклина Корректоры: Е. Ласточкина и В. Петрова

Заказ 3001/17 Тираж 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 триод 1 открыт, то через триод 8 импульс после инвертирования поступает на выход устройства в отрицательной, полярности. Отрицательный импульс от источника 1б меняет состояние триггера Т так, что открывается триод 2 и закрывается триод 1. Интегрирующая цепь 19 и 20 задерживает изменение состояния триггера относительно момента поступления импульса через дифференцирующую цепь 17 и 18 на базу триода 4, а так как к этому моменту триод 2 закрыт, то импульс от источника 1б на выход устройства не проходит. Аналогично не проходит на выход устройства и следующий им пульс, постуг а ющий от источника 11.

Таким образом, если частоты следования импульсов от источников 11 и 1б равны, т. е. поступающие на входы А и Б импульсы чередуются, то на выход схемы не поступает ни одного импульса. Если же частоты следования различны, то на выход поступают только те им,пульсы, которые во времени поступают вслед за импульсом той же последовательности. Импульс же второй последовательности, поступающий вслед за импульсом первой последовательности, не только не проходит на выход, но и переводит трйтгер Т в такое состояние, при

Ф котором приходящий вслед за ним импульс первой последовательности также не поступает на выход устройства, чем и осуществЛяется вычитание. Знак, разности моделируется полярностью выходных импульсов. Если частота источника 11 больше, то на выходе импульсы разностной последовательности имеют отрицательную полярность, в противном случае — положительную.

Предмет изобретения

1. Вычитающее устройство для полученич алгебраической разности двух последовательностей импульсов, отличающееся тем, что, 15 с целью увеличения надежности, оно содержит статический триггер, к выходам которого подключены два ключевых транзистора, в базовую цепь каждого из которых включена дифференцирующая цепочка, а входы триггера че20 рез интегрирующие цепочки связаны со входными шинами.

2. Устройство по п. 1, отличающееся тем, что с целью определения знака разности, оно содержит инвертирующий каскад, подсоединен25 -ный к выходу одного из ключевых транзисторов.