Каскодный дифференциальный усилитель

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении предельных значений коэффициента усиления по напряжению каскодного дифференциального усилителя при малом напряжении питания. Каскодный дифференциальный усилитель, содержащий первый и второй входные транзисторы, базы которых подключены к первому входу устройства, третий и четвертый входные транзисторы, базы которых подключены ко второму входу устройства, первый токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого, второго, третьего и четвертого входных транзисторов и первой шиной источника питания, первый и второй выходные транзисторы, первый и второй вспомогательные транзисторы, эмиттеры которых через второй токостабилизирующий двухполюсник связаны с первой шиной источника питания, база первого вспомогательного транзистора соединена с коллектором второго входного транзистора и первым выводом первого вспомогательного резистора, база второго вспомогательного транзистора соединена с коллектором третьего входного транзистора и первым выводом второго вспомогательного резистора, первый и второй двухполюсники нагрузки, вторую шину источника питания, причем вторые выводы первого и второго вспомогательных резисторов подключены к дополнительному источнику питания. 2 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, SiGe-операционных усилителях, СВЧ-усилителях, компараторах, непрерывных стабилизаторах напряжения и т.п.).

В современной микроэлектронике находят применение классические каскодные дифференциальные усилители (КДУ) с двумя резисторами в коллекторной цепи выходных транзисторов [1-11]. Данная архитектура является основой широкого класса аналоговых (аналогово-цифровых) устройств и является базовой как для традиционных, так и для новых технологий.

Наиболее близким по технической сущности к заявляемому устройству является каскодный дифференциальный усилитель по патенту US №7.400.196, fig.3.

Существенный недостаток известного КДУ, архитектура которого присутствует также в других усилительных каскадах [1-11], состоит в том, что при ограничениях на напряжение питания (Еп), характерных для SiGe технологических процессов (Еп≤2,0÷2,5 B), его коэффициент усиления по напряжению (Ку) получается небольшим (Куmax=10÷20). В первую очередь это обусловлено ограничениями на сопротивления резисторов коллекторной нагрузки, которые из-за малых Еп не могут выбираться высокоомными. Поэтому для повышения Ку иногда применяются так называемые «динамические нагрузки» (ДН), например на биполярных транзисторах, которые требуют для обеспечения своего линейного режима работы «потери» статического напряжения UДН=0,8÷1,6 В между шиной источника питания и выходом ДН. Причем численные значения UДН равны 0,8 B для простейших динамических нагрузок, имеющих, к сожалению, невысокое выходное сопротивление:

где UЭрли - напряжение Эрли выходного p-n-р-транзистора ДН;

Iэ=I0 - статический ток эмиттера p-n-р-выходного транзистора ДН.

Для интегральных транзисторов UЭрли=20÷30 B. Следовательно, при I0=1 мА применение классических динамических нагрузок не позволяет получить высокие значения Ку. Более высокие выходные сопротивления RДН реализуются в токовых зеркалах Вильсона или каскодных схемах токовых зеркал. Однако они работают только в том случае, когда статическое напряжение Uдн между выводами такой динамической нагрузки более чем 2Uэб≥1,6 B. При низковольтном питании это не приемлемо. Кроме этого, не все техпроцессы (например, внедряемый в России SGB25VD) допускают использование p-n-р-транзисторов. Для других, например, радиационно-стойких технологий (НПО «Интеграл» г.Минск), применение p-n-p-транзисторов не рекомендуется в условиях радиационного воздействия на микроэлектронное изделие.

Таким образом, при малых напряжениях питания, а особенно в тех случаях, когда требуется получить более-менее значительные амплитуды выходного напряжения, известные схемотехнические решения КДУ неэффективны.

Основная задача предполагаемого изобретения состоит в повышении предельных значений коэффициента усиления по напряжению КДУ при малом напряжении питания.

Поставленная задача решается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 входу устройства, третий 4 и четвертый 5 входные транзисторы, базы которых подключены ко второму 6 входу устройства, первый 7 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого 1, второго 2, третьего 4 и четвертого 5 входных транзисторов и первой 8 шиной источника питания, первый 9 и второй 10 выходные транзисторы, первый 11 и второй 12 вспомогательные транзисторы, эмиттеры которых через второй 13 токостабилизирующий двухполюсник связаны с первой 8 шиной источника питания, база первого 11 вспомогательного транзистора соединена с коллектором второго 2 входного транзистора и первым выводом первого 14 вспомогательного резистора, база второго 12 вспомогательного транзистора соединена с коллектором третьего 4 входного транзистора и первым выводом второго 15 вспомогательного резистора, первый 16 и второй 17 двухполюсники нагрузки, вторую 18 шину источника питания, предусмотрены новые элементы и связи - коллектор первого 1 входного транзистора соединен с эмиттером первого 9 выходного транзистора и коллектором второго 12 вспомогательного транзистора, коллектор четвертого 5 входного транзистора соединен с эмиттером второго 10 выходного транзистора и коллектором первого 11 вспомогательного транзистора, базы первого 9 и второго 10 выходных транзисторов соединены с шиной вспомогательного источника питания 19, коллектор первого 9 выходного транзистора связан с первым 20 выходом устройства и через первый 16 двухполюсник нагрузки подключен ко второй 18 шине источника питания, коллектор второго 10 выходного транзистора связан со вторым 21 выходом устройства и через второй 17 двухполюсник нагрузки подключен ко второй 18 шине источника питания, причем вторые выводы первого 14 и второго 15 вспомогательных резисторов подключены к дополнительному источнику питания 22.

На фиг.1 показана схема КДУ-прототипа.

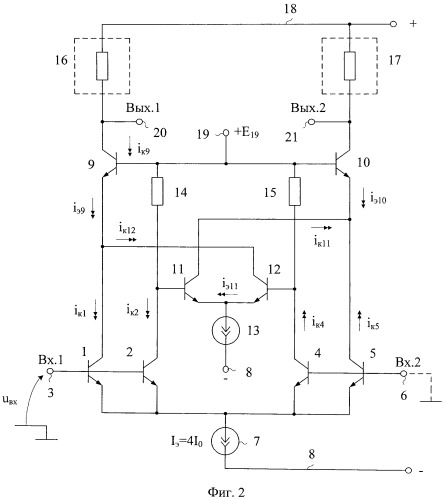

На фиг.2 показана схема заявляемого устройства, соответствующего п.1 и п.2 формулы изобретения.

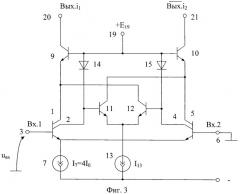

На фиг.3 показана схема КДУ фиг.2 для случая, когда элементы 14 и 15 реализованы в виде р-n переходов.

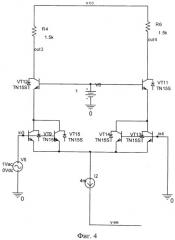

На фиг.4 показана схема КДУ-прототипа в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.5 показана схема заявляемого КДУ в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

График фиг.6 характеризует частотные зависимости коэффициента усиления по напряжению (Ку) КДУ фиг.4 и фиг.5, полученные в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.7 представлена зависимость коэффициента усиления КДУ фиг.5 от тока второго 13 токостабилизирующего двухполюсника I13=I3 (фиг.5) на частоте f=1 МГц.

Каскодный дифференциальный усилитель (фиг.2) содержит первый 1 и второй 2 входные транзисторы, базы которых подключены к первому 3 входу устройства, третий 4 и четвертый 5 входные транзисторы, базы которых подключены ко второму 6 входу устройства, первый 7 токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого 1, второго 2, третьего 4 и четвертого 5 входных транзисторов и первой 8 шиной источника питания, первый 9 и второй 10 выходные транзисторы, первый 11 и второй 12 вспомогательные транзисторы, эмиттеры которых через второй 13 токостабилизирующий двухполюсник связаны с первой 8 шиной источника питания, база первого 11 вспомогательного транзистора соединена с коллектором второго 2 входного транзистора и первым выводом первого 14 вспомогательного резистора, база второго 12 вспомогательного транзистора соединена с коллектором третьего 4 входного транзистора и первым выводом второго 15 вспомогательного резистора, первый 16 и второй 17 двухполюсники нагрузки, вторую 18 шину источника питания. Коллектор первого 1 входного транзистора соединен с эмиттером первого 9 выходного транзистора и коллектором второго 12 вспомогательного транзистора, коллектор четвертого 5 входного транзистора соединен с эмиттером второго 10 выходного транзистора и коллектором первого 11 вспомогательного транзистора, базы первого 9 и второго 10 выходных транзисторов соединены с шиной вспомогательного источника питания 19, коллектор первого 9 выходного транзистора связан с первым 20 выходом устройства и через первый 16 двухполюсник нагрузки подключен ко второй 18 шине источника питания, коллектор второго 10 выходного транзистора связан со вторым 21 выходом устройства и через второй 17 двухполюсник нагрузки подключен ко второй 18 шине источника питания, причем вторые выводы первого 14 и второго 15 вспомогательных резисторов подключены к дополнительному источнику питания 22.

На фиг.2 входной дифференциальный каскад 1 реализован на транзисторах 1-2 и 4-15, статический режим которых устанавливается первым 7 токостабилизирующим двухполюсником. Выходной дифференциальный каскод реализован на транзисторах 9 и 10, статический режим которых по цепи базы устанавливается вспомогательным источником питания 19 (Е19). Коллекторная нагрузка КДУ реализована на резисторах 16 и 17, связанных со второй 18 шиной положительного источника питания.

Рассмотрим работу ДУ фиг.2 на переменном токе.

Приращения коллекторных токов транзисторов 1÷5 в схеме фиг.2 зависят от входного напряжения:

где - сопротивления эмиттерных переходов транзисторов 1-5;

φт=25 мВ - температурный потенциал.

Ток iк2 (iк4) создает на резисторах 14 и 15 переменное напряжение:

В результате между базами транзисторов 11 и 12 образуется приращение напряжений:

которое преобразуется в коллекторные токи транзисторов 11 и 12:

Таким образом, приращение эмиттерного (коллекторного) тока транзистора 9:

или после преобразований:

Следовательно, коэффициент усиления по напряжению заявляемого КДУ относительно выхода Вых.1:

Если выбрать I13=2I0, I7=4I0, то

При реальных значениях параметров последнюю формулу можно упростить:

Когда I0=1 мА, R16=R14=1 кОм, из (6)-(10) получаем, что Ку≈400. Это значительно лучше, чем в ДУ-прототипе.

Данные теоретические выводы подтверждаются результатами компьютерного моделирования (фиг.6, фиг.7). Данные графики показывают, что предлагаемый усилитель имеет более чем в 10 раз лучшее усиление, которое может изменяться за счет тока второго 13 токостабилизирующего двухполюсника I13=I3.

Заявляемая схема особенно перспективна для использования в микроэлектронных SiGe изделиях СВЧ-устройств.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US №2007/0188232

2. Патент США №5.461.342, fig.1

3. Патент США №7.236.011, fig.4

4. Патент UK №1.520.085, кл. НЗТ, fig.2

5. Патент США №3.482.177

6. Патент DE№2.418.455

7. Патент RU №2.282.303, fig.2

8. Патент США №5.568.092, fig.1

9. Патент США №5.440.271, fig.1

10. Ю.С.Ежков. Справочник по схемотехнике усилителей. Изд. 2-е. М.: РадиоСофт, 2002. - С.142, рис.6.64.

11. Ю.С.Ежков. Справочник по схемотехнике усилителей. Изд. 2-е. М.: РадиоСофт, 2002. - С.227, рис.8.51.

1. Каскодный дифференциальный усилитель, содержащий первый (1) и второй (2) входные транзисторы, базы которых подключены к первому (3) входу устройства, третий (4) и четвертый (5) входные транзисторы, базы которых подключены ко второму (6) входу устройства, первый (7) токостабилизирующий двухполюсник, включенный между объединенными эмиттерами первого (1), второго (2), третьего (4) и четвертого (5) входных транзисторов и первой (8) шиной источника питания, первый (9) и второй (10) выходные транзисторы, первый (11) и второй (12) вспомогательные транзисторы, эмиттеры которых через второй (13) токостабилизирующий двухполюсник связаны с первой (8) шиной источника питания, база первого (11) вспомогательного транзистора соединена с коллектором второго (2) входного транзистора и первым выводом первого (14) вспомогательного резистора, база второго (12) вспомогательного транзистора соединена с коллектором третьего (4) входного транзистора и первым выводом второго (15) вспомогательного резистора, первый (16) и второй (17) двухполюсники нагрузки, вторую (18) шину источника питания, отличающийся тем, что коллектор первого (1) входного транзистора соединен с эмиттером первого (9) выходного транзистора и коллектором второго (12) вспомогательного транзистора, коллектор четвертого (5) входного транзистора соединен с эмиттером второго (10) выходного транзистора и коллектором первого (11) вспомогательного транзистора, базы первого (9) и второго (10) выходных транзисторов соединены с шиной вспомогательного источника питания (19), коллектор первого (9) выходного транзистора связан с первым (20) выходом устройства и через первый (16) двухполюсник нагрузки подключен ко второй (18) шине источника питания, коллектор второго (10) выходного транзистора связан со вторым (21) выходом устройства и через второй (17) двухполюсник нагрузки подключен ко второй (18) шине источника питания, причем вторые выводы первого (14) и второго (15) вспомогательных резисторов подключены к дополнительному источнику питания (22).

2. Каскодный дифференциальный усилитель по п.1, отличающийся тем, что в качестве дополнительного источника питания (22) используется шина вспомогательного источника питания (19).

3. Каскодный дифференциальный усилитель по п.1, отличающийся тем, в качестве дополнительного источника питания (22) используется вторая (18) шина источника питания.