Статическая запоминающая ячейка с двумя адресными входами

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в повышении помехоустойчивости. Статическая запоминающая ячейка с двумя адресными входами на МОП-транзисторах состоит из триггера, двух ключей выборки и логического элемента «И», управляющего ключами, причем триггер состоит из первого и второго МОП-транзисторов с n-каналом и третьего и четвертого МОП-транзисторов с р-каналом, при этом содержит дополнительную общую шину триггеров, к которой подключены истоки первого и второго МОП-транзисторов, причем потенциал общей шины триггеров выше, чем потенциал общей шины ячейки. 3 ил.

Реферат

Изобретение относится к области радиотехники и может быть использовано при построении массива памяти интегрального статического запоминающего устройства, выполненного на базе КМОП технологии.

Известна статическая запоминающая ячейка с двумя адресными входами (US 7768816 В2, МПК G11C 11/00, опубл. 11.06.2009, US 7355906 В2, МПК G11C 7/00, опубл. 29.11.2007), ключи выборки которой составлены из двух последовательно соединенных МОП-транзисторов, управляемых с различных адресных входов. Данная структура позволяет обеспечить выборку по словам и столбцам без включения в состав ячейки дополнительного логического элемента «И». Однако ограничение минимальной величины напряжения порога переключения в режиме записи накладывает ограничение на минимальную ширину МОП-транзисторов ключей выборки, что приводит к увеличению площади ячейки и увеличению входных емкостей адресных входов.

Известна статическая запоминающая ячейка с двумя адресными входами (US 2007/0025162 А1, МПК G11C 11/00, G11C 5/14, опубл. 01.02.2007), в которой напряжения на узлах питания инверторов изменяются в зависимости от режима работы при помощи внешнего источника питания. Данная структура позволяет увеличить статическую устойчивость ячейки в режиме чтения и независимо от этого повысить порог переключения в режиме записи. Однако из-за процессов перезаряда емкостей шин питания при смене режима, а также применения управляемых источников питания увеличивается энергопотребление устройства памяти.

Известна статическая запоминающая ячейка с двумя адресными входами (US 7768816 В2, МПК G11C 11/00, опубл. 11.06.2009, US 7355906 В2, МПК G11C 7/00, опубл. 29.11.2007), представляющая шеститранзисторную ячейку, МОП-транзисторы ключей выборки которой управляются с помощью логического элемента «И», выполненного на двух n-канальных и одном р-канальном МОП-транзисторах, подключенного к адресным входам. Данная структура позволяет уменьшить площадь, занимаемую МОП-транзисторами ключей выборки, а также уменьшить входные емкости адресных входов. Однако ограничение минимальной величины напряжения порога переключения в режиме записи накладывает ограничения на статическую устойчивость ячейки в режиме чтения, что приводит к увеличению вероятности битовых ошибок.

Известна статическая запоминающая ячейка с двумя адресными входами (US 2010/0080045 А1, МПК G11C 11/00, опубл. 01.04.2010), представляющая шеститранзисторную ячейку, МОП-транзисторы ключей выборки которой управляются с помощью логического элемента «И», выполненного на двух n-канальных МОП-транзисторах, подключенного к адресным входам. Данная структура позволяет уменьшить площадь, занимаемую логическим элементом «И». Однако ограничение минимальной величины напряжения порога переключения в режиме записи ухудшает статическую устойчивость ячейки в режиме чтения, что приводит к увеличению вероятности битовых ошибок.

По наибольшему числу признаков за ближайший аналог (прототип) предлагаемого устройства выбрана статическая запоминающая ячейка с двумя адресными входами, описанная в US 2010/0080045 А1, МПК G11C 11/00, опубл. 01.04.2010, Фиг.2.

Статическая запоминающая ячейка с двумя адресными входами состоит из триггера, двух ключей выборки, логического элемента «И», управляющего ключами, и дополнительно введенной общей шины триггеров, потенциал которой выше потенциала общей шины ячейки. Триггер построен на основе двух КМОП-инверторов. К выходным узлам инверторов, а также к разрядным шинам подключены ключи выборки, выполненные на основе n-канальных МОП-транзисторов. Логический элемент «И» состоит из двух n-канальных МОП-транзисторов, один из которых включен между выходным узлом логического элемента и общей шиной ячейки, а другой - между выходным узлом логического элемента и первой адресной шиной. Затворы МОП-транзисторов, составляющих логический элемент, подключены к проводникам второй адресной шины, причем логические уровни на проводниках и, следовательно, на затворах попарно-инверсные. Выходной узел логического элемента подключен к затворам n-канальных МОП-транзисторов, образующих ключи выборки. Истоки р-канальных МОП-транзисторов из состава инверторов соединены с шиной питания. Истоки n-канальных МОП-транзисторов из состава инверторов соединены с общей шиной триггеров.

При описанном подключении истоков n-канальных МОП-транзисторов из состава инверторов к дополнительной шине с потенциалом, повышенным по сравнению с общей шиной, увеличение статической устойчивости ячейки в режиме чтения достигается за счет уменьшения напряжения затвор-исток МОП-транзисторов ключей выборки, что приводит к увеличению их сопротивления в открытом состоянии. При этом уменьшения порога переключения триггера в режиме записи не происходит, что связано с увеличением напряжения переключения инверторов относительно нулевого логического уровня на разрядных шинах. Однако при этом уменьшается разрядный ток ячейки, что приводит к уменьшению амплитуды полезного сигнала на разрядных шинах в режиме чтения. При стандартной КМОП-технологии с минимальным разрешением 0.18-мкм запас статической устойчивости ячейки в режиме чтения составляет, как правило, от 300 до 400 мВ.

Задачей изобретения является увеличение статической устойчивости ячейки в режиме чтения без уменьшения напряжения порога переключения в режиме записи за счет введения дополнительной общей шины триггеров, потенциал которой выше потенциала общей шины ячейки.

Сущность предлагаемого технического решения заключается в том, что аналогично прототипу статическая запоминающая ячейка с двумя адресными входами состоит из триггера, двух ключей выборки и логического элемента «И», управляющего ключами. Триггер построен на двух КМОП-инверторах, причем к узлу, в котором соединяются стоки МОП-транзисторов одного из инверторов, подключены затворы МОП-транзисторов другого инвертора, и наоборот. Истоки n-канальных МОП-транзисторов из состава инверторов подключены к дополнительно введенной в состав ячейки общей шине триггера, истоки р-канальных МОП-транзисторов из состава инверторов подключены к шине питания. Истоки МОП-транзисторов, образующих ключи выборки, подключены к стокам инверторов из состава триггера, причем к стокам МОП-транзисторов из состава одного инвертора подключен один транзистор. Стоки МОП-транзисторов, образующих ключи выборки, подключены к разрядным шинам, причем к одной шине подключен один транзистор. Затворы МОП-транзисторов, образующих ключи выборки, соединены между собой и подключены к узлу, который является выходом логического элемента «И». Логический элемент «И» состоит из двух n-канальных МОП-транзисторов. Причем сток первого из них подключен к узлу, который является выходом логического элемента «И», а исток - к общей шине ячейки. Исток второго МОП-транзистора подключен к узлу, который является выходом логического элемента «И», а сток - к первой адресной шине. Затворы МОП-транзисторов, составляющих логический элемент, подключены к проводникам второй адресной шины, причем логические уровни на проводниках и, следовательно, на затворах попарно-инверсные. В отличие от прототипа истоки n-канальных МОП-транзисторов из состава инверторов триггера подключены к дополнительно введенной в состав ячейки общей шине триггеров, потенциал которой выше, чем потенциал общей шины ячейки.

Подключение истоков n-канальных МОП-транзисторов из состава инверторов в отличие от прототипа не на общую шину ячейки, а к дополнительной общей шине триггеров приводит к увеличению потенциала нулевого логического уровня на выходе инверторов, а также к увеличению напряжения порога переключения инверторов относительно общей шины ячейки.

В режиме чтения из-за увеличения потенциала нулевого логического уровня на выходе инверторов происходит уменьшение напряжения затвор-исток МОП-транзисторов ключей выборки, что приводит к увеличению их сопротивления в открытом состоянии. Открытый МОП-транзистор ключа выборки совместно с открытым n-канальным МОП-транзистором из состава инвертора образуют делитель напряжения. Уменьшение напряжения между разрядной шиной, заряженной до потенциала высокого логического уровня, и общей шиной триггеров, а также увеличение сопротивления МОП-транзистора ключа выборки в открытом состоянии приводит к уменьшению падения напряжения на открытом n-канальном МОП-транзисторе из состава инвертора. В результате увеличивается разница между напряжением сток-исток данного МОП-транзистора и напряжением затвор-исток второго n-канального МОП-транзистора из состава триггера, при котором происходит переключение триггера в противоположное состояние. Данная разница напряжений определяет запас статической устойчивости ячейки.

В режиме записи открытый МОП-транзистор ключа выборки совместно с открытым р-канальным МОП-транзистором из состава инвертора образуют делитель напряжения. Сопротивление МОП-транзистора ключа выборки определяется напряжением затвор-сток, то есть разностью потенциалов между затвором и разрядной шиной, и не зависит от потенциала общей шины триггеров. Сопротивление р-канального МОП-транзистора определяется напряжением затвор-исток, то есть разностью потенциалов между общей шиной триггеров и шиной питания, и увеличивается с увеличением потенциала общей шины триггеров. Следовательно, с увеличением потенциала общей шины триггеров увеличивается напряжение исток-сток р-канального МОП-транзистора. При этом также увеличивается напряжение порога переключения инверторов относительно общей шины ячейки, что приводит к увеличению порога переключения ячейки в режиме записи.

Сущность изобретения иллюстрируется следующими графическими материалами.

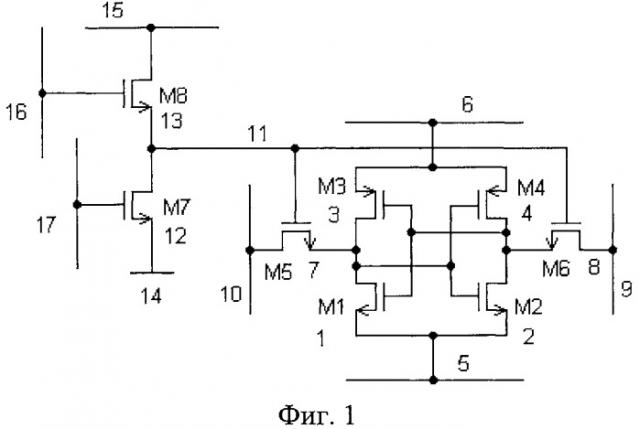

Схема статической запоминающей ячейки с двумя адресными входами показана на фиг.1, на которой приняты следующие обозначения: 1 - первый МОП-транзистор M1, 2 - второй МОП-транзистор М2, 3 - третий МОП-транзистор М3, 4 - четвертый МОП-транзистор М4, 5 - общая шина триггеров, 6 - шина питания, 7 - пятый МОП-транзистор М5, 8 - шестой МОП-транзистор М6, 9 - первая разрядная шина, 10 - вторая разрядная шина, 11 - выход логического элемента «И», 12 - седьмой МОП-транзистор М7, 13 - восьмой МОП-транзистор М8, 14 - общая шина ячейки, 15 - первая адресная шина, 16 - неинвертирующий разряд второй адресной шины, 17 - инвертирующий разряд второй адресной шины.

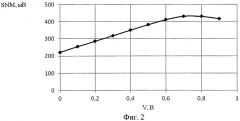

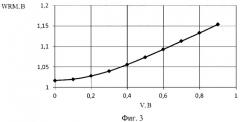

На фиг.2. показана зависимость запаса статической устойчивости в режиме чтения от напряжения на общей шине триггеров - SNM. На фиг.3. показана зависимость напряжения порога переключения ячейки в режиме записи от напряжения на общей шине триггеров - WRM.

Статическая запоминающая ячейка с двумя адресными входами состоит из триггера, двух ключей выборки, логического элемента «И» и дополнительно введенной общей шины триггеров, потенциал которой выше потенциала общей шины ячейки. Триггер построен на первом (1), втором (2), третьем (3) и четвертом (4) МОП-транзисторах. Истоки первого (1) и второго (2) МОП-транзисторов подключены к общей шине триггеров (5), истоки третьего (3) и четвертого (4) МОП-транзисторов подключены к шине питания (6). Затворы первого и третьего МОП-транзисторов соединены между собой и подключены к стокам четвертого и второго МОП-транзисторов, а затворы четвертого и второго МОП-транзисторов соединены между собой и подключены к стокам первого и третьего МОП-транзисторов. Исток пятого МОП-транзистора (7), образующего первый ключ выборки, подключен к соединенным между собой стокам первого (1) и третьего (3) МОП-транзисторов, а исток шестого МОП-транзистора (8), образующего второй ключ выборки, подключен к соединенным между собой стокам второго (2) и четвертого (4) МОП-транзисторов. Стоки шестого и пятого МОП-транзисторов подключены к первой (9) и ко второй (10) разрядным шинам соответственно. Затворы пятого (7) и шестого (8) МОП-транзисторов соединены между собой и подключены к узлу (11), который является выходом логического элемента «И». Логический элемент «И» состоит из седьмого (12) и восьмого (13) МОП-транзисторов. Причем сток седьмого МОП-транзистора (12) подключен к выходу логического элемента «И» (11), а исток - к общей шине ячейки (14). Исток восьмого МОП-транзистора (13) подключен к выходу логического элемента «И» (11), а сток - к первой адресной шине (15). Затворы седьмого и восьмого МОП-транзисторов, составляющих логический элемент, подключены к проводникам второй адресной шины (16) и (17), причем затвор восьмого транзистора подключен к неинвертирующему разряду (16) второй адресной шины, а затвор седьмого транзистора подключен к инвертирующему разряду (17).

Ячейка работает следующим образом.

В режимах записи и чтения на первую адресную шину (15) и неинвертирующий разряд второй адресной шины (16) поступают сигналы высокого логического уровня, а на инвертирующий разряд второй адресной шины (17) поступает сигнал низкого логического уровня. В результате седьмой МОП-транзистор (12) переходит в режим отсечки, а восьмой МОП-транзистор (13) переходит в режим инверсии. При этом первая адресная шина (15) через канал восьмого МОП-транзистора (13) соединяется с выходным узлом (11) логического элемента «И», что приводит к появлению напряжения высокого логического уровня на затворах пятого (7) и шестого (8) МОП-транзисторов. Предположим далее, что на истоке пятого МОП-транзистора (7) присутствует потенциал, равный потенциалу шины питания, а на истоке шестого МОП-транзистора (8) присутствует потенциал, равный потенциалу общей шины триггеров (5). Тогда, в режиме чтения разрядные шины заряжены до напряжения высокого уровня. Из-за того что напряжение затвор-исток шестого МОП-транзистора (8) превышает пороговое напряжение отпирания, возникает ток, протекающий через каналы второго (2) и шестого (8) МОП-транзисторов, разряжающий первую разрядную шину (9) до потенциала общей шины триггеров (5). Напряжения затвор-исток и затвор-сток пятого МОП-транзистора (7) не превышают порогового напряжения отпирания, в результате пятый МОП-транзистор находится в режиме отсечки и вторая разрядная шина (10) сохраняет заряд. В режиме записи при смене состояния ячейки на первой разрядной шине (9) присутствует напряжение высокого, а на второй разрядной шине (10) - напряжение низкого уровня. Из-за того что напряжение затвор-сток пятого МОП-транзистора (7) превышает пороговое напряжение отпирания, возникает ток, протекающий через каналы третьего (3) и пятого (7) МОП-транзисторов. В результате потенциал стока третьего МОП-транзистора (3) оказывается ниже напряжения порога области активного режима инверторов, возникает положительная обратная связь, и триггер изменяет состояние на противоположное.

Для подтверждения работоспособности проведено моделирование ячейки.

Результаты моделирования схемы, выполненной с использованием типовых параметров КМОП-технологии с минимальным разрешением 0.18 мкм при напряжении на первой адресной шине 1.8 В, напряжении на неинвертирующем разряде второй адресной шины 1.8 В, напряжении на инвертирующем разряде второй адресной шины 0 В, напряжении на шине питания 1.8 В приведены на фиг.2 и фиг.3. Напряжения указаны относительно уровня общей шины ячейки и соответствуют стандартному варианту включения ячеек памяти. Напряжение на общей шине триггеров изменялось от 0 до 0.9 В. На фиг.2 показана зависимость запаса статической устойчивости в режиме чтения от напряжения на общей шине триггеров при напряжении 1.8 В на обеих разрядных шинах. На фиг.3 показана зависимость напряжения порога переключения ячейки в режиме записи от напряжения на общей шине триггеров при напряжении 1.8 В на первой разрядной шине и при линейном изменении напряжения на второй разрядной шине от 1.8 В до 0 за 50 нс. Подложки n-канальных МОП-транзисторов подключены к общей шине ячейки. Подложки р-канальных МОП-транзисторов подключены к шине питания. Из результатов моделирования видно, что запас статической устойчивости в режиме чтения увеличился в два раза, при этом напряжение порога переключения ячейки в режиме записи существенно не изменилось (увеличилось на 10%).

Статическая запоминающая ячейка с двумя адресными входами на МОП-транзисторах, состоящая из триггера, двух ключей выборки и логического элемента «И», управляющего ключами, причем триггер состоит из первого и второго МОП-транзисторов с n-каналом и третьего и четвертого МОП-транзисторов с р-каналом, при этом истоки первого и второго МОП-транзисторов соединены с общей шиной триггеров, истоки третьего и четвертого МОП-транзисторов соединены с шиной питания, стоки третьего и первого МОП-транзисторов соединены с затворами четвертого и второго МОП-транзисторов, стоки четвертого и второго МОП-транзисторов соединены с затворами третьего и первого МОП-транзисторов; ключи собраны на пятом и шестом МОП транзисторах с n-каналом, причем исток пятого МОП-транзистора подключен к стоку третьего МОП-транзистора, исток шестого МОП-транзистора подключен к стоку четвертого МОП-транзистора, сток шестого МОП-транзистора подключен к первой разрядной шине, сток пятого МОП-транзистора подключен ко второй разрядной шине, затворы пятого и шестого МОП-транзисторов подключены к стоку седьмого МОП-транзистора; элемент «И» состоит из седьмого и восьмого МОП-транзисторов с n-каналом, причем исток седьмого МОП-транзистора подключен к общей шине ячейки, сток седьмого МОП-транзистора подключен к истоку восьмого МОП-транзистора, сток восьмого МОП-транзистора подключен к первой адресной шине, затвор седьмого МОП-транзистора подключен к инвертирующему разряду второй адресной шины, затвор восьмого МОП-транзистора подключен к неинвертирующему разряду второй адресной шины, отличающаяся тем, что содержит дополнительную общую шину триггеров, к которой подключены истоки первого и второго МОП-транзисторов, причем потенциал общей шины триггеров выше, чем потенциал общей шины ячейки.