Многоканальный преобразователь аналоговых сигналов в импульсную последовательность, модулированную по времени

Иллюстрации

Показать всеИзобретение относится к многоканальным системам преобразования и передачи информации с уплотнением по времени и может быть использовано в измерительной технике и устройствах связи. Техническим результатом является увеличение информативности устройства и расширение динамического диапазона измеряемых параметров. Устройство содержит аналого-цифровой преобразователь, двоичный n-разрядный счетчик, формирователь время-импульсной последовательности, триггер, логический элемент «И», двоичный р-разрядный счетчик, многоканальный коммутатор, программируемый модуль памяти, кодоуправляемый усилитель, ячейку управления режимом работы, два цифро-аналоговых преобразователя, операционный усилитель, контроллер, включающий в себя генератор тактовой частоты с кварцевой стабилизацией, умножитель частоты и распределитель тактовых импульсов. 3 ил.

Реферат

Изобретение относится к многоканальным системам преобразования и передачи информации с уплотнением по времени и может быть использовано в измерительной технике и устройствах связи.

Известно устройство «Преобразователь аналоговых сигналов в импульсную последовательность, модулированную по времени» (см. патент РФ №2377721, опубликован 27.12.2009), содержащее многоканальный коммутатор, контроллер, включающий последовательно соединенные генератор тактовой частоты с кварцевой стабилизацией и распределитель тактовых импульсов, первый выход которого соединен с первым входом триггера, выход которого соединен с первым входом логического элемента «И», второй вход которого соединен со вторым выходом генератора тактовой частоты, а выход логического элемента «И» соединен со счетным входом двоичного n-разрядного счетчика, выход которого соединен со вторым входом триггера и первым входом формирователя измерительных импульсов, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом формирователя опорных импульсов, вход которого соединен со вторым выходом распределителя тактовых импульсов, третий выход которого соединен с пусковым входом аналого-цифрового преобразователя, цифровые выходы которого соединены с входами двоичного счетчика соответственно, вход управления параллельной загрузки которого соединен с выходом «готовность данных» аналого-цифрового преобразователя, выход сумматора соединен со входом усилителя мощности, кодоуправляемый усилитель, программируемый модуль памяти и двоичный p-разрядный счетчик, выходы которого соединены с цифровыми входами многоканального коммутатора и программируемого модуля памяти, выходы которого соединены со входами кодоуправляемого усилителя, вход которого соединен с выходом многоканального коммутатора, а выход соединен с аналоговым входом аналого-цифрового преобразователя, выход «готовность данных» которого соединен со счетным входом двоичного p-разрядного счетчика, вход программируемого модуля памяти является входом данных.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбрано в качестве прототипа.

Недостатками устройства являются низкая информативность, вызванная низкой частотой генератора тактовой частоты, что не позволяет использовать данное устройство в системах с быстро изменяющимися процессами, а также его незащищенность от наличия и дрейфа начальных уровней входных аналоговых сигналов, приводящая к снижению динамического диапазона измеряемого параметра и возможной потере информации, что приводит к ограничению выбора типа датчика.

Задачей, на решение которой направлено заявленное изобретение, является создание многоканального преобразователя аналоговых сигналов в импульсную последовательность, модулированную по времени, позволяющего существенно увеличить информативность устройства и расширить динамический диапазон измеряемых параметров.

Достигаемым техническим результатом является возможность использования устройства в системах с быстро изменяющимися процессами и снижение начального уровня входных сигналов и его дрейфа до допустимых величин путем автоматической их компенсации.

Для достижения технического результата в многоканальном преобразователе аналоговых сигналов в импульсную последовательность, модулированную по времени, содержащем аналого-цифровой преобразователь, цифровые выходы которого соединены с входами двоичного n-разрядного счетчика соответственно, выход которого соединен с первыми входами формирователя время-импульсной последовательности и триггера, выход которого соединен с первым входом логического элемента «И», выход которого соединен с первым входом двоичного n-разрядного счетчика, второй вход которого соединен с выходом аналого-цифрового преобразователя и с входом двоичного p-разрядного счетчика, выход переполнения которого соединен со вторым входом формирователя время-импульсной последовательности, выход которого является выходом устройства, счетные выходы двоичного p-разрядного счетчика соединены с цифровыми входами многоканального коммутатора и с входами p-разрядного регистра программируемого модуля памяти, вход которого является шиной ввода исходных данных, а выходы q-разрядного регистра соединены с цифровыми входами кодоуправляемого усилителя, выход которого соединен с первым входом аналого-цифрового преобразователя, контроллер, включающий в себя генератор тактовой частоты с кварцевой стабилизацией и распределитель тактовых импульсов, первый и второй выходы которого соединены со вторым входом аналого-цифрового преобразователя и с третьим входом формирователя время-импульсной последовательности соответственно, а третий выход соединен со вторым входом триггера, новым является то, что дополнительно введены ячейка управления режимом работы, первый и второй цифро-аналоговые преобразователи, операционный усилитель, выход которого соединен с первым входом кодоуправляемого усилителя, второй вход которого соединен с выходом первого цифро-аналогового преобразователя, входы которого соединены с выходами f-разрядного регистра программируемого модуля памяти, выходы r-разрядного регистра которого соединены с входами второго цифро-аналогового преобразователя, выход которого соединен с первым входом операционного усилителя, второй вход которого соединен с выходом многоканального коммутатора, аналоговые входы которого являются входами устройства, цифровые выходы аналого-цифрового преобразователя соединены с входами n-разрядного регистра программируемого модуля памяти, первый и второй входы которого соединены соответственно со вторым входом двоичного n-разрядного счетчика и с выходом ячейки управления режимом работы, группа входов которой является входами внешних управляющих команд, а вход соединен с третьим входом формирователя время-импульсной последовательности, при этом в контроллер дополнительно введен умножитель частоты, первый выход которого соединен с входом распределителя тактовых импульсов, второй выход соединен со вторым входом логического элемента «И», а вход соединен с выходом генератора тактовой частоты с кварцевой стабилизацией.

Введение в заявляемое устройство ячейки управления режимом работы, двух цифро-аналоговых преобразователей, операционного усилителя и умножителя частоты позволяет увеличить частоту опроса входных сигналов, что приводит к повышению информативности устройства, и ведет к снижению величины начальных уровней и их дрейфа до допустимых значений путем автоматической их компенсации.

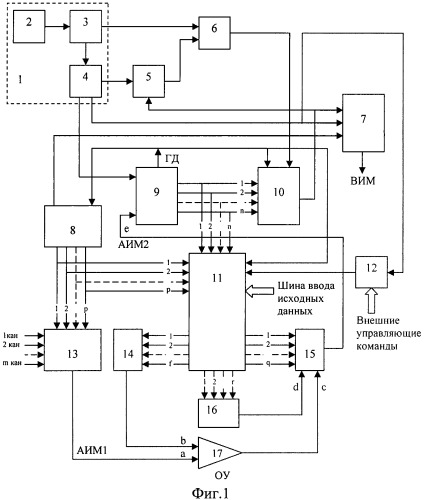

На фигуре 1 приведена схема предлагаемого устройства.

На фигуре 2 приведена иллюстрация принципа действия компенсации величины нулевых уровней и их дрейфа.

На фигуре 3 приведена временная диаграмма работы многоканального преобразователя аналоговых сигналов в импульсную последовательность, модулированную по времени.

Многоканальный преобразователь аналоговых сигналов в импульсную последовательность, модулированную по времени, содержит аналого-цифровой преобразователь (АЦП) 9, цифровые выходы которого соединены с входами двоичного n-разрядного счетчика 10 соответственно, выход переполнения которого соединен с первыми входами формирователя время-импульсной последовательности 7 и триггера 5, выход которого соединен с первым входом логического элемента «И» 6, выход которого соединен с первым входом двоичного n-разрядного счетчика 10, второй вход которого соединен с выходом АЦП 9 и с входом двоичного p-разрядного счетчика 8, выход переполнения которого соединен со вторым входом формирователя время-импульсной последовательности 7, выход которого является выходом устройства, счетные выходы двоичного p-разрядного счетчика 8 соединены с цифровыми входами многоканального коммутатора 13 и с входами p-разрядного регистра программируемого модуля памяти (ПМП) 11, вход которого является шиной ввода исходных данных, а выходы q-разрядного регистра соединены с цифровыми входами кодоуправляемого усилителя 15, выход которого соединен с первым входом АЦП 9, контроллер 1, включающий в себя генератор тактовой частоты с кварцевой стабилизацией 2 и распределитель тактовых импульсов 4, первый и второй выходы которого соединены со вторым входом АЦП 9 и с третьим входом формирователя время-импульсной последовательности 7 соответственно, а третий выход соединен со вторым входом триггера 5, ячейку управления режимом работы 12, первый 16 и второй 14 цифро-аналоговые преобразователи (ЦАП), операционный усилитель (ОУ) 17, выход которого соединен с первым входом кодоуправляемого усилителя 15, второй вход которого соединен с выходом первого ЦАП 16, входы которого соединены с выходами r-разрядного регистра ПМП 11, выходы f-разрядного регистра которого соединены со входами второго ЦАП 14, выход которого соединен с первым входом ОУ, второй вход которого соединен с выходом многоканального коммутатора 13, аналоговые входы которого являются входами устройства, цифровые выходы АЦП 9 соединены с входами n-разрядного регистра ПМП 11, первый и второй входы которого соединены соответственно со вторым входом двоичного n-разрядного счетчика 10 и с выходом ячейки управления режимом работы 12, группа входов которой является входами внешних управляющих команд, а вход соединен с третьим входом формирователя время-импульсной последовательности 7, умножитель частоты 3, первый выход которого соединен с входом распределителя тактовых импульсов 4, второй выход соединен со вторым входом логического элемента «И» 6, а вход соединен с выходом генератора тактовой частоты с кварцевой стабилизацией 2.

Заявляемое устройство работает следующим образом. Работа осуществляется в двух режимах.

1 режим - «Компенсация отключена».

2 режим - «Компенсация включена».

Выбор режима работы осуществляется внешними управляющими командами, например подачей или снятием питания со второго входа ячейки управления режимом работы.

Перед началом работы в программируемый модуль памяти заносится информация о значениях коэффициента усиления и начального уровня для каждого измерительного канала.

В режиме «Компенсация отключена» генератор тактовой частоты с кварцевой стабилизацией 2 вырабатывает высокостабилизированную серию импульсов, которая умножается на определенный коэффициент в умножителе частоты 3 и с выходов распределителя тактовых импульсов 4 в виде управляющих серий импульсов поступает на соответствующие входы функциональных элементов устройства, в том числе на вход тактирования АЦП 9, в котором происходит преобразование аналоговых сигналов в соответствующий цифровой код с выдачей сигнала «готовность данных» на выходе ГД АЦП 9 по окончании преобразования. При появлении сигнала с вышеуказанного выхода происходит запись со стиранием предыдущего значения n-разрядного двоичного кода с цифровых выходов АЦП 9 через входной n-разрядный регистр в ячейку памяти ПМП 11, соответствующую i-тому каналу, и параллельная загрузка этого кода в двоичный n-разрядный счетчик 10 для дальнейшего формирования измерительного импульса i-того канала («i» есть число от 1 до m). На выходе двоичного p-разрядного счетчика 8 устанавливается соответствующий i+1-му каналу код, который поступает на входной p-разрядный регистр ПМП 11 и на цифровые входы многоканального коммутатора 13, устанавливая на его аналоговом выходе и соответственно на неинвертирующем входе операционного усилителя 17 АИМ1 i+1-го измерительного канала. На выходном q-разрядном регистре ПМП 11 и цифровых входах кодоуправляемого усилителя 15 устанавливается код коэффициента усиления i+1-го канала. На выходном f-разрядном регистре ПМП 11 и на цифровых входах ЦАП 14 устанавливается код значения начального уровня i+1-го канала, при этом на аналоговом выходе ОУ 17 и на неинвертирующем входе кодоуправляемого усилителя 15 устанавливается напряжение, равное ∆Uдр (см. фиг.2). На выходном r-разрядном регистре ПМП 11 и на цифровых входах ЦАП 16 устанавливается код, соответствующий нулевому значению его выходного напряжения, при этом на выходе кодоуправляемого усилителя 15 и на аналоговом входе АЦП 9 устанавливается напряжение, равное АИМ2=∆Uдр×Ккус (см. фиг.2). При поступлении очередного тактового импульса с распределителя тактовых импульсов 4 на пусковой вход АЦП 9 начинается преобразование АИМ i+1-го канала в соответствующий цифровой код. После окончания преобразования на выходе ГД АЦП 9 появляется сигнал «готовность данных» и повторяется описанный выше алгоритм, только для i+1-го и i+2-го каналов и так далее.

Таким образом, устройство работает в циклическом режиме, последовательно преобразуя аналоговую информацию каждого измерительного канала в цифровой код и далее в импульсную последовательность, модулированную по времени.

В режиме «компенсация включена» по внешней управляющей команде устройство переходит в режим работы с включенной компенсацией. При этом ячейка управления режимом работы 12 запрещает запись двоичного n-разрядного кода с цифровых выходов АЦП 9 в ячейки памяти ПМП 11. Прекращение записи синхронизировано с ближайшим тактовым импульсом с распределителя тактовых импульсов 4. Дальнейшая работа, как правило, кратковременная, происходит по описанному выше алгоритму, при этом используются значения кодов компенсации начального уровня, записанные в соответствующие ячейки памяти ПМП 11 до включения режима компенсации. Эти коды устанавливаются на выходном r-разрядном регистре ПМП 11 и на цифровых входах ЦАП 16, при этом на аналоговом выходе ЦАП 16 и на инвертирующем входе кодоуправляемого усилителя 15 устанавливается напряжение Uдр.

Таким образом, описание работы показывает, что заявляемый многоканальный преобразователь позволяет увеличить частоту опроса входных сигналов, а также уменьшить величины начальных уровней и их дрейфа до допустимых значений за счет автоматической их компенсации.

В целях подтверждения осуществимости заявляемого объекта и достижения технического результата изготовлен и испытан лабораторный макет многоканального преобразователя аналоговых сигналов в импульсную последовательность, модулированную по времени с умножителем частоты и с автоматической компенсацией величины начальных уровней и их дрейфа, выполненный по приведенной на фиг.1 схеме.

Проведенные испытания показали осуществимость заявляемого многоканального преобразователя и подтвердили существенное повышение информативности устройства и расширение динамического диапазона измеряемого параметра.

Многоканальный преобразователь аналоговых сигналов в импульсную последовательность, модулированную по времени, содержащий аналого-цифровой преобразователь, цифровые выходы которого соединены с входами двоичного n-разрядного счетчика соответственно, выход которого соединен с первыми входами формирователя время-импульсной последовательности и триггера, выход которого соединен с первым входом логического элемента «И», выход которого соединен с первым входом двоичного n-разрядного счетчика, второй вход которого соединен с выходом аналого-цифрового преобразователя и с входом двоичного р-разрядного счетчика, выход переполнения которого соединен со вторым входом формирователя время-импульсной последовательности, выход которого является выходом устройства, счетные выходы двоичного р-разрядного счетчика соединены с цифровыми входами многоканального коммутатора и с входами р-разрядного регистра программируемого модуля памяти, вход которого является шиной ввода исходных данных, а выходы q-разрядного регистра соединены с цифровыми входами кодоуправляемого усилителя, выход которого соединен с первым входом аналого-цифрового преобразователя, контроллер, включающий в себя генератор тактовой частоты с кварцевой стабилизацией и распределитель тактовых импульсов, первый и второй выходы которого соединены со вторым входом аналого-цифрового преобразователя и с третьим входом формирователя время-импульсной последовательности соответственно, а третий выход соединен со вторым входом триггера, отличающийся тем, что дополнительно введены ячейка управления режимом работы, первый и второй цифроаналоговые преобразователи, операционный усилитель, выход которого соединен с первым входом кодоуправляемого усилителя, второй вход которого соединен с выходом первого цифроаналогового преобразователя, входы которого соединены с выходами r-разрядного регистра программируемого модуля памяти, выходы f-разрядного регистра которого соединены со входами второго цифроаналогового преобразователя, выход которого соединен с первым входом операционного усилителя, второй вход которого соединен с выходом многоканального коммутатора, аналоговые входы которого являются входами устройства, цифровые выходы аналого-цифрового преобразователя соединены с входами n-разрядного регистра программируемого модуля памяти, первый и второй входы которого соединены соответственно со вторым входом двоичного n-разрядного счетчика и с выходом ячейки управления режимом работы, группа входов которой является входами внешних управляющих команд, а вход соединен с третьим входом формирователя время-импульсной последовательности, при этом в контроллер дополнительно введен умножитель частоты, первый выход которого соединен с входом распределителя тактовых импульсов, второй выход соединен со вторым входом логического элемента «И», а вход соединен с выходом генератора тактовой частоты с кварцевой стабилизацией.