Схема возбуждения для линий сканирующего сигнала, сдвиговый регистр и способ возбуждения сдвигового регистра

Иллюстрации

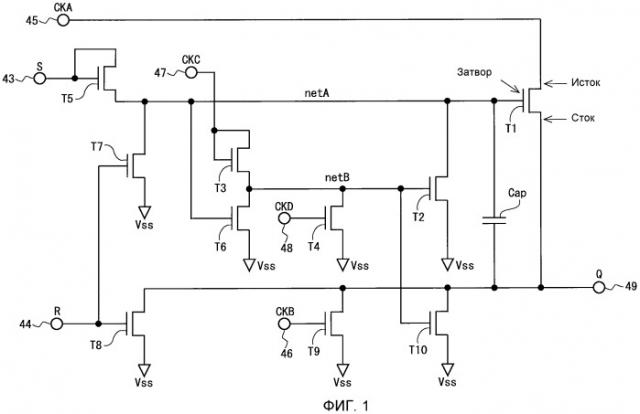

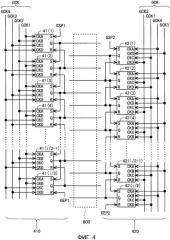

Показать всеИзобретение относится к устройствам отображения, а именно к схеме возбуждения для линий сканирующего сигнала (в). Техническим результатом является подавление излишнего потребления мощности из-за тока утечки в тонкопленочном транзисторе, в случае, когда схема в сдвиговом регистре формируется с использованием тонкопленочного транзистора, который имеет относительно большую утечку в закрытом состоянии. Результат достигается тем, что каждая бистабильная схема, которая формирует сдвиговый регистр, включает в себя тонкопленочный транзистор (Т1) для повышения потенциала выходного контакта (49) на основании первого синхроимпульса, область netA, подключенную к контакту затвора тонкопленочного транзистора (Т1), тонкопленочный транзистор (Т2) для понижения потенциала области netA, и область netB, подключенную к контакту затвора тонкопленочного транзистора (Т2). В этой конфигурации потенциал области netB повышается на основании третьего синхроимпульса, который опережает по фазе на 90 градусов первый синхроимпульс, и понижается на основании четвертого синхроимпульса, который запаздывает по фазе на 90 градусов относительно первого синхроимпульса. 4 н. и 23 з.п. ф-лы, 19 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение имеет отношение к схеме возбуждения и к способу возбуждения для устройства отображения с активной матрицей. Конкретнее, изобретение имеет отношение к сдвиговому регистру в схеме возбуждения для линий сканирующего сигнала, который возбуждает линии сканирующего сигнала, размещенные на участке отображения в устройстве отображения с активной матрицей, и к способу его возбуждения.

Уровень техники

Жидкокристаллические устройства отображения, использующие тонкопленочные транзисторы на основе аморфного кремния (a-Si) (именуемые в дальнейшем “a-Si TFT” - amorphous silicon thin film transistor) в качестве элементов возбудителя, известны достаточно хорошо. В последние годы на первый план выдвигается развитие жидкокристаллических устройств отображения, использующих тонкопленочные транзисторы на основе микрокристаллического кремния (именуемые в дальнейшем “µc-Si TFT”) в качестве элементов возбудителя. Подвижность микрокристаллического кремния больше, чем подвижность аморфного кремния, и µc-Si TFT могут формироваться посредством технологического процесса, подобного технологическому процессу для a-Si TFT. По этой причине, можно рассчитывать, что применение µc-Si TFT в качестве элементов возбудителя принесет, например, снижение затрат за счет сокращения площади кадра и уменьшения числа кристаллов в ИС возбудителя, повышение монтажной производительности, а также увеличение размеров устройств отображения. Дополнительно, µc-Si TFT обладают такой характерной особенностью, что пороговый сдвиг (изменение порогового напряжения), когда напряжение прикладывается к электроду затвора в течение длительного периода времени, меньше порогового сдвига для a-Si TFT. Другими словами, µc-Si TFT надежнее, чем a-Si TFT, в том смысле, что µc-Si TFT невосприимчивы к деградации.

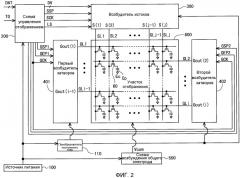

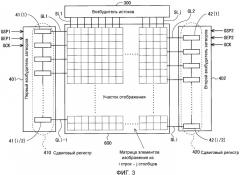

Между прочим, модуль отображения жидкокристаллического устройства отображения с активной матрицей включает в себя множество линий шин истоков (линий видеосигнала), множество линий шин затворов (линий сканирующего сигнала), а также множество участков формирования элементов изображения, соответственно, предусмотренных на пересечениях множества линий шин истоков и множества линий шин затворов. Эти участки формирования элементов изображения размещаются в матрице для создания массива элементов изображения. Каждый участок формирования элементов изображения включает в себя, например, тонкопленочный транзистор в качестве переключающего элемента, чей контакт затвора подключается к линии шины затвора, которая проходит через соответствующее пересечение, и чей контакт истока подключается к линии шины истока, которая проходит через соответствующее пересечение, и емкость элемента изображения для хранения значения элемента изображения. Дополнительно, такое жидкокристаллическое устройство отображения с активной матрицей снабжается возбудителем истоков (схемой возбуждения для линий видеосигнала) для возбуждения множества линий шин истоков и возбудителем затворов (схемой возбуждения для линий сканирующего сигнала) для возбуждения множества линий шин затворов.

Видеосигналы, указывающие значения элементов изображения, переносятся по линиям шин истоков. Однако невозможно одновременно (вместе) перенести видеосигналы, указывающие значения элементов изображения, для множества линий через единственную линию шины истока. По этой причине, видеосигналы записываются в емкости элементов изображения в участках формирования элементов изображения, размещенных в матрице последовательно построчно. Следовательно, возбудитель затвора конфигурируется сдвиговым регистром с множеством каскадов так, чтобы множество линий шин затворов последовательно выбирались в течение предварительно заданного периода.

Желательно, чтобы каждая линия шины затвора приводилась в выбранное состояние только один раз в одном кадровом периоде (в одном периоде горизонтального сканирования). Следовательно, предпочтительно, чтобы сканирующий сигнал, который прикладывается к каждой линии шины затвора, был с потенциалом на Высоком уровне только в течение периода, в котором каждая линия шины затвора будет установлена в выбранное состояние (в дальнейшем, именуется как “период с выбором”), и с заданным потенциалом на Низком уровне в период, отличный от периода с выбором (в дальнейшем, именуется как “период без выбора”). Однако потенциал сканирующего сигнала иногда изменяется в положительную сторону от потенциала на Низком уровне в периоде без выбора под влиянием паразитной емкости, образуемой на схеме, которая формирует сдвиговый регистр. Так, например, Выложенная Заявка на Патент Японии Номер 2006-351171 раскрывает изобретение, касающееся сдвигового регистра с возможностью снижения влияния, обусловленного паразитной емкостью, по сравнению с традиционным случаем. Фиг.15 является принципиальной схемой, демонстрирующей конфигурацию, соответствующую одному каскаду в сдвиговом регистре, раскрытом в Выложенной Заявке на Патент Японии Номер 2006-351171. В соответствии с этой схемой, на протяжении периода без выбора, линия шины затвора не переходит в высокоимпедансное состояние, а запирающее напряжение всегда подается на линию шины затвора. Считается, что это позволяет подавлять влияние, обусловленное паразитной емкостью.

ДОКУМЕНТ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

ПАТЕНТНЫЙ ДОКУМЕНТ

[Патентный документ 1] Выложенная Заявка на Патент Японии Номер 2006-351171

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Задачи, решаемые изобретением

При конфигурации, описанной выше, однако, как показано условным обозначением “c” на Фиг.16 (Фиг.9 в Выложенной Заявке на Патент Японии Номер 2006-351171), в периоде без выбора, потенциал сканирующего сигнала изменяется в положительную сторону от потенциала на Низком уровне из-за влияния паразитной емкости. В качестве причины этого рассматривается следующее. В Выложенной Заявке на Патент Японии Номер 2006-351171, внимание сосредоточено на паразитной емкости между линией шины затвора и общим электродом. Однако подобная паразитная емкость образуется также между электродами тонкопленочного транзистора в схеме, которая формирует сдвиговый регистр. Например, паразитная емкость образуется между затвором и истоком тонкопленочного транзистора, показанного условным обозначением T1 на Фиг.15. Поэтому, когда потенциал синхроимпульса LCLK1 изменяется с Низкого уровня на Высокий уровень, потенциал контакта затвора тонкопленочного транзистора T1 повышается вследствие паразитной емкости. В результате, ток утечки протекает через тонкопленочный транзистор T1, так что потенциал сканирующего сигнала изменяется. В данном документе, поскольку синхроимпульс LCLK1 устанавливается в состояние Высокого уровня в предварительно заданном цикле, даже в периоде без выбора, потенциал сканирующего сигнала изменяется в этом предварительно заданном цикле.

Как описано выше, когда потенциал сканирующего сигнала в периоде без выбора изменяется, излишний электрический ток протекает через линию шины затвора для передачи сканирующего сигнала. Например, в случае устройства отображения, на котором применяется панель WXGA, в каждый момент времени, только одна из 768 линий шин затворов будет установлена в выбранное состояние, а каждая из остальных 767 линий шин затворов будет установлена в невыбранное состояние. Другими словами, сканирующий сигнал, который прикладывается к каждой из этих 767 линий шин затворов, должен быть установлен на Низкий уровень. Однако, если ток утечки, описанный выше, генерируется в каждом каскаде сдвигового регистра, излишние электрические токи, соответствующие 767 линиям шин затвора, протекают через все устройство отображения. Следовательно, происходит излишнее потребление электроэнергии.

Более того, описанный выше µc-Si TFT имеет большую, чем a-Si TFT, утечку в закрытом состоянии (ток утечки, генерируемый в Закрытом состоянии). Таким образом, в случае применения µc-Si TFT для схемы, которая формирует сдвиговый регистр, излишнее потребление мощности из-за тока утечки становится большим, по сравнению со случаем применения a-Si TFT.

Задачей настоящего изобретения является реализация схемы возбуждения для линий сканирующего сигнала (в устройстве отображения), способной, даже в случае, когда схема в сдвиговом регистре формируется с использованием тонкопленочного транзистора, который имеет относительно большую утечку в закрытом состоянии, подавлять излишнее потребление мощности из-за тока утечки в тонкопленочном транзисторе.

Средство для решения задач

Первый аспект настоящего изобретения направлен на схему возбуждения для линий сканирующего сигнала устройства отображения, которая возбуждает множество линий сканирующего сигнала, размещенных на участке отображения, причем схема возбуждения для линий сканирующего сигнала содержит:

сдвиговый регистр, включающий в себя множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне, причем

каждая бистабильная схема включает в себя:

зарядный участок выходной узловой точки, включающий в себя первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала, причем этот зарядный участок выходной узловой точки устанавливает состояние, указанное сигналом состояния, в первое состояние;

разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние;

зарядный участок первой узловой точки для зарядки первой узловой точки, подключенной к первому электроду первого переключающего элемента, на основании предварительно заданного установочного сигнала;

первый разрядный участок первой узловой точки для разрядки первой узловой точки, причем этот первый разрядный участок первой узловой точки включает в себя второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал;

зарядный участок второй узловой точки для зарядки второй узловой точки, подключенной к первому электроду второго переключающего элемента, на основании третьего сигнала синхронизации; и

первый разрядный участок второй узловой точки для разрядки второй узловой точки, на основании четвертого сигнала синхронизации,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

в каждой бистабильной схеме,

зарядный участок второй узловой точки включает в себя третий переключающий элемент, имеющий первый электрод и второй электрод, на каждый из которых подается третий сигнал синхронизации, и третий электрод, подключенный ко второй узловой точке,

первый разрядный участок второй узловой точки включает в себя четвертый переключающий элемент, имеющий первый электрод, на который подается четвертый сигнал синхронизации, второй электрод, подключенный ко второй узловой точке, и третий электрод, на который подается предварительно заданный низкий потенциал, и

зарядный участок первой узловой точки включает в себя пятый переключающий элемент, имеющий первый электрод и третий электрод, на каждый из которых подается установочный сигнал, и второй электрод, подключенный к первой узловой точке.

Согласно третьему аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя:

второй разрядный участок второй узловой точки для разрядки второй узловой точки на основании зарядного напряжения первой узловой точки, причем этот второй разрядный участок второй узловой точки включает в себя шестой переключающий элемент, имеющий первый электрод, подключенный к первой узловой точке, второй электрод, подключенный ко второй узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

второй разрядный участок первой узловой точки для разрядки первой узловой точки на основании предварительно заданного сигнала сброса, причем этот второй разрядный участок первой узловой точки включает в себя седьмой переключающий элемент, имеющий первый электрод, по которому подается сигнал сброса, второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал.

Согласно четвертому аспекту настоящего изобретения, в третьем аспекте настоящего изобретения,

четырехфазные сигналы синхронизации формируются первой группой сигналов синхронизации, включающей в себя двухфазные сигналы синхронизации, которые подаются в качестве первого и второго сигналов синхронизации на каждую бистабильную схему, и второй группой сигналов синхронизации, включающей в себя двухфазные сигналы синхронизации, которые подаются в качестве третьего и четвертого сигналов синхронизации на каждую бистабильную схему, и

когда две соседние бистабильные схемы определяются как первая и вторая бистабильные схемы,

на первую бистабильную схему подается, в качестве первого сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав первой группы сигналов синхронизации, подается, в качестве второго сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав первой группы сигналов синхронизации, подается, в качестве третьего сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав второй группы сигналов синхронизации, подается, в качестве четвертого сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав второй группы сигналов синхронизации, и подается, в качестве сигнала сброса, сигнал состояния, выводимый от второй бистабильной схемы, и

на вторую бистабильную схему подается, в качестве первого сигнала синхронизации, сигнал, который подается в качестве второго сигнала синхронизации на первую бистабильную схему, подается, в качестве второго сигнала синхронизации, сигнал, который подается в качестве первого сигнала синхронизации на первую бистабильную схему, подается, в качестве третьего сигнала синхронизации, сигнал, который подается в качестве четвертого сигнала синхронизации на первую бистабильную схему, подается, в качестве четвертого сигнала синхронизации, сигнал, который подается в качестве третьего сигнала синхронизации на первую бистабильную схему, и подается, в качестве установочного сигнала, сигнал состояния, выводимый от первой бистабильной схемы.

Согласно пятому аспекту настоящего изобретения, в четвертом аспекте настоящего изобретения,

сигнальная линия, передающая первую группу сигналов синхронизации, является большей по ширине, чем сигнальная линия, передающая вторую группу сигналов синхронизации.

Согласно шестому аспекту настоящего изобретения, в третьем аспекте настоящего изобретения,

четырехфазные сигналы синхронизации формируются первым набором сигналов синхронизации и вторым набором сигналов синхронизации, каждый из которых включает в себя двухфазные сигналы синхронизации, сдвинутые по фазе на 180 градусов по отношению друг к другу, и

когда бистабильная схема, предшествующая некоторой одной из множества бистабильных схем, определяется как первая бистабильная схема, а бистабильная схема, следующая за этой некоторой бистабильной схемой, определяется как вторая бистабильная схема,

на первую бистабильную схему подается, в качестве первого сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав первого набора сигналов синхронизации, подается, в качестве второго сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав первого набора сигналов синхронизации, подается, в качестве третьего сигнала синхронизации, один из двухфазных сигналов синхронизации, входящих в состав второго набора сигналов синхронизации, подается, в качестве четвертого сигнала синхронизации, другой из двухфазных сигналов синхронизации, входящих в состав второго набора сигналов синхронизации, и подается, в качестве сигнала сброса, сигнал состояния, выводимый от второй бистабильной схемы, и

на вторую бистабильную схему подается, в качестве первого сигнала синхронизации, сигнал, который подается в качестве второго сигнала синхронизации на первую бистабильную схему, подается, в качестве второго сигнала синхронизации, сигнал, который подается в качестве первого сигнала синхронизации на первую бистабильную схему, подается, в качестве третьего сигнала синхронизации, сигнал, который подается в качестве четвертого сигнала синхронизации на первую бистабильную схему, подается, в качестве четвертого сигнала синхронизации, сигнал, который подается в качестве третьего сигнала синхронизации на первую бистабильную схему, и подается, в качестве установочного сигнала, сигнал состояния, выводимый от первой бистабильной схемы.

Согласно седьмому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

разрядный участок выходной узловой точки включает в себя:

первый разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние, на основании сигнала сброса, причем этот первый разрядный участок выходной узловой точки включает в себя восьмой переключающий элемент, имеющий первый электрод, на который подается сигналом сброса, второй электрод, подключенный к выходной узловой точке, и третий электрод, на который подается предварительно заданный низкий потенциал; и

второй разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние, на основании второго сигнала синхронизации, причем этот второй разрядный участок выходной узловой точки включает в себя девятый переключающий элемент, имеющий первый электрод, на который подается второй сигнал синхронизации, второй электрод, подключенный к выходной узловой точке, и третий электрод, на который подается предварительно заданный низкий потенциал.

Согласно восьмому аспекту настоящего изобретения, в седьмом аспекте настоящего изобретения,

разрядный участок выходной узловой точки дополнительно включает в себя третий разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние, на основании зарядного напряжения второй узловой точки, причем этот третий разрядный участок выходной узловой точки включает в себя десятый переключающий элемент, имеющий первый электрод, подключенный ко второй узловой точке, второй электрод, подключенный к выходной узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал.

Согласно девятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя конденсатор с одним концом, подключенным к первой узловой точке, и другим концом, подключенным к выходной узловой точке.

Согласно десятому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

третий сигнал синхронизации опережает по фазе на 90 градусов первый сигнал синхронизации.

Согласно одиннадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

схема возбуждения для линий сканирующего сигнала включает в себя

первую схему возбуждения для линий сканирующего сигнала для подачи сигнала состояния от одних концов на другие концы множества линий сканирующего сигнала, и

вторую схему возбуждения для линий сканирующего сигнала для подачи сигнала состояния от этих других концов на эти первые концы множества линий сканирующего сигнала.

Согласно двенадцатому аспекту настоящего изобретения, в одиннадцатом аспекте настоящего изобретения,

первая схема возбуждения для линий сканирующего сигнала подает сигнал состояния или на множество линий сканирующего сигнала на нечетных строках, или на множество линий сканирующего сигнала на четных строках, и

вторая схема возбуждения для линий сканирующего сигнала подает сигнал состояния на иное или множество линий сканирующего сигнала на нечетных строках, или множество линий сканирующего сигнала на четных строках.

Согласно тринадцатому аспекту настоящего изобретения, в одиннадцатом аспекте настоящего изобретения,

на каждую линию сканирующего сигнала подается сигнал состояния и от первой схемы возбуждения для линий сканирующего сигнала и от второй схемы возбуждения для линий сканирующего сигнала.

Согласно четырнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

переключающие элементы, входящие в состав каждой бистабильной схемы, представляют собой тонкопленочные транзисторы, сделанные из микрокристаллического кремния.

Согласно пятнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

переключающие элементы, входящие в состав каждой бистабильной схемы, представляют собой тонкопленочные транзисторы, сделанные из аморфного кремния.

Согласно шестнадцатому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

по меньшей мере, один из переключающих элементов, каждый из которых имеет второй электрод, подключенный к первой узловой точке, представляет собой тонкопленочный транзистор с многоканальной структурой.

Семнадцатый аспект настоящего изобретения направлен на устройство отображения, которое содержит:

участок отображения; и

схему возбуждения для линий сканирующего сигнала, которая возбуждает множество линий сканирующего сигнала, размещенных на участке отображения, при этом

схема возбуждения для линий сканирующего сигнала включает в себя сдвиговый регистр, включающий в себя множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне,

каждая бистабильная схема включает в себя:

зарядный участок выходной узловой точки, включающий в себя первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала, причем этот зарядный участок выходной узловой точки устанавливает состояние, указанное сигналом состояния, в первое состояние;

разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние;

зарядный участок первой узловой точки для зарядки первой узловой точки, подключенной к первому электроду первого переключающего элемента, на основании предварительно заданного установочного сигнала;

первый разрядный участок первой узловой точки для разрядки первой узловой точки, причем этот первый разрядный участок первой узловой точки включает в себя второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал;

зарядный участок второй узловой точки для зарядки второй узловой точки, подключенной к первому электроду второго переключающего элемента, на основании третьего сигнала синхронизации; и

первый разрядный участок второй узловой точки для разрядки второй узловой точки, на основании четвертого сигнала синхронизации,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Согласно восемнадцатому аспекту настоящего изобретения, в семнадцатом аспекте настоящего изобретения,

устройство отображения является возбудителем монолитного типа, в котором участок отображения и схема возбуждения для линий сканирующего сигнала формируются на единой подложке.

Девятнадцатый аспект настоящего изобретения направлен на сдвиговый регистр для возбуждения множества линий сканирующего сигнала, размещенных на участке отображения в устройстве отображения, при этом сдвиговый регистр содержит множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне, причем

каждая бистабильная схема включает в себя:

зарядный участок выходной узловой точки, включающий в себя первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала, причем этот зарядный участок выходной узловой точки устанавливает состояние, указанное сигналом состояния, в первое состояние;

разрядный участок выходной узловой точки для установки состояния, указанного сигналом состояния, во второе состояние;

зарядный участок первой узловой точки для зарядки первой узловой точки, подключенной к первому электроду первого переключающего элемента, на основании предварительно заданного установочного сигнала;

первый разрядный участок первой узловой точки для разрядки первой узловой точки, причем этот первый разрядный участок первой узловой точки включает в себя второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал;

зарядный участок второй узловой точки для зарядки второй узловой точки, подключенной к первому электроду второго переключающего элемента, на основании третьего сигнала синхронизации; и

первый разрядный участок второй узловой точки для разрядки второй узловой точки, на основании четвертого сигнала синхронизации,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Двадцатый аспект настоящего изобретения направлен на способ возбуждения для сдвигового регистра, для возбуждения множества линий сканирующего сигнала, размещенных на участке отображения в устройстве отображения, при этом сдвиговый регистр включает в себя множество бистабильных схем, каждая из которых обладает первым состоянием и вторым состоянием и подключается последовательно одна к другой, причем сдвиговый регистр устанавливает множество бистабильных схем последовательно в первое состояние, основываясь на четырехфазных сигналах синхронизации, которые вводятся извне и подаются в качестве первого, второго, третьего и четвертого сигналов синхронизации на соответствующие бистабильные схемы, при этом каждый из четырехфазных сигналов синхронизации циклически воспроизводит потенциал на Высоком уровне и потенциал на Низком уровне,

способ возбуждения содержит:

первый этап возбуждения, на котором переводят каждую бистабильную схему из второго состояния в первое состояние, поддерживают каждую бистабильную схему в первом состоянии в течение предварительно заданного периода, а затем переводят каждую бистабильную схему во второе состояние; и

второй этап возбуждения, на котором поддерживают каждую бистабильную схему во втором состоянии, и при этом

каждая бистабильная схема включает в себя:

выходную узловую точку, которая является узловой точкой для вывода сигнала состояния, указывающего либо первое состояние, либо второе состояние, и которая является узловой точкой, подключенной к линии сканирующего сигнала;

первый переключающий элемент, имеющий второй электрод, по которому подается первый сигнал синхронизации, и третий электрод, подключенный к выходной узловой точке;

первую узловую точку, подключенную к первому электроду первого переключающего элемента;

второй переключающий элемент, имеющий второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

вторую узловую точку, подключенную к первому электроду второго переключающего элемента,

первый этап возбуждения включает в себя:

этап зарядки первой узловой точки, на котором заряжают первую узловую точку, подавая предварительно заданный установочный сигнал на каждую бистабильную схему;

этап зарядки выходной узловой точки, на котором переводят состояние, указанное сигналом состояния, из второго состояния в первое состояние, изменяя потенциал первого сигнала синхронизации с Низкого уровня на Высокий уровень; и

первый этап разрядки выходной узловой точки, на котором переводят состояние, указанное сигналом состояния, из первого состояния во второе состояние, подавая предварительно заданный сигнал сброса на каждую бистабильную схему,

второй этап возбуждения включает в себя:

этап зарядки второй узловой точки, на котором заряжают вторую узловую точку, изменяя потенциал третьего сигнала синхронизации с Низкого уровня на Высокий уровень; и

первый этап разрядки второй узловой точки, на котором разряжают вторую узловую точку, изменяя потенциал четвертого сигнала синхронизации с Низкого уровня на Высокий уровень,

коэффициент заполнения, который является отношением периода, в течение которого поддерживается потенциал на Высоком уровне, к циклу, в котором потенциал на Высоком уровне и потенциал на Низком уровне повторяются в отношении каждого из четырехфазных сигналов синхронизации, устанавливается равным одной второй,

первый сигнал синхронизации и второй сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу,

третий сигнал синхронизации и четвертый сигнал синхронизации сдвинуты по фазе на 180 градусов по отношению друг к другу, и

третий сигнал синхронизации опережает по фазе первый сигнал синхронизации.

Согласно двадцать первому аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

каждая бистабильная схема дополнительно включает в себя:

третий переключающий элемент, имеющий первый электрод и второй электрод, на каждый из которых подается третий сигнал синхронизации, и третий электрод, подключенный ко второй узловой точке;

четвертый переключающий элемент, имеющий первый электрод, по которому подается четвертый сигнал синхронизации, второй электрод, подключенный ко второй узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

пятый переключающий элемент, имеющий первый электрод и третий электрод, на каждый из которых подается установочный сигнал, и второй электрод, подключенный к первой узловой точке,

на этапе зарядки второй узловой точки, вторая узловая точка заряжается таким образом, что третий переключающий элемент устанавливается в Открытое состояние, на основании третьего сигнала синхронизации,

на первом этапе разрядки второй узловой точки, вторая узловая точка разряжается таким образом, что четвертый переключающий элемент устанавливается в Открытое состояние, на основании четвертого сигнала синхронизации, и

на этапе зарядки первой узловой точки, первая узловая точка заряжается таким образом, что пятый переключающий элемент устанавливается в Открытое состояние, на основании установочного сигнала.

Согласно двадцать второму аспекту настоящего изобретения, в двадцатом аспекте настоящего изобретения,

первый этап возбуждения дополнительно включает в себя:

второй этап разрядки второй узловой точки, на котором разряжают вторую узловую точку, на основании зарядного напряжения первой узловой точки; и

второй этап разрядки первой узловой точки, на котором разряжают первую узловую точку, на основании сигнала сброса,

каждая бистабильная схема дополнительно включает в себя:

шестой переключающий элемент, имеющий первый электрод, подключенный к первой узловой точке, второй электрод, подключенный ко второй узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал; и

седьмой переключающий элемент, имеющий первый электрод, по которому подается сигнал сброса, второй электрод, подключенный к первой узловой точке, и третий электрод, по которому подается предварительно заданный низкий потенциал,

на втором этапе разрядки второй узловой точки, вторая узловая точка разряжается таким образом, что шестой переключающий элемент устанавливается в Открытое состояние, на основании зарядного напряжения первой узловой точки, и

на втором этапе разрядки первой узловой точки, первая узловая точка разряжается таким образом, что седьмой переключаю