Селектор импульсов

Иллюстрации

Показать всеИзобретение относится к области импульсной техники, в частности к селекторам по периоду следования. Технический результат - повышение надежности функционирования селектора в условиях воздействия помех. Технический результат достигается тем, что в условиях действия помех при отсутствии входного импульса в стробе формируется дополнительный строб-импульс, положение которого определяется по предшествующему интервалу появления входного импульса, т.е. в предположении, что последний принятый импульс являлся помехой. Селектор импульсов содержит: блок выделения первого импульса, три схемы ИЛИ, три счетчика, два блока формирования стробов, четыре схемы И, два пересчетных блока, генератор, триггер, шифратор, сдвигатель кодов, два сумматора, два регистра и коммутатор с соответствующими связями. 1 ил.

Реферат

Изобретение относится к области импульсной техники, в частности к селекторам по периоду следования, и может быть использовано в аппаратуре полуактивных головок самонаведения для выделения сигналов на фоне помех.

Известен селектор (патент №2073953, кл. Н03К 5/26 от 04.11.93 г.), содержащий последовательно соединенные блок выделения первого импульса, первый элемент «НЕ», первый элемент «ИЛИ», элемент задержки, первый формирователь строба, второй элемент «ИЛИ», первый и второй элементы «И», последовательно соединенные схему перезапуска, счетчик непопаданий, счетчик попаданий, второй элемент «НЕ», второй формирователь строба и третий элемент «ИЛИ», а также устройство регулируемой задержки. Выход блока выделения первого импульса соединен со вторыми входами формирователя стробов и блока перезапуска, выход первого элемента «НЕ» соединен со вторым входом второго элемента «ИЛИ», выход первого формирователя стробов соединен с третьим входом схемы перезапуска, выход второго элемента «ИЛИ» соединен со вторыми входами счетчика попаданий и устройства регулируемой задержки, выход первого элемента «И» соединен с третьими входами счетчика попаданий и схемы регулируемой задержки, первыми входами схемы перезапуска и блока выделения первого импульса и вторыми входами счетчика непопаданий и первого элемента «ИЛИ». Выход схемы перезапуска соединен с первыми входами счетчика непопаданий и блока выделения первого импульса. Выход счетчика попаданий соединен с четвертым входом схемы перезапуска, первым входом устройства регулируемой задержки и вторым входом второго элемента «И». Выход устройства регулируемой задержки соединен со вторым входом второго формирователя стробов, а выход третьего элемента «ИЛИ» - со вторым входом второго элемента «И».

Наиболее близким по технической сущности к предлагаемому является селектор импульсов по периоду следования (авторское свидетельство №1758864, кл. Н03К 5/26 от 11.03.90 г.), содержащий линию задержки, блок выделения первого импульса, три элемента «И», триггер, элемент «ИЛИ», элемент задержки, блок формирования стробов, пересчетный блок, причем блок выделения первого импульса, элемент «ИЛИ», элемент задержки, блок формирования стробов, третий элемент «И» соединены последовательно, выход третьего элемента «И» подключен к первому входу пересчетного блока, выходу селектора и вторым входам блока формирования стробов и элемента «ИЛИ», второй вход третьего элемента «И» соединен со входом селектора и первыми входами блока выделения первого импульса, первого элемента «И» и линии задержки, линия задержки, первый и третий элементы «И» соединены последовательно, выход триггера соединен со вторым входом второго элемента «И», а первый вход триггера - с выходом второго элемента «И» и третьим входом элемента «ИЛИ», четвертый вход элемента «ИЛИ» соединен с выходом элемента задержки, второй вход которого подключен ко вторым входам линии задержки, блока выделения первого импульса, триггера и выходу пересчетного блока, второй вход пересчетного блока соединен с выходом, а второй выход - с третьим входом блока формирования стробов. Линия задержки содержит генератор тактовых импульсов, второй и третий триггеры, счетчик импульсов, первый и второй запоминающие блоки и второй элемент ИЛИ, выход которого соединен с выходом линии задержки, а первый и второй входы - с выходами соответственно первого и второго запоминающих блоков, адресные входы которых поразрядно соединены с выходами счетчиков импульсов, входы управления режимом запись-считывание - соответственно с первым и вторым выходами третьего триггера, а информационные входы - с выходом второго триггера, вход установки которого соединен с первым входом линии задержки, второй вход которой соединен с входами сброса первого и второго запоминающих блоков и счетчика импульсов, счетный вход которого соединен с выходом генератора тактовых импульсов и входом сброса второго триггера, а выход переполнения - со счетным входом третьего триггера.

Недостатком вышеуказанных селекторов является то, что при наличии внутренних или внешних помех возможно их попадание внутрь стробируемого интервала, приводящее к ошибке определения положения следующего входного импульса и, как следствие, к потере входного импульса. При этом указанные селекторы переходят в режим возобновления поиска входных сигналов на заданной литерной частоте, что приводит к потере части выходных импульсов.

Задачей предлагаемого изобретения является повышение надежности функционирования селектора в условиях воздействия помех.

Указанная задача достигается тем, что в селектор импульсов, содержащий последовательно соединенные блок выделения первого импульса, первую схему ИЛИ, первый счетчик и первый блок формирования стробов, последовательно соединенные первую схему И и первый пересчетный блок, последовательно соединенные генератор и второй счетчик, а также триггер, вторую, третью схемы И, вторую схему ИЛИ, причем выход первой схемы И, являющийся выходом селектора импульсов соединен с вторым входом первой схемы ИЛИ, вход селектора импульсов соединен с первыми входами блока выделения первого импульса и первой схемы И, введены последовательно соединенные шифратор, сдвигатель кодов, первый сумматор, третий счетчик, второй блок формирования стробов, четвертая схема И и третья схема ИЛИ, последовательно соединенные первый регистр, второй сумматор и коммутатор, последовательно соединенные второй пересчетный блок и второй регистр, причем выход первого пересчетного блока соединен с первыми входами второй схемы И и шифратора, а также с вторыми входами коммутатора и второго счетчика, выход триггера соединен с первыми входами третьей схемы И и второго пересчетного блока и вторыми входами шифратора, сдвигателя кодов и четвертой схемы И, выход первой схемы И соединен с первым входом триггера и вторыми входами третьей схемы ИЛИ, первого и второго регистров и третьего счетчика, выход первого блока формирователя стробов соединен с вторыми входами второй и третьей схем И, второго пересчетного блока и триггера и первым входом второй схемы ИЛИ, выход второй схемы И соединен с вторыми входами блока выделения первого импульса и первого пересчетного блока, выход третьей схемы И соединен с третьими входами первой схемы ИЛИ и второго пересчетного блока, выход шифратора соединен с вторыми входами первого и второго блоков формирования стробов, выход генератора соединен с третьим входом третьего счетчика и вторым входом первого счетчика, выход коммутатора соединен с третьим входом первого счетчика, а четвертый вход коммутатора является входом кода литерной частоты, выход первого регистра соединен с третьим входом второго регистра, выход которого соединен с вторым входом первого сумматора, второй выход второго пересчетного блока соединен с вторым входом первого регистра, выход третьей схемы ИЛИ соединен с четвертым входом третьего счетчика, выход четвертой схемы И соединен с вторым входом второй схемы ИЛИ, выход второго счетчика соединен с третьим входом первого регистра, выход сдвигателя кодов соединен с вторым входом второго сумматора, а выход второй схемы ИЛИ соединен с вторым входом первой схемы И.

Технический результат достигается тем, что в условиях действия помех при отсутствии входного импульса в стробе формируется дополнительный строб-импульс, положение которого определяется по предшествующему интервалу появления входного импульса, т.е. в предположении, что последний принятый импульс являлся помехой.

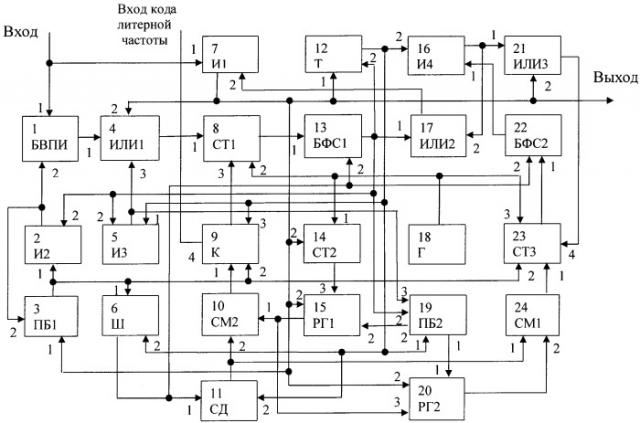

На фиг. приведена структурная схема селектора, где

1 - блок выделения первого импульса (БВПИ),

2, 5, 7, 16 - схема И (И2, И3, И1, И4 соответственно),

3, 19 - пересчетный блок (ПБ1, ПБ2 соответственно),

8, 14, 23 - счетчики (СТ1, СТ2, СТ3 соответственно),

4, 17, 21 - схема ИЛИ (ИЛИ 1, ИЛИ2, ИЛИ3 соответственно),

6 - шифратор (Ш),

9 - коммутатор (К),

10, 24 - сумматор (СМ2, СМ1 соответственно),

11 - сдвигатель кодов (СД),

12 - триггер (Т),

13, 22 - блок формирования строба (БФС1, БФС2),

15, 20 -регистр (РГ1, РГ2 соответственно),

18 - генератор (Г),

Предлагаемое устройство работает следующим образом.

При подаче напряжения питания на устройство по переднему его фронту формируется импульс, осуществляющий сброс триггера 12 и первого 3 и второго 19 пересчетного блоков, тем самым подготавливая селектор к приему входного сигнала - последовательности импульсов с заранее заданным периодом повторения. Заданный период повторения определяется кодом литерной частоты, поступающим на вход первого счетчика 8 через первый коммутатор сигналов 9 с входа кода литерной частоты селектора импульсов. Генератор 18 формирует тактовые импульсы для первого 8, второго 14 и третьего 23 счетчиков.

Первый из входных импульсов, поступающих на вход блока выделения первого импульса 1, пропускается им на первый вход первой схемы ИЛИ 4 и через нее - на первый вход первого счетчика 8, выполняющего функцию элемента задержки, осуществляя его запуск. Выходной импульс первого счетчика 8 задержан относительно запускающего на время:

где Т - заданный период повторения входных импульсов;

tс - длительность стробирующего импульса;

N - код литерной частоты;

t0 - период повторения тактовых импульсов.

Этим импульсом осуществляется запуск первого блока формирования стробов 13, формирующего строб-импульс, поступающий через вторую схему ИЛИ 17 на вход первой схемы И 7 и разрешающий прохождение очередного импульса, следующего на заданной частоте, на выход селектора. Передним фронтом строб-импульса осуществляется также сброс триггера 12.

Длительность строб-импульса определяется кодом Nп, формируемым шифратором 6. В режиме поиска значение этого кода определяется из соотношения:

где Δ - наибольшее отклонение периода повторения входных импульсов от номинального,

Δг - наибольшее отклонение времени формирования фронта стробирующего импульса от номинального.

Входной импульс, пришедший в стробируемом интервале, пройдя через первую схему И 7, осуществляет установку первого триггера 12 в состояние «1», фиксирующее попадание очередного импульса в стробируемый интервал, инкрементирует состояние первого пересчетного блока 3, фиксирующего количество последовательных (без пропусков) попаданий входных импульсов в стробируемый интервал, перезапускает через второй вход первой схемы ИЛИ 4 первый счетчик 8 и второй счетчик 14, формирующий код текущего значения периода повторения входных импульсов. Первый триггер 12, в свою очередь, разрешает счет импульсов вторым пересчетным блоком 19. Задним фронтом импульса с выхода первого блока формирования стробов осуществляется инкрементирование состояния пересчетного блока 19. При попадании двух входных импульсов подряд в стробируемый интервал первый и второй выходы второго пересчетного блока задним фронтом импульса с выхода блока формирования стробов поочередно устанавливается в единичное состояние. При этом сигнал с второго выхода второго пересчетного блока разрешает запись содержимого второго счетчика 14 в первый регистр 15, а с первого - перезапись содержимого первого регистра 15 во второй регистр 20. Таким образом, начиная с третьего входного импульса, попавшего в стробируемый интервал в первом и втором регистрах, сохраняются коды длительности последнего и предпоследнего периодов повторения входных импульсов соответственно. Если в стробируемом интервале входной импульс отсутствует, триггер 12 остается в исходном состоянии и разрешает сброс второго пересчетного блока 19 через третью схему И 5, первого пересчетного блока 3 и блока выделения первого импульса 1 через вторую схему И 2 - селектор готов к приему первого импульса новой последовательности. При попадании в стробируемый интервал, а следовательно на вход пересчетного блока 3, требуемого количества входных импульсов m (от трех до пяти, в зависимости от требуемой вероятности ложной тревоги при обнаружении искомой последовательности импульсов и допустимого времени поиска), сигнал с выхода пересчетного блока 3 переводит селектор в режим слежения за входными импульсами. При этом выходным сигналом первого пересчетного блока 3 запрещается прохождение через вторую схему И 2 импульса перезапуска блока выделения первого импульса 1 и пересчетного блока 3, коммутатор 9 подключает второй (информационный) вход счетчика 8 через второй сумматор 10 к выходу первого регистра 15, т.е. прогнозируемое положение строба определяется по результату измерения предыдущего периода повторения, сохраняемого в первом регистре 15.

Сигнал с выхода первого пересчетного блока 3 поступает также на вход шифратора 6 для формирования кода длительности стробирующего импульса при слежении. Значение этого кода определяется соотношением:

где Δк, Δгк - кратковременная нестабильность периодов повторения входных импульсов и прогнозируемого времени задержки, формируемого счетчиком 8 соответственно.

Для совпадения середины строб-импульса с прогнозируемым положением следующего входного импульса в сумматоре 10 формируется разность значений кодов предыдущего периода входного импульса и значения кода длительности стробирующего интервала, поступающая через коммутатор 9 на второй вход первого счетчика импульсов 8. Аналогичному преобразованию подвергается код, поступающий с выхода второго регистра 20 через первый сумматор 24 на второй вход третьего счетчика 23.

При регулярном попадании входного импульса в прогнозируемый стробирующий интервал слежение за входной последовательностью импульсов осуществляется следующим образом. По приходу входного импульса содержимое первого регистра 15 переписывается во второй регистр 20, содержимое второго счетчика 14 переписывается в первый регистр 15, очищается второй счетчик 14 и в нем накапливается результат измерения текущего периода, запускается первый счетчик 8, задержка импульса с выхода которого определяется поступающим через второй сумматор 10 и коммутатор 9 обновленным содержимым первого регистра 15, запускается третий счетчик 23, задержка импульса с выхода которого определяется обновленным содержимым второго регистра 20. По окончания времен задержки формируются импульсы запуска первого и второго блоков формирования стробов соответственно. Так как прохождение строб-импульса с выхода второго формирователя стробирующего импульса 22 через четвертую схему И 16 на вход второй схемы ИЛИ 17 блокируется единичным состоянием триггера 12, влияния на работу селектора он не оказывает.

При отсутствии очередного импульса в стробирующем интервале триггер 12 остается в исходном состоянии и импульс с выхода второго блока формирования стробирующего импульса через схему И поступает на вход схемы ИЛИ 17. Тем самым формируется второй стробирующий интервал, формируемый в предположении, что последний принятый входной импульс являлся помехой. Одновременно изменяется состояние логического уровня на третьем входе шифратора и сдвигателя кодов 11. При этом изменяется код на выходе шифратора, а следовательно, и длительность формируемых стробирующих интервалов. При этом, если отсутствие импульса в стробируемом интервале обусловлено отсутствием входных импульсов, требуемая длительность стробирующего интервала определяется соотношением:

где n - допустимое количество пропущенных импульсов входного сигнала. Если потеря обусловлена помехой, то требуемая длительность стробируемого интервала:

В качестве длительности строб-импульсов выбирается большее из значений Δпс1 или Δпс2.

В отсутствие выходных импульсов селектора формирование строб-импульсов осуществляется следующим образом. По заднему фронту импульса с выхода первого блока формирования строба запускается первый счетчик. При этом сдвигатель кодов 11 за счет действия на входе уровня логического нуля с выхода триггера 12 формирует код, сдвинутый на один разряд влево (код с удвоенным значением), вычитаемый далее из значения кода, хранящегося в первом регистре. Тем самым период повторения строб-импульсов на выходе первого формирователя стробов сохраняется равным последнему измеренному значению периода повторения входных импульсов. Аналогично формируются строб-импульсы на выходе второго блока формирователя стробов 22. При последующем попадании входного импульса в один из стробируемых интервалов перезапускаются первый, второй и третий счетчики - осуществляется синхронизация селектора по входному импульсу. При появлении уровня логической единицы на выходе триггера код на выходе шифратора 6, а следовательно, длительность строб-импульсов уменьшается до значения, определяемого по соотношению (3).

Блок выделения первого импульса может быть выполнен в соответствии с используемым в аналоге и прототипе.

Блоки формирования стробов представляют собой последовательно соединенные элементы задержки 1 и триггер 2, выход которого соединен с входом линии задержки и является выходом формирователя стробов, а установочный вход триггера - его входом. Запуск формирователя стробов осуществляется установкой триггера в состояние логической единицы, окончание стробирующего импульса происходит в момент сброса триггера импульсом с элемента задержки. Элемент задержки, в свою очередь, может быть реализован на счетчике с предустановкой, осуществляемой при запуске формирователя стробов, при этом длительность импульса определяется параллельным кодом, поступающим на вход счетчика.

Пересчетные блоки могут быть выполнены, например, на сдвиговом регистре с последовательным входом, подключенным к уровню логической единицы, и параллельными выходами. Вход 1 для первого пересчетного блока и третий для второго являются тактирующими, вход 2 для первого пересчетного блока и второй для второго являются входами сброса, а первый вход второго пересчетного блока - вход разрешения сдвига. Регистр второго пересчетного блока двухразрядный, количество триггеров в регистре первого пересчетного блока равно m - количеству импульсов, достаточных для надежного обнаружения искомой последовательности импульсов.

Прочие компоненты предлагаемого селектора может быть реализован на микросхемах серии 533, либо с использованием программируемых логических интегральных схем (ПЛИС), совместимость по логическим уровням (например, вход 1 второй схемы И и второй вход четвертой схемы И инверсные) обеспечивается включением дополнительных инверторов. В качестве триггера могут быть использована микросхема 564ТМ2.

Селектор импульсов, содержащий последовательно соединенные блок выделения первого импульса, первую схему ИЛИ, первый счетчик и первый блок формирования стробов, последовательно соединенные первую схему И и первый пересчетный блок, последовательно соединенные генератор и второй счетчик, а также триггер, вторую, третью схемы И, вторую схему ИЛИ, причем выход первой схемы И, являющийся выходом селектора импульсов, соединен с вторым входом первой схемы ИЛИ, вход селектора импульсов соединен с первыми входами блока выделения первого импульса и первой схемы И, отличающийся тем, что в него введены последовательно соединенные шифратор, сдвигатель кодов, первый сумматор, третий счетчик, второй блок формирования стробов, четвертая схема И и третья схема ИЛИ, последовательно соединенные первый регистр, второй сумматор и коммутатор, последовательно соединенные второй пересчетный блок и второй регистр, причем выход первого пересчетного блока соединен с первыми входами второй схемы И и шифратора, а также с вторыми входами коммутатора и второго счетчика, выход триггера соединен с первыми входами третьей схемы И и второго пересчетного блока и вторыми входами шифратора, сдвигателя кодов и четвертой схемы И, выход первой схемы И соединен с первым входом триггера и вторыми входами третьей схемы ИЛИ, первого и второго регистров и второго счетчика, выход первого блока формирователя стробов соединен с вторыми входами второй и третьей схем И, второго пересчетного блока и триггера и первым входом второй схемы ИЛИ, выход второй схемы И соединен с вторыми входами блока выделения первого импульса и первого пересчетного блока, выход третьей схемы И соединен с третьими входами первой схемы ИЛИ и второго пересчетного блока, выход шифратора соединен с вторыми входами первого и второго блоков формирования стробов, выход генератора соединен с третьим входом третьего счетчика и вторым входом первого счетчика, выход коммутатора соединен с третьим входом первого счетчика, а четвертый вход коммутатора является входом кода литерной частоты, выход первого регистра соединен с третьим входом второго регистра, выход которого соединен с вторым входом первого сумматора, второй выход второго пересчетного блока соединен с вторым входом первого регистра, выход третьей схемы ИЛИ соединен с четвертым входом третьего счетчика, выход четвертой схемы И соединен с вторым входом второй схемы ИЛИ, выход второго счетчика соединен с третьим входом первого регистра, выход сдвигателя кодов соединен с вторым входом второго сумматора, а выход второй схемы ИЛИ соединен с вторым входом первой схемы И.