Операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиотехники и связи. Техническим результатом является уменьшение входного статического тока ОУ, а также повышение быстродействия ОУ при импульсных входных сигналах. Операционный усилитель содержит первый (1) и второй (2) входные транзисторы, неинвертирующий вход (3) устройства, первый (4) и второй (5) прямосмещенные p-n переходы, инвертирующий (6) вход устройства, первый (7) токостабилизирующий двухполюсник, первую (8) шину источника питания, второй (9) токостабилизирующий двухполюсник, вторую (10) шину источника питания, первый (11) выходной транзистор, первый (12) вспомогательный источник напряжения питания, третий (13) токостабилизирующий двухполюсник, второй (14) выходной транзистор, второй (15) вспомогательный источник напряжения питания, четвертый (16) токостабилизирующий двухполюсник, третий (17) и четвертый (18) входные транзисторы. 1 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в решающих и инструментальных усилителях, аналогово-цифровых интерфейсах и т.п.).

Известны схемы операционных усилителей (ОУ) на основе входных каскадов на n-р-n и р-n-р транзисторах, связанных с промежуточным каскадом, обеспечивающим широкий диапазон изменения выходного напряжения ОУ (так называемую опцию Rail-to-rail). При этом промежуточные каскады реализуются, как правило, на основе двух токовых зеркал, инвертирующих входной сигнал [1-9]. Более высокочастотными являются ОУ, в которых промежуточный каскад выполнен по каскодной схеме [10].

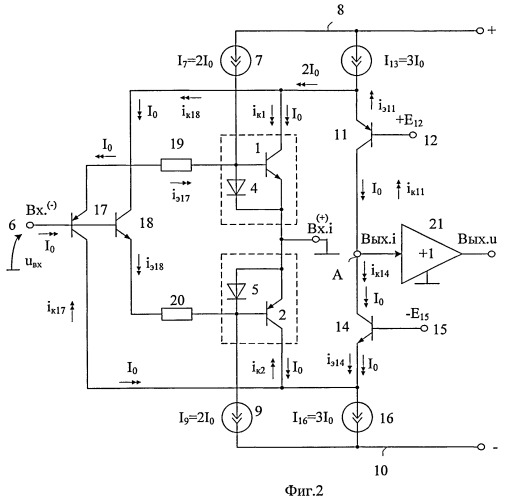

Ближайшим прототипом (фиг.1) заявляемого устройства является операционный усилитель, описанный в патенте фирмы National Semiconductor Corp.US №7479831, fig.7, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с неинвертирующим входом 3 устройства, первый 4 и второй 5 последовательно соединенные прямосмещенные р-n переходы, включенные между базами первого 1 и второго 2 входных транзисторов, инвертирующий 6 вход устройства, первый 7 токостабилизирующий двухполюсник, включенный между базой первого 1 входного транзистора и первой 8 шиной источника питания, второй 9 токостабилизирующий двухполюсник, включенный между базой второго 2 входного транзистора и второй 10 шиной источника питания, первый 11 выходной транзистор, база которого соединена с первым 12 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого 1 входного транзистора и через третий 13 токостабилизирующий двухполюсник связан с первой 8 шиной источника питания, второй 14 выходной транзистор, база которого соединена со вторым 15 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго 2 входного транзистора и через четвертый 16 токостабилизирующий двухполюсник связан со второй 10 шиной источника питания, причем коллекторы первого 11 и второго 14 выходных транзисторов связаны с токовым выходом устройства.

Существенный недостаток известного ОУ состоит в том, что он имеет недостаточно высокий коэффициент усиления по напряжению, обусловленный невысокими значениями крутизны преобразования входного напряжения (напряжения на инвертирующем входе входного каскада) в выходной ток, поступающий в промежуточный каскад.

Второй серьезный недостаток ОУ-прототипа - повышенный уровень входного статического тока, который определяется неидентичностью токов первого 7 и второго 9 токостабилизирующих двухполюсников.

Кроме этого, ОУ-прототип характеризуется невысоким быстродействием при импульсных входных сигналах (Uвх), что связано с отсутствием в нем пропорциональности между амплитудой импульсного входного напряжения (Uвх>0,7В) и приращением выходного тока входного каскада. Как следствие, из-за запирания р-n переходов 4 (5) под влиянием и наличия паразитной емкости Сп в цепи базы входных транзисторов 1 и 2, коллекторные токи транзисторов 1 (2) изменяются по линейному закону, что сдерживает реакцию ОУ на входные импульсные сигналы [11, 12].

Основная задача предлагаемого изобретения состоит в повышении коэффициента усиления по напряжению (K0), что обеспечивается созданием дополнительных каналов преобразования входного напряжения в выходной ток ОУ, повышающих при прочих равных условиях крутизну усиления входного каскада.

Дополнительные задачи - уменьшение входного статического тока ОУ, а также повышение быстродействия ОУ при импульсных входных сигналах.

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с неинвертирующим входом 3 устройства, первый 4 и второй 5 последовательно соединенные прямосмещенные р-n переходы, включенные между базами первого 1 и второго 2 входных транзисторов, инвертирующий 6 вход устройства, первый 7 токостабилизирующий двухполюсник, включенный между базой первого 1 входного транзистора и первой 8 шиной источника питания, второй 9 токостабилизирующий двухполюсник, включенный между базой второго 2 входного транзистора и второй 10 шиной источника питания, первый 11 выходной транзистор, база которого соединена с первым 12 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого 1 входного транзистора и через третий 13 токостабилизирующий двухполюсник связан с первой 8 шиной источника питания, второй 14 выходной транзистор, база которого соединена со вторым 15 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго 2 входного транзистора и через четвертый 16 токостабилизирующий двухполюсник связан со второй 10 шиной источника питания, причем коллекторы первого 11 и второго 14 выходных транзисторов связаны с токовым выходом устройства, предусмотрены новые элементы и связи - общий узел первого 4 и второго 5 прямосмещенных р-n переходов соединен с эмиттерами первого 1 и второго 2 входных транзисторов, инвертирующий 6 вход устройства подключен к базам третьего 17 и четвертого 18 входных транзисторов, эмиттер третьего 17 входного транзистора соединен с базой первого 1 входного транзистора через первый 19 вспомогательный резистор, эмиттер четвертого 18 входного транзистора соединен с базой второго 2 входного транзистора через второй 20 вспомогательный резистор, причем коллектор третьего 17 входного транзистора соединен с коллектором второго 2 входного транзистора, а коллектор четвертого 18 входного транзистора соединен с коллектором первого 1 входного транзистора.

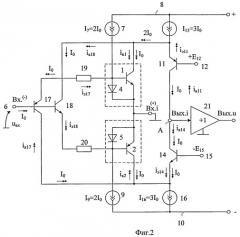

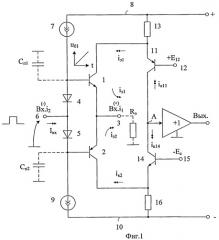

Схема заявляемого устройства, соответствующая п.1 и п.2 формулы изобретения, приведена на фиг.2. На фиг.3 показана схема ОУ в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

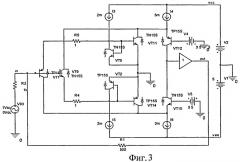

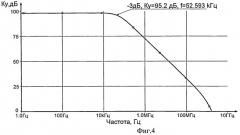

На фиг.4 приведена частотная зависимость коэффициента усиления по напряжению разомкнутого ОУ фиг.3.

Операционный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с неинвертирующим входом 3 устройства, первый 4 и второй 5 последовательно соединенные прямосмещенные р-n переходы, включенные между базами первого 1 и второго 2 входных транзисторов, инвертирующий 6 вход устройства, первый 7 токостабилизирующий двухполюсник, включенный между базой первого 1 входного транзистора и первой 8 шиной источника питания, второй 9 токостабилизирующий двухполюсник, включенный между базой второго 2 входного транзистора и второй 10 шиной источника питания, первый 11 выходной транзистор, база которого соединена с первым 12 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого 1 входного транзистора и через третий 13 токостабилизирующий двухполюсник связан с первой 8 шиной источника питания, второй 14 выходной транзистор, база которого соединена со вторым 15 вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго 2 входного транзистора и через четвертый 16 токостабилизирующий двухполюсник связан со второй 10 шиной источника питания, причем коллекторы первого 11 и второго 14 выходных транзисторов связаны с токовым выходом устройства. Общий узел первого 4 и второго 5 прямосмещенных р-n переходов соединен с эмиттерами первого 1 и второго 2 входных транзисторов, инвертирующий 6 вход устройства подключен к базам третьего 17 и четвертого 18 входных транзисторов, эмиттер третьего 17 входного транзистора соединен с базой первого 1 входного транзистора через первый 19 вспомогательный резистор, эмиттер четвертого 18 входного транзистора соединен с базой второго 2 входного транзистора через второй 20 вспомогательный резистор, причем коллектор третьего 17 входного транзистора соединен с коллектором второго 2 входного транзистора, а коллектор четвертого 18 входного транзистора соединен с коллектором первого 1 входного транзистора.

На фиг.2, в соответствии с п.2 формулы изобретения, токовый выход устройства (Вых.i) соединен со входом дополнительного буферного каскада 21, выход которого является потенциальным выходом устройства.

Рассмотрим работу известного фиг.1 и заявляемого фиг.2 ОУ.

В ОУ-прототипе фиг.1 входной статический ток зависит от разности токов двухполюсников 7 и 9:

Поэтому разброс численных значений 19 и 17 непосредственно влияет на входной ток ОУ Iвх (1).

В заявляемом ОУ фиг.2 входной статический ток Iвх в β-раз меньше I9=I7=I0 и определяется по формуле:

где β18≈β17 - коэффициенты усиления по току базы транзисторов 18 и 17.

Далее, за счет новых связей в заявляемой схеме ОУ создаются дополнительные каналы передачи входного сигнала к токовому выходу устройства (Вых.i). Действительно, uвx передается к узлу «А» (Вых.i) по 4 каналам:

- со входа 6 в коллектор транзистора 17, эмиттер транзистора 14 и далее к выходу Вых.i;

- со входа 6 в коллектор транзистора 18, эмиттер транзистора 11 и далее к выходу Вых.i;

- со входа 6 в эмиттер транзистора 18, в р-n переход 5, коллектор транзистора 2, эмиттер транзистора 14 и далее к выходу «Вых.i»;

- со входа 6 в эмиттер транзистора 17 в р-n переход 4, коллектор транзистора 1, эмиттер транзистора 11, и далее к выходу «Вых.i».

Таким образом, в схеме фиг.2 все изменения коллекторных токов транзисторов входного каскада «не теряются» и передаются к узлу «А» (Вых.i), что повышает K0.

Следует также заметить, что импульсное изменение входного напряжения (6) в ОУ фиг.2 не вызывает полную «парализацию» одного из 4 каналов передачи uвх, что в конечном итоге повышает быстродействие ОУ [11, 12].

Полученные выше выводы подтверждаются результатами моделирования предлагаемой схемы ОУ в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва) (фиг.4).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US 2009/0033423, fig.18.

2. Патент WO 2002/037672.

3. Патент US 6249153, fig.9.

4. Патент US 5399991 fig.3B.

5. Патент US 5512859.

6. Патент US 6724260.

7. Патент US 4502020.

8. Патент US 4833423 fig.2.

9. Патент ЕР 1418668 fig.3B.

10. Патент US №7479831, fig.7.

11. Прокопенко Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н.Прокопенко, А.С.Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

12. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л., 1979. - 148 с.

1. Операционный усилитель, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых соединены с неинвертирующим входом (3) устройства, первый (4) и второй (5) последовательно соединенные прямосмещенные р-n переходы, включенные между базами первого (1) и второго (2) входных транзисторов, инвертирующий (6) вход устройства, первый (7) токостабилизирующий двухполюсник, включенный между базой первого (1) входного транзистора и первой (8) шиной источника питания, второй (9) токостабилизирующий двухполюсник, включенный между базой второго (2) входного транзистора и второй (10) шиной источника питания, первый (11) выходной транзистор, база которого соединена с первым (12) вспомогательным источником напряжения питания, а эмиттер соединен с коллектором первого (1) входного транзистора и через третий (13) токостабилизирующий двухполюсник связан с первой (8) шиной источника питания, второй (14) выходной транзистор, база которого соединена со вторым (15) вспомогательным источником напряжения питания, а эмиттер соединен с коллектором второго (2) входного транзистора и через четвертый (16) токостабилизирующий двухполюсник связан со второй (10) шиной источника питания, причем коллекторы первого (11) и второго (14) выходных транзисторов связаны с токовым выходом устройства, отличающийся тем, что общий узел первого (4) и второго (5) прямосмещенных р-n переходов соединен с эмиттерами первого (1) и второго (2) входных транзисторов, инвертирующий (6) вход устройства подключен к базам третьего (17) и четвертого (18) входных транзисторов, эмиттер третьего (17) входного транзистора соединен с базой первого (1) входного транзистора через первый (19) вспомогательный резистор, эмиттер четвертого (18) входного транзистора соединен с базой второго (2) входного транзистора через второй (20) вспомогательный резистор, причем коллектор третьего (17) входного транзистора соединен с коллектором второго (2) входного транзистора, а коллектор четвертого (18) входного транзистора соединен с коллектором первого (1) входного транзистора.

2. Операционный усилитель по п.1, отличающийся тем, что токовый выход устройства соединен со входом дополнительного буферного каскада (21), выход которого является потенциальным выходом устройства.