Четырехтактный реверсивный распределитель импульсов для управления шаговым двигателем с автоматической коррекцией одиночных ошибок

Иллюстрации

Показать всеИзобретение относится к области автоматики и может быть использовано в коммутаторах шаговых электроприводов систем числового программного управления на базе четырехфазных шаговых двигателей. Технический результат заключается в повышении надежности. Для этого в заявленном устройстве аппаратно реализован алгоритм помехозащищенного кодирования Хэмминга, для чего к известному базовому устройству, содержащему двухразрядный реверсивный двоичный счетчик, шины управления, реверса, тактовых импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два инвертора, дополнительно введены три схемы свертки по модулю два, дешифратор, четыре управляемых инвертора. Новое устройство аппаратно реализует соотношения, связывающие коды счетчика с кодами информационных и контрольных разрядов, а также с кодами синдрома. При отсутствии ошибок код синдрома равен нулю, а при наличии ошибки соответствует ее адресу, по которому дешифратор и управляемые инверторы корректируют ошибочный разряд, что обеспечивает штатную работу распределителя как при отсутствии, так и при одиночных отказах. 3 табл., 2 ил.

Реферат

Изобретение относится к области автоматики и может быть использовано в коммутаторах шаговых электроприводов систем числового программного управления на базе четырехфазных шаговых электродвигателей.

Известно устройство для обнаружения отказов в шаговом электроприводе [1], содержащее блок синхронизации, логическое устройство, включающее реверсивный кольцевой сдвиговый регистр и элемент сравнения кодов, а также пороговые датчики тока, напряжения, логические схемы И.

Данное устройство обнаруживает отличающиеся от разрешенных комбинаций сигналов, поданных на соответствующие фазные обмотки шагового двигателя, однако, оно не корректирует эти ошибки.

Наиболее близким по техническому решению к заявляемому устройству является четырехтактный реверсивный распределитель импульсов для управления шаговым двигателем [2], содержащий шины управления, реверса, тактовых импульсов, реверсивный двухразрядный двоичный счетчик, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй инверторы. Это устройство формирует логические переменные a, b, c, d, которые через усилители мощности в разрешенных комбинациях запитывают фазные обмотки шагового двигателя.

К недостаткам этого распределителя следует отнести отсутствие автоматической коррекции отказов.

Заявляемое изобретение направлено на повышение надежности распределителя введением автоматической коррекции одиночных отказов.

Это достигается тем, что в четырехтактный реверсивный распределитель импульсов для управления шаговым двигателем, содержащий шины реверса, управления, тактовых импульсов, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй инверторы, реверсивный двухразрядный двоичный счетчик, соединенный тактовым входом с шиной тактовых импульсов, входом разрешения счета - с шиной управления, а входом для задания направления счета - с шиной реверса, выходами счетчик соединен с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входу первого инвертора, а вход второго инвертора соединен с выходом старшего разряда счетчика, дополнительно введены первая-третья схемы свертки по модулю два, дешифратор, первый-четвертый управляемые инверторы, при этом первый вход первой свертки объединен с третьими входами второй и третьей схемы свертки, а также со вторым входом третьего управляемого инвертора и подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы первой и второй схем свертки объединены с первым входом третьей схемы свертки, а также со вторым входом первого управляемого инвертора и подключены к выходу первого инвертора, третий вход первой схемы свертки объединен с первым входом второй схемы свертки, а также со вторым входом третьей схемы свертки и вторым входом второго управляемого инвертора и подключен к выходу второго инвертора, а объединенные четвертые входы первой-третьей схем свертки и второй вход четвертого управляемого инвертора подключены к выходу старшего разряда счетчика, а первые входы первого-четвертого управляемых инверторов соединены соответственно с третьим, пятым, шестым, седьмым выходами дешифратора, адресные входы которого первый, второй, четвертый соединены соответственно с выходами первой-третьей схем свертки, а выходы первого-четвертого управляемых инверторов являются первым-четвертым выходами распределителя.

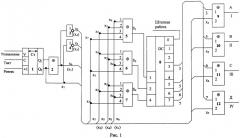

На рисунке 1 представлена функциональная схема заявляемого распределителя.

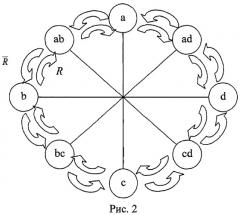

На рисунке 2 приведена векторная диаграмма поля статора шагового двигателя при коммутации фаз.

В таблице 1 представлена зависимость a, b, c, d переменных от кодов счетчика Q2Q1.

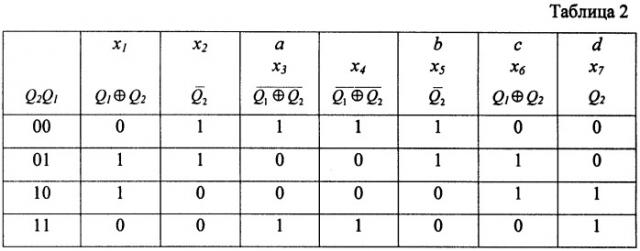

Таблица 2 описывает зависимость контрольных и информационных разрядов от кодов счетчика Q2Q1.

В таблице 3 показаны значения синдрома при ошибках x5≡0, x7≡1 для всех наборов Q2Q1.

Четырехтактный реверсивный распределитель содержит реверсивный двоичный двухразрядный счетчик 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, первый 3 и второй 4 инверторы, первую-третью схемы свертки 5-7, дешифратор 8, первый-четвертый управляемые инверторы 9-12.

Распределитель работает следующим образом: тактовые импульсы поступают на тактовый вход «С» реверсивного двоичного счетчика 1 и, если на шину управления подан сигнал разрешения счета, то счетчик 1 увеличивает или уменьшает содержимое в зависимости от уровня сигнала (1 или 0) на шине реверса.

Логические переменные a, b, c, d, управляющие включением фазных напряжений шагового двигателя при цикле парной четырехтактной коммутации [3], образуют наборы , , , при прямом вращении и , , , - при реверсе.

В таблице 1 приведена зависимость переменных a, b, c, d от кодов состояния счетчика Q2Q1. Алгебраическое выражение этой зависимости приведено соотношениях (1).

| Таблица 1 | |||||

| Q2 | Q1 | а | b | с | d |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 1 |

Эти соотношения аппаратно реализуются счетчиком 1, двумя инверторами 3, 4 и схемой ИСКЛЮЧАЮЩЕЕ ИЛИ 2.

Для обнаружения и коррекции одиночных ошибок введена аппаратная реализация кодирования Хэмминга [4], контрольные разряды которого x1, x2, x4 представлены соотношениями (2).

где a=x3, b=x5, c=x6, d=x7.

В таблице 2 приведена зависимость контрольных и информационных разрядов от кодовых комбинаций Q2Q1 счетчика 1.

Из таблицы 2 следует, что x1=x6; x2=x5; x3=x4. Указатель адреса ошибки - синдром S(S4, S2, S1) определяется соотношением (3).

Откуда следует, что при отсутствии ошибок код синдрома равен нулю, а на нулевом выходе дешифратора 8 устанавливается логическая единица, указывающая на правомерность использования информационных разрядов x3, x5, x6, x7, коды которых проходят через управляемые инверторы без изменений.

При наличии ошибки двоичный код синдрома указывает ее адрес. На соответствующем этому коду выходе дешифратора появляется логическая единица, которая с помощью управляемого инвертора восстанавливает ошибочный разряд.

Пусть в информационном разряде x5 возникла ошибка x5≡0, что нарушает нормальную работу распределителя на наборах Q2Q1=00, Q2Q1=01 и вызывает формирование синдрома S (101), а так же логической единицы на пятом выходе дешифратора, корректирующей ошибки в пятом разряде. На наборах Q2Q1=10, Q2Q1=11 неискаженное значение x5 равно нулю, что формирует синдром S (000), указывающий на возможное корректное использование информационных разрядов x3, x5, x6, x7 (0011, 1001). Формирование синдрома для различных наборов Q2Q1 при наличии ошибок x5≡0, x7≡1 приведено в таблице 3.

Источники информации

1. Авторское свидетельство №1415401. Кл Н02Р 8/00, Бюл. №29, 07.08.88.

2. Авторское свидетельство №1432719. Кл Н02Р 8/00, Бюл. №39, 23.10.88.

3. Чиликин М.Г. Дискретный электропривод с шаговыми двигателями. Под ред. М.Г.Чиликина - М.: Энергия. 1971.

4. Угрюмов Е.П. Цифровая схемотехника. Учеб. пособие для вузов. - 2-е. издание, перераб. и доп.- СПб: БХВ - Петербург. 2007.

Четырехтактный реверсивный распределитель импульсов для управления шаговым двигателем с автоматической коррекцией одиночных ошибок, содержащий шины управления, реверса, тактовых импульсов, двухразрядный реверсивный двоичный счетчик, два инвертора и элемент Исключающее ИЛИ, входы которого соединены с выходами реверсивного счетчика, причем тактовый вход счетчика подключен к шине тактовых импульсов, его входы разрешения и направления счета соединены соответственно с шинами управления и реверса, выход элемента Исключающее ИЛИ соединен с входом первого инвертора, а вход второго инвертора подключен к выходу старшего разряда счетчика, отличающийся тем, что в него дополнительно введены первая-третья схемы свертки, дешифратор и первый-четвертый управляемые инверторы, при этом первый вход первой схемы свертки объединен с третьими входами второй и третьей схем свертки, а также со вторым входом третьего управляемого инвертора и подключен к выходу элемента Исключающее ИЛИ, вторые входы первой и второй схем свертки объединены с первым входом третьей схемы свертки, а также и со вторым входом первого управляемого инвертора и подключены к выходу первого инвертора, третий вход первой схемы свертки объединен с первым входом второй схемы свертки, а также со вторым входом третьей схемы свертки и вторым входом второго управляемого инвертора и подключен к выходу второго инвертора, а объединенные четвертые входы первой-третьей схемы свертки и второй вход четвертого управляемого инвертора подключены к выходу старшего разряда счетчика, а первые входы первого-четвертого управляемых инверторов соединены соответственно с третьим, пятым, шестым, седьмым выходами дешифратора, адресные входы которого первый, второй, четвертый соединены соответственно с выходами первой-третьей схемы свертки, а выходы первого-четвертого управляемых инверторов являются первым-четвертым выходами распределителя.