Устройство и способ для передачи и приема преамбул в системе цифровой широковещательной передачи видео

Иллюстрации

Показать всеИзобретение относится к системе цифровой широковещательной передачи видео (DVB) и, в частности, к устройству и способу для передачи и приема преамбул для компонентов кадра в DVB-системе. Техническим результатом является уменьшение отношения пиковой мощности к средней мощности (PAPR) преамбулы посредством скремблирования. Указанный технический результат достигается тем, что предложено устройство и способ для передачи преамбулы в системе DVB, при этом устройство содержит: первый процессор для формирования последовательности сигнализации модуляции (MSS) с использованием множества принимаемых последовательностей и для вывода модулированной последовательности посредством дифференциальной модуляции MSS; модуль скремблирования для скремблирования модулированной последовательности посредством умножения модулированной последовательности на последовательность скремблирования и второй процессор принимает скремблированную последовательность через каждую выделенную поднесущую, преобразует принимаемую последовательность в сигнал временной области и формирует и передает преамбулу. 4 н. и 23 з.п. ф-лы, 10 ил., 5 табл.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение, в общем, относится к системе цифровой широковещательной передачи видео (DVB). Более конкретно, настоящее изобретение относится к устройству и способу для передачи и приема преамбул для компонентов кадра в DVB-системе.

Описание предшествующего уровня техники

В общем, термин "система цифровой широковещательной передачи" обозначает систему широковещательной передачи с применением технологии цифровой передачи, такой как цифровая широковещательная передача аудио (DAB), цифровая широковещательная передача видео (DVB) и цифровая широковещательная передача мультимедиа (DMB).

В числе других DVB-система, европейская технология цифровой широковещательной передачи, является стандартом передачи для поддержки не только существующей цифровой широковещательной передачи, но также и цифровых мультимедийных услуг для мобильных/портативных устройств.

DVB-система может мультиплексировать широковещательные данные на основе транспортного потока по стандарту экспертной группы по киноизображению 2 (MPEG 2 TS) и передавать потоки данных на основе IP одновременно. В DVB-системе различные услуги могут быть переданы после мультиплексирования в один IP-поток. А также после приема данных передаваемого IP-потока, терминал может демультиплексировать их обратно в отдельные услуги, демодулировать услуги и выводить их через экран пользовательского терминала. Здесь пользовательскому терминалу требуется информация, указывающая типы различных услуг, предоставляемых посредством DVB-системы, и сведения, которые содержит каждая из услуг.

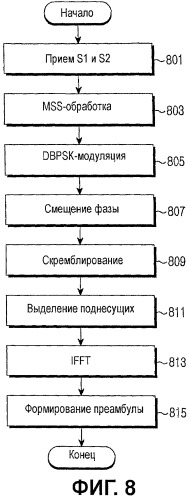

Фиг.1 является схемой, иллюстрирующей структуру кадра физического канала в традиционной DVB-системе.

Согласно фиг.1 структура кадра может примерно разделяться на части P1 и P2 преамбулы и части BODY тела. Части P1 и P2 преамбулы используются для передачи служебной информации кадра, тогда как части тела состоят из частей, используемых для передачи данных или полезной нагрузки.

Цели преамбулы P1 на фиг.1 следующие. Во-первых, преамбула P1 используется для сканирования начального сигнала кадра в приемном устройстве. Во-вторых, преамбула P1 используется для обнаружения сдвига частоты и настройки средней частоты в приемном устройстве. В-третьих, преамбула P1 используется для передачи идентификационной информации кадра, а также передачи размера быстрого преобразования Фурье (FFT) и другой информации передачи. Наконец, преамбула P1 используется для обнаружения и коррекции частотной и временной синхронизации в приемном устройстве.

Касательно структуры преамбулы P1 на фиг.1 часть A, в которой передается информация, устанавливается равной 1K символов мультиплексирования с ортогональным частотным разделением (OFDM) независимо от FFT-размера полезной нагрузки, где передаются данные, и имеет длину 112 мкс. Когда другие части B и C состоят из 1/2 защитного интервала, они добавляются к обеим сторонам 1K символов, с длиной 56 мкс. Как показано на фиг.1, общая длина преамбулы P1 составляет 224 мкс.

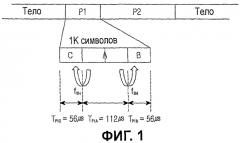

Фиг.2 является схемой, иллюстрирующей местоположения несущих, на которых последовательность преамбул передается согласно уровню техники.

Фиг.2 приведена для описания внутренней структуры 1K OFDM-символов, показанных на фиг.1. Как проиллюстрировано на фиг.2, 1K OFDM-символов включают в себя 853 несущие. Из этих 853 несущих, составляющих 1K OFDM-символов, только 384 несущие используются для передачи последовательности преамбул.

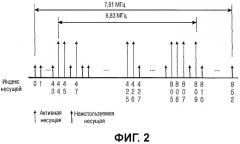

Фиг.3 является блок-схемой, иллюстрирующей передающее устройство для передачи преамбулы в традиционной DVB-системе.

Местоположения несущих, используемых для передачи последовательности преамбул из этих 853 несущих, могут быть заранее определенными. На фиг.3 местоположения несущих заранее определены и сохранены в таблице последовательности распределения несущих (CDS) 300.

Работа процессора 310 последовательностей сигнализации модуляции (MSS) осуществляется следующим образом. MSS-процессор 310 принимает первую последовательность (в дальнейшем 'S1') и вторую последовательность (в дальнейшем 'S2') и формирует комплементарные наборы последовательностей (CSS). S1 и S2 включают в себя 3-битовую информацию и 4-битовую информацию, соответственно. CSS, сформированные посредством S1 и S2, имеют 8 и 16 комбинаций, соответственно, и CSSS1 и CSSS2, сформированные посредством S1 и S2, имеют длину в 64 и 256, соответственно. Такие CSS отличаются тем, что имеют низкое отношение пиковой мощности к средней мощности (PAPR) и являются ортогональными друг с другом.

Сигналы S1 и S2 могут быть выражены так, как показано в таблице 1, в которой они выражаются в шестнадцатиричном формате.

| Таблица 1 | |

Последовательность процессов, в которых последовательности S1 и S2 выводятся как модулированная последовательность посредством MSS-процессора 310 через процессор 325 смещения фазы, является следующей.

Уравнение (1) представляет последовательность, сформированную посредством комбинации S1 и S2 в MSS-процессоре 310, и последовательность обозначается посредством MSS_SEQ:

| (1) |

MSS_SEQ в уравнении (1) модулируется посредством дифференциальной BPSK (DBPSK) в DBPSK-модуляторе (или модуле DBPSK-преобразования) 320, уравнение (2) представляет DBPSK-модулированную последовательность, которая обозначается посредством MSS_DIFF.

| (2) |

Процессор 325 смещения фазы выводит конечную модулированную последовательность посредством применения смещения фазы в 180° к 64 самым старшим (MSB) битам (или ячейкам) в модулированной последовательности. Процессор 325 смещения фазы не применяет смещение фазы к оставшимся битам, за исключением 64 битов MSB. Поскольку все 64 бита MSB имеют одинаковое значение смещения, значение смещения фазы не должно влиять на процесс демодуляции DBPSK-демодулятора в приемном устройстве. Следовательно, нет необходимости в процессе, обратном процессу смещения фазы в приемном устройстве. Окончательно вывод процессора 325 смещения фазы определяется уравнением (3):

| (3) |

Последовательность, выводимая через MSS-процессор 310, DBPSK-модулятор 320 и процессор 325 смещения фазы, т.е. модулированная последовательность, распределяется 384 активным несущим для P1 посредством модуля 330 распределения несущих.

В структуре добавляются 2 защитных интервала, чтобы повышать надежность символов для P1, и операции процессора обратного быстрого преобразования Фурье (IFFT) 340 и формирователя 350 преамбул являются практически идентичными операциям на фиг.1.

Фиг.4 является блок-схемой, иллюстрирующей приемное устройство для приема преамбулы в традиционной DVB-системе.

Согласно фиг.4 детектор 400 преамбулы в приемном устройстве обнаруживает преамбулу и вводит ее в FFT-процессор 410. FFT-процессор 410 выполняет FFT для обнаруженной преамбулы и выводит результаты в демультиплексор (DEMUX) 420. Затем демультиплексор 420 демультиплексирует данные по активным несущим, через которые преамбула передается, и выводит демультиплексированные данные в DBPSK-демодулятор 430. DBPSK-демодулятор 430 выполняет процесс, обратный процессу, выполняемому процессором 325 смещения фазы, т.е. выполняет DBPSK-демодуляцию, которая обратно сдвигает по фазе MSB-сигналы преамбулы длиной 64 в приемном устройстве и затем выводит результаты в детектор 440 сигнализации. Детектор 440 сигнализации выводит полезную информацию посредством обнаружения S1 и S2 из демодулированной последовательности.

Фиг.5 является блок-схемой последовательности операций способа, иллюстрирующей способ приема для приема преамбулы в традиционной DVB-системе.

Согласно фиг.5 приемное устройство выполняет инициализацию на этапе 500 и выполняет настройку для преамбулы на этапе 505. Приемное устройство выполняет корреляцию защитных интервалов (GIC) для принимаемого сигнала на этапе 510 и определяет на этапе 515, обнаружило ли оно преамбулу P1. Если приемное устройство не смогло обнаружить преамбулу P1 на этапе 515, приемное устройство возвращается к этапу 510. Иначе, когда приемное устройство обнаружило преамбулу P1 приемное устройство выполняет приблизительное временное регулирование и точное регулирование сдвига частоты на этапе 520. Затем на этапе 525 приемное устройство выполняет корреляцию мощности, чтобы оценивать мощность активных несущих, и определяет снова на этапе 530, обнаружило ли оно преамбулу P1. При невозможности обнаруживать преамбулу P1 приемное устройство возвращается к этапу 510, а когда приемное устройство успешно обнаруживает преамбулу P1, приемное устройство выполняет грубую настройку сдвига частоты на этапе 535. После этого приемное устройство выполняет DBPSK-демодуляцию, которая является процессом, обратным процессу, выполняемому схемой дифференциальной модуляции в передающем устройстве, на этапе 540, вычисляет значение корреляции между преамбулами на этапе 545 и обнаруживает сигналы S1 и S2 на этапе 550.

Поскольку вышеуказанная традиционная структура преамбулы использует дифференциальную модуляцию (т.е. DBPSK), некогерентный прием возможен. Тем не менее, характеристика комплементарных последовательностей изменяется вследствие выполнения дифференциальной модуляции, приводя к увеличению PAPR. Соответственно, имеется необходимость в усовершенствованном устройстве и способе для передачи и приема преамбул для компонентов кадра в DVB-системе.

Сущность изобретения

Аспект настоящего изобретения заключается в том, чтобы разрешать, по меньшей мере, вышеуказанные проблемы и/или недостатки и обеспечивать, по меньшей мере, преимущества, описанные ниже. Соответственно, аспект настоящего изобретения заключается в том, чтобы предоставлять устройство и способ, допускающие уменьшение PAPR преамбулы посредством скремблирования.

В соответствии с аспектом настоящего изобретения предоставляется устройство для передачи преамбулы в системе цифровой широковещательной передачи видео (DVB). Устройство передачи включает в себя первый процессор для формирования последовательности сигнализации модуляции (MSS) с использованием множества принимаемых последовательностей и для вывода модулированной последовательности посредством дифференциальной модуляции MSS, модуль скремблирования для скремблирования модулированной последовательности посредством умножения модулированной последовательности на последовательность скремблирования и второй процессор для приема скремблированной последовательности через каждую из множества выделенных поднесущих, для преобразования принимаемой последовательности в сигнал временной области и для формирования и передачи преамбулы.

В соответствии с другим аспектом настоящего изобретения предоставляется способ для передачи преамбулы в системе цифровой широковещательной передачи видео (DVB). Способ передачи включает в себя формирование последовательности сигнализации модуляции (MSS) с использованием множества принимаемых последовательностей, вывод модулированной последовательности посредством дифференциальной модуляции MSS, скремблирование модулированной последовательности посредством умножения модулированной последовательности на последовательность скремблирования, прием скремблированной последовательности через каждую из множества выделенных поднесущих, преобразование принимаемой последовательности в сигнал временной области и формирование и передачу преамбулы.

В соответствии с аспектом настоящего изобретения предоставляется устройство для передачи преамбулы в системе цифровой широковещательной передачи видео (DVB). Устройство приема включает в себя первый процессор для обнаружения преамбулы из принимаемого сигнала, для преобразования обнаруженной преамбулы в сигнал частотной области и для демультиплексирования сигнала частотной области, модуль дескремблирования для дескремблирования демультиплексированной последовательности посредством умножения демультиплексированной последовательности на последовательность дескремблирования и второй процессор для дифференциальной демодуляции дескремблированной последовательности и для обнаружения множества последовательностей из демодулированной последовательности.

В соответствии с еще одним аспектом настоящего изобретения предоставляется способ для приема преамбулы в системе цифровой широковещательной передачи видео (DVB). Способ приема включает в себя обнаружение преамбулы из принимаемого сигнала, преобразование обнаруженной преамбулы в сигнал частотной области, демультиплексирование сигнала частотной области, дескремблирование демультиплексированной последовательности посредством умножения демультиплексированной последовательности на последовательность дескремблирования, дифференциальную демодуляцию дескремблированной последовательности и обнаружение множества последовательностей из демодулированной последовательности.

Другие аспекты, преимущества и выраженные признаки изобретения должны стать очевидными специалистам в данной области техники из последующего подробного описания, которое, при рассмотрении вместе с прилагаемыми чертежами, раскрывает примерные варианты осуществления изобретения.

Краткое описание чертежей

Вышеуказанные и другие примерные аспекты, признаки и преимущества примерных вариантов осуществления настоящего изобретения должны стать более понятными из последующего подробного описания, рассматриваемого вместе с прилагаемыми чертежами, на которых

Фиг.1 является схемой, иллюстрирующей структуру кадра физического канала в традиционной DVB-системе;

Фиг.2 является схемой, иллюстрирующей местоположения несущих, на которых последовательность преамбул передается в традиционной области техники;

Фиг.3 является блок-схемой, иллюстрирующей передающее устройство для передачи преамбулы в традиционной DVB-системе;

Фиг.4 является блок-схемой, иллюстрирующей приемное устройство для приема преамбулы в традиционной DVB-системе;

Фиг.5 является блок-схемой последовательности операций способа, иллюстрирующей способ приема для приема преамбулы в традиционной DVB-системе;

Фиг.6 является блок-схемой, иллюстрирующей передающее устройство для передачи преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения;

Фиг.7 является схемой, иллюстрирующей пример PRBS-кодера для уравнения (5);

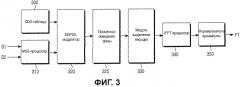

Фиг.8 является блок-схемой последовательности операций способа, иллюстрирующей способ передачи для передачи преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения;

Фиг.9 является блок-схемой, иллюстрирующей приемное устройство для приема преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения, и

Фиг.10 является блок-схемой последовательности операций способа, иллюстрирующей способ приема для приема преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения.

Следует отметить, что на всех чертежах аналогичные ссылочные позиции используются для обозначения идентичных или аналогичных элементов, признаков и структур.

Подробное описание примерных вариантов осуществления

Последующее описание со ссылкой на прилагаемые чертежи предоставлено для содействия полному пониманию примерных вариантов осуществления изобретения, как определено посредством формулы изобретения и ее эквивалентов. Оно включает в себя различные сведения, способствующие такому пониманию, которые, однако, должны рассматриваться просто как примерные. Соответственно, специалистам в данной области техники должно быть понятно, что различные изменения и модификации вариантов осуществления, описанных в данном документе, могут осуществляться без отступления от сущности и объема изобретения. Таким образом, описания хорошо известных функций и конструкций опущены для ясности и краткости.

Термины и слова, используемые в последующем описании и формуле изобретения, не ограничены библиографическими значениями, а используются изобретателем для обеспечения возможности ясного и согласованного понимания изобретения. Соответственно, специалистам в данной области техники должно быть очевидным, что последующее описание примерных вариантов осуществления настоящего изобретения предоставлено только для иллюстрации, а не для ограничения изобретения, как определено посредством прилагаемой формулы изобретения и ее эквивалентов.

Следует понимать, что формы единственного числа включают в себя ссылки на множество, если контекст явно не предписывает иное. Таким образом, например, ссылка на "поверхность компонента" включает в себя ссылку на одну или более из таких поверхностей.

Под термином "практически" подразумевается, что изложенная характеристика, параметр или значение не обязательно должны достигаться точно, но что отклонения или варьирования, включающие в себя, например, допуски, погрешность измерения, ограничения точности измерения и другие факторы, известные специалистам в данной области техники, могут возникать в величинах, которые не препятствуют достижению ожидаемого эффекта.

Настоящее изобретение относится к преамбуле, в которой передается служебная информация и, в частности, к преамбуле P1, через которую передается начальная информация. Примерные варианты осуществления настоящего изобретения предоставляют способ для разрешения вышеуказанной проблемы того, что отношение пиковой мощности к средней мощности (PAPR) комплементарных последовательностей для преамбулы увеличивается вследствие использования дифференциальной модуляции.

Описание примерных вариантов осуществления настоящего изобретения приводится ниже.

Таблица 2 показывает PAPR преамбул для случая, когда схема дифференциальной модуляции не применяется в преамбуле P1. Когда 128 сигналов преамбулы формируются посредством комбинаций S1 и S2, максимальное PAPR составляет 10,29 дБ, минимальное PAPR составляет 6,72 дБ, а среднее PAPR составляет 8,21 дБ.

| Таблица 2 | |

Однако таблица 3 показывает PAPR преамбул для случая, в котором применяется схема дифференциальной модуляции. В этом случае максимальное PAPR преамбул составляет 10,50 дБ, минимальное PAPR составляет 7,14 дБ, а среднее PAPR составляет 7,14 дБ. Как указано выше, можно видеть из сравнения между таблицей 2 и таблицей 3, что PAPR увеличивается по мере того, как характеристики комплементарных последовательностей расходятся друг от друга вследствие использования схемы дифференциальной модуляции. Из таблицы 2 и таблицы 3 можно видеть, что среднее PAPR увеличивается на 0,42 дБ вследствие влияния дифференциальной модуляции.

| Таблица 3 | |

В качестве способа для разрешения проблемы увеличения PAPR, вызываемого посредством дифференциальной модуляции, т.е. для уменьшения PAPR, DVB-система может применять скремблирование.

Фиг.6 является блок-схемой, иллюстрирующей передающее устройство для передачи преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения.

Согласно фиг.6 передающее устройство включает в себя CDS-таблицу 600, MSS-процессор 610, DBPSK-модулятор 620, процессор 630 смещения фаз, модуль 635 скремблирования, модуль 640 выделения несущих, IFFT-процессор 650 и формирователь 660 преамбул. Поскольку CDS-таблица 600, MSS-процессор 610, DBPSK-модулятор 620, процессор 630 смещения фаз, модуль 640 выделения несущих, IFFT-процессор 650 и формирователь 660 преамбул фактически идентичны по функциям CDS-таблице 300, MSS-процессору 310, DBPSK-модулятору 320, процессору 325 смещения фаз, модулю 330 выделения несущих, IFFT-процессору 340 и формирователю 350 преамбул в традиционном передающем устройстве по фиг.3, их подробное описание опускается.

Модуль 635 скремблирования, согласно примерному варианту осуществления настоящего изобретения, может предотвращать увеличение PAPR для комплементарного набора последовательностей (CSS), сформированного посредством MSS-процессора 610, посредством DBPSK-модулятора 620 и процессора 630 смещения фаз. Другими словами, в примерной реализации модуль 635 скремблирования формирует новую последовательность посредством умножения модулированной последовательности, выводимой из процессора 630 смещения фаз, на последовательность скремблирования. Модуль 635 скремблирования может работать с любой произвольной последовательностью, когда операция изменения сигнала из MSS-процессора 610 в произвольную форму выполняется.

Выходная MSS_SCR модуля 635 скремблирования выражается как уравнение (4).

| (4) |

В уравнении (4) термин "SCR" обозначает операцию скремблирования модуля 635 скремблирования. Новая последовательность формируется посредством умножения модулированной последовательности, вводимой в модуль 635 скремблирования, на последовательность скремблирования. Например, когда BSPK-последовательность длины K вводится как модулированная последовательность, т.е. когда {10, -11, -12, 13,..., 1K-1} вводится как модулированная последовательность, даже последовательность скремблирования может быть сформирована с помощью произвольной BPSK-последовательности длины K. Когда последовательность скремблирования {-10, -11, -12, -13,..., -1K-1}, модуль 635 скремблирования формирует {-10, -11, 12, -13,..., -1K-1} как новую BPSK-последовательность длины K посредством умножения модулированной последовательности {10, -11, -12, 13,..., 1K-1} на последовательность скремблирования {-10, 11, -12, -13,..., -1K-1}. Таким образом, модуль 635 скремблирования формирует новую последовательность MSS_SCR посредством умножения последовательности, модулированной с помощью уравнения (4), на последовательность скремблирования.

Модуль 635 скремблирования выполняет скремблирование посредством умножения последовательности, модулированной в DBPSK-модуляторе 620 и процессоре 630 смещения фаз, т.е. модулированной последовательности длины 384, выраженной в 1 или -1, на последовательность скремблирования длины 384, используемую в модуле 635 скремблирования. Последовательность скремблирования описывается подробнее в следующем примерном варианте осуществления.

Модуль 635 скремблирования формирует последовательность скремблирования для уменьшения PAPR преамбулы P1. В DVB-системе используется псевдослучайная двоичная последовательность (PRBS), заданная уравнением (5), и модуль 635 скремблирования может формировать последовательность скремблирования с использованием существующей PRBS.

| 1+X14+X15 | (5) |

Фиг.7 является схемой, иллюстрирующей пример PRBS-кодера для уравнения (5).

Согласно фиг.7 PRBS-регистр 710 принимает последовательность начальных значений (100010111100101) и формирует PRBS-последовательность (1110100011100100011100100...). Начальное значение и последовательность скремблирования PAPR длины 384 показываются в таблице 4.

| Таблица 4 | |||||||||||||||||||||||||||||||

| Последовательность начальных значений | |||||||||||||||||||||||||||||||

| 1 0 0 0 1 0 1 1 1 1 0 0 1 0 1 | |||||||||||||||||||||||||||||||

| PRBS (последовательность скремблирования) | |||||||||||||||||||||||||||||||

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

Последовательность скремблирования таблицы 4 используется как последовательность скремблирования для модуля скремблирования, используемого для уменьшения PAPR преамбулы P1. В PRBS-кодере по фиг.7 последовательность длины 384, сформированная с начальным значением таблицы 4, преобразуется из значения 0 или 1 к значению 1 или -1 и умножается на модулированную последовательность, выводимую из процессора смещения фаз в модуле 635 скремблирования, тем самым уменьшая PAPR.

Таблица 5 показывает PAPR 128 преамбул P1 в примерном варианте осуществления настоящего изобретения, который использует скремблирование для уменьшения PAPR. Можно отметить, что максимальное PAPR составляет 9,10 дБ, минимальное PAPR составляет 6,71 дБ, а среднее PAPR составляет 8,01 дБ. По сравнению с таблицей 3 усиление в 1,4 дБ может получаться при максимальном PAPR.

| Таблица 5 | |

В примерной реализации новая последовательность формируется посредством вышеуказанного модуля 635 скремблирования. Кроме того, каждая последовательность скремблирования может сохраняться в таблице поиска для будущего использования или может быть определена при необходимости. В качестве примера, вывод DBPSK-модулятора 620 на фиг.6 может сохраняться в таблице поиска, вывод модуля 635 скремблирования может сохраняться в таблице поиска или выводы всех этапов 600-635 могут сохраняться в таблице поиска для работы модуля 635 скремблирования.

Фиг.8 является блок-схемой последовательности операций способа, иллюстрирующей способ передачи для передачи преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения.

Согласно фиг.8 передающее устройство принимает S1 и S2 на этапе 801 и формирует MSS посредством выбора последовательности, соответствующей S1 и S2, на этапе 803. Передающее устройство дифференцированно модулирует MSS на этапе 805 и применяет смещение фазы в 180° к 64 битам MSB на этапе 807. На этапе 809 передающее устройство выполняет скремблирование посредством умножения последовательности скремблирования, сформированной посредством уравнения (5), на последовательность, модулированную на этапе 807. На этапе 811 передающее устройство принимает скремблированную последовательность через каждую выделенную поднесущую. Затем, на этапе 813, передающее устройство формирует сигнал временной области посредством выполнения IFFT для скремблированной последовательности, принимаемой через выделенную поднесущую. В завершение, на этапе 815, передающее устройство формирует преамбулу, имеющую структуру, проиллюстрированную на фиг.1.

Поскольку операция скремблирования, выполняемая посредством модуля 635 скремблирования, выполняется после DBPSK-модуляции, примерные варианты осуществления настоящего изобретения являются более стабильными по характеристикам обнаружения S1 и S2 по сравнению с тем, когда операция скремблирования выполняется перед DBPSK-модуляцией. Другими словами, примерные варианты осуществления настоящего изобретения являются надежными по характеристикам обнаружения S1 и S2.

Фиг.9 является блок-схемой, иллюстрирующей приемное устройство для приема преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения.

Согласно фиг.9, приемное устройство включает в себя детектор 900 преамбулы, FFT-процессор 910, демультиплексор 920, модуль 930 дескремблирования, DBPSK-демодулятор 940 и детектор 950 сигнализации. Поскольку детектор 900 преамбулы, FFT-процессор 910, демультиплексор 920, DBPSK-демодулятор 940 и детектор 950 сигнализации фактически идентичны по функциям детектору 400 преамбул, FFT-процессору 410, демультиплексору 420, DBPSK-демодулятору 430 и детектору 440 сигнализации, проиллюстрированным на фиг.4, их подробное описание опускается.

Модуль 930 дескремблирования, согласно примерному варианту осуществления настоящего изобретения, выполняет процесс, обратный процессу, выполняемому модулем 635 скремблирования для последовательности, полученной посредством демультиплексирования данных по активным несущим, через которые передается преамбула. Другими словами, модуль 930 дескремблирования выполняет дескремблирование посредством умножения демультиплексированной последовательности на последовательность дескремблирования. Последовательность дескремблирования имеет длину, идентичную длине демультиплексированной последовательности. Последовательность дескремблирования может быть заранее определена и сохранена в таблице поиска или может быть сформирована с использованием PRBS способом, практически идентичным способу относительно вышеуказанной последовательности скремблирования.

Фиг.10 является блок-схемой последовательности операций способа, иллюстрирующей способ приема для приема преамбулы в DVB-системе согласно примерному варианту осуществления настоящего изобретения.

Согласно фиг.10 приемное устройство выполняет инициализацию на этапе 1000 и выполняет настройку для преамбулы на этапе 1005. Приемное устройство выполняет корреляцию защитных интервалов (GIC) для принимаемого сигнала на этапе 1010 и определяет на этапе 1015, обнаружило ли оно преамбулу P1. Если приемное устройство не смогло обнаружить преамбулу P1 на этапе 1015, приемное устройство возвращается к этапу 1010. Однако если приемное устройство обнаружило преамбулу P1, приемное устройство выполняет приблизительное временное регулирование и точное регулирование сдвига частоты на этапе 1020. После этого приемное устройство выполняет корреляцию мощности, чтобы оценивать мощность активных несущих на этапе 1025, и затем определяет снова на этапе 1030, обнаружило ли оно преамбулу P1. Если приемное устройство не смогло обнаружить преамбулу P1 на этапе 1030, приемное устройство возвращается к этапу 1010, а если приемное устройство успешно приняло преамбулу P1, приемное устройство выполняет приблизительное регулирование сдвига частоты на этапе 1035. Затем приемное устройство выполняет дескремблирование с использованием последовательности дескремблирования согласно примерному варианту осуществления настоящего изобретения на этапе 1040 и выполняет дифференциальную демодуляцию, которая является процессом, обратным процессу, выполняемому схемой дифференциальной модуляции в передающем устройстве, на этапе 1045. После этого приемное устройство определяет корреляцию между преамбулами на этапе 1050 и обнаруживает сигналы S1 и S2 на этапе 1055.

Как очевидно из вышеприведенного описания, примерные варианты осуществления настоящего изобретения используют схему дифференциальной модуляции при передаче преамбулы, одного из физических каналов, в DVB-системе, тем самым уменьшая PAPR преамбулы P1, посредством разрешения проблемы увеличения PAPR с помощью скремблирования.

Хотя изобретение показано и описано со ссылкой на его конкретные примерные варианты осуществления, специалистам в данной области техники должно быть понятно, что различные изменения по форме и содержанию могут осуществляться без отступления от сущности и объема изобретения, определяемого прилагаемой формулой изобретения и ее эквивалентами.

1. Устройство для передачи преамбулы в системе цифровой широковещательной передачи видео (DVB), причем устройство содержит: первый процессор для формирования последовательности сигнализации модуляции (MSS) с использованием множества принимаемых последовательностей и для вывода модулированной последовательности посредством дифференциальной модуляции MSS; модуль скремблирования для скремблирования модулированной последовательности посредством умножения модулированной последовательности на последовательность скремблирования; и второй процессор для приема скремблированной последовательности через каждую из множества выделенных поднесущих, для преобразования принятой последовательности в сигнал временной области и для формирования и передачи преамбулы.

2. Устройство по п.1, в котором первый процессор содержит: MSS-процессор для формирования MSS с использованием множества принимаемых последовательностей и дифференциальный модулятор для дифференциальной модуляции MSS.

3. Устройство по п.1, в котором второй процессор содержит: модуль выделения несущих для приема скремблированной последовательности через каждую из множества выделенных поднесущих; процессор обратного быстрого преобразования Фурье (IFFT) для преобразования скремблированной последовательности, принятой через каждую из множества выделенных поднесущих, в сигнал временной области и формирователь преамбулы для формирования и передачи преамбулы.

4. Устройство по п.1, в котором модулированная последовательность и последовательность скремблирования имеют одинаковую длину.

5. Устройство по п.1, в котором последовательность скремблирования формируется с использованием псевдослучайной двоичной последовательности (PRBS).

6. Устройство по п.1, в котором последовательность скремблирования сохраняется в таблице поиска.

7. Устройство по п.1, в котором дифференциальная модуляция MSS содержит модуляцию на основе дифференциальной двухпозиционной фазовой манипуляции (DBPSK).

8. Способ для передачи преамбулы в системе цифровой широковещательной передачи видео (DVB), при этом способ содержит этапы, на которых: формируют последовательность сигнализации модуляции (MSS) с использованием множества принимаемых последовательностей; выводят модулированную последовательность; скремблируют модулированную последовательность посредством умножения модулированной последовательности на последовательность скремблирования; принимают скремблированную последовательность через каждую из множества выделенных поднесущих; преобразуют принятую последовательность в сигнал временной области и формируют и передают преамбулу.

9. Способ по п.8, в котором вывод модулированной последовательности содержит этап, на котором дифференциально модулируют MSS.

10. Способ по п.8, в котором передача преамбулы содержит этапы, на которых: принимают скремблированную последовательность через каждую из множества выделенных поднесущих; преобразуют скремблированную последовательность, принятую через каждую из множества выделенных поднесущих, в сигнал временной области и формируют и переда