Устройство формирования видеосигнала от кмоп-матрицы

Иллюстрации

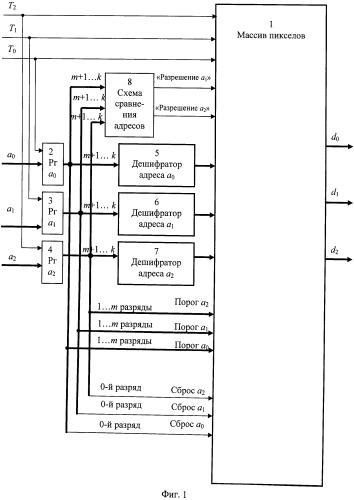

Показать всеИзобретение относится к области телевизионной техники, предназначено для формирования видеосигнала изображения объектов от фотоэлектрической КМОП-матрицы с цифровыми пикселами (Digital Pixel Sensor, DPS). Техническим результатом является возможность съема видеоинформации одновременно с разных участков фотосенсора с разными режимами накопления светового потока на этих участках при различной контрастной освещенности объектов. Результат достигается тем, что устройство содержит массив 1 пикселов, первый регистр 2 адреса, первый дешифратор 5 адреса, первую шину синхросигнала, а также второй 3 и третий 4 регистры адресов, второй 6 и третий 7 дешифраторы адресов, вторую и третью шины синхросигналов, с первой по третью шины выходных данных, при этом нулевые разряды трех регистров адреса подключены к соответствующим шинам сброса цифровых пикселов, с первых по m-е разряды - к соответствующим пороговым шинам пикселов, с m+1 по k-е разряды - к соответствующим входам схемы 8 сравнения адресов и соответствующим трем дешифраторам адресов. Шины синхросигналов подключены к соответствующим входам массива пикселов, а шины выходных данных - к соответствующим выходам пикселов, первый и второй выходы схемы сравнения адресов, соответствующие сигналам разрешения первого и второго адресов, подключены к соответствующим шинам массива пикселов. 2 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к области телевизионной техники, предназначено для формирования видеосигнала изображения объектов от фотоэлектрической КМОП-матрицы с цифровыми пикселами (Digital Pixel Sensor, DPS) и может быть использовано в телевизионных системах различного назначения.

Известна управляемая контроллером 1.3-мегапиксельная фотоэлектрическая КМОП-матрица МТ9М413 [1, 1.3-MEGAPIXEL CMOS ACTIVE-PIXEL DIGITAL IMAGE SENSOR. Micron Part Number: T9M413C36STC, http://nevael.ru/sensor_mt9m413c36stc, http://www.micron.com/products/partdetail?part=MT9M413C36STC], в состав которой входят массив активных пикселов с аналоговыми выходами, дешифраторы адресов строки и столбца, АЦП в каждом столбце, 10-разрядные регистры АЦП и выходные регистры, выходы которых подключены к выходным портам.

Недостатком данной матрицы является повышенные требования к частоте преобразования каждого АЦП, что приводит к увеличению «шума» преобразования, а следовательно, к уменьшению скорости съема видеоинформации.

Известна также КМОП-матрица с цифровыми пикселами [2, Твердотельная революция в телевидении: Телевизионные системы на основе приборов с зарядовой связью, систем на кристалле и видеосистем на кристалле / Под ред. А.А.Умбиталиева и А.К.Цыцулина. - М.: Радио и связь, 2006, рис.1.21, стр.67], содержащая наряду с выходными шинами регистр вертикальной развертки, мультиплексор горизонтальной развертки и массив пикселов, в составе каждого из которых имеются фотодиоды, усилители и аналого-цифровые преобразователи (АЦП).

Недостатком матрицы является невозможность съема видеоинформации одновременно с разных участков фотосенсора с разными режимами анализа этих участков.

Наиболее близким к предлагаемому решению по технической сущности и достигаемому эффекту является радиационно стойкая мегапиксельная КМОП-матрица STAR1000 [3, STAR1000 1М Pixel Radiation Hard CMOS Image Sensor, http://www.datasheetpro.com/697304_download_STAR1000-BK7_datasheet.html].

Данная фотоэлектрическая КМОП-матрица содержит массив активных пикселов, регистры адресов строки и столбца, дешифраторы адреса строки и столбца, усилители сигналов столбцов, оконечный усилитель, мультиплексор и АЦП.

Указанное устройство имеет следующие недостатки. Кроме невозможности съема видеоинформации одновременно с разных участков фотосенсора с разными режимами анализа этих участков при различной контрастной освещенности объектов, в режиме накопления исчезает разница между освещенной и неосвещенной поверхностями, что приводит к превышению максимально возможного уровня сигнала на более освещенной части объекта.

Техническим результатом заявляемого технического решения является возможность съема видеоинформации одновременно с разных участков фотосенсора с разными режимами накопления светового потока на этих участках при различной контрастной освещенности объектов.

Это достигается тем, что устройство формирования видеосигнала от КМОП-матрицы, содержащее массив пикселов, первый регистр адреса, первый дешифратор адреса, первую шину синхросигнала, отличается тем, что в него дополнительно введены второй и третий регистры адресов, второй и третий дешифраторы адресов, вторая и третья шины синхросигналов, с первой по третью шины выходных данных, при этом нулевые разряды трех регистров адреса подключены к соответствующим шинам сброса цифровых пикселов, с первых по m-е разряды - к соответствующим пороговым шинам пикселов, с m+1 по k-е разряды - к соответствующим входам схемы сравнения адресов и соответствующим трем дешифраторам адресов, выходы которых подключены к соответствующим адресным входам массива пикселов, шины синхросигналов подключены к соответствующим входам массива пикселов, а шины выходных данных - к соответствующим выходам пикселов, первый и второй выходы схемы сравнения адресов, соответствующие сигналам разрешения первого и второго адресов, подключены к соответствующим шинам массива пикселов, с первой по третью шины синхросигналов подключены к соответствующим шинам массива пикселов и синхровходам соответствующих регистров адреса.

Суть заявляемого устройства поясняется чертежами.

На фиг.1 представлена функциональная схема предлагаемого устройства формирования видеосигнала от КМОП-матрицы;

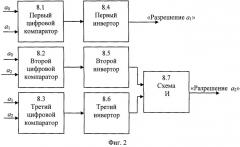

на фиг.2 - схема сравнения адресов в составе предлагаемого устройства;

на фиг.3 - функциональная схема пиксела;

на фиг.4 - временная диаграмма работы устройства.

Устройство формирования видеосигнала от КМОП-матрицы (фиг.1) содержит массив 1 пикселов, первый 2, второй 3 и третий 4 регистры адресов, первый 5, второй 6 и третий 7 дешифраторы адресов, а также схему 8 сравнения адресов.

Схема 8 сравнения адресов (фиг.2) содержит первый, второй и третий цифровые компараторы 8.1…8.3, первый, второй и третий инверторы 8.4…8.6, схему 8.7 И.

Схема каждого активного цифрового пиксела в составе массива 1 пикселов (фиг.3) содержит фотодиод 1.1, транзистор 1.2 сброса, усилитель 1.3, компаратор 1.4, счетчик 1.5, с первой по шестую схемы 1.6…1.11 И, с первой по третью m-разрядные сборки 1.12…1.14 схем И, m-разрядную сборку 1.15 схем ИЛИ, m-разрядный триггер 1.16, ЦАП 1.17, первую 1.18 и вторую 1.19 схемы ИЛИ, с первой по третью схемы 1.20…1.22 И-НЕ, с первой по третью n-разрядные сборки 1.23…1.25 схем И.

Устройство формирования видеосигнала от КМОП-матрицы работает следующим образом.

Устройство позволяет производить считывание видеоинформации с трех областей активных цифровых пикселов с независимыми частотами опроса. При этом частоты по отношению друг к другу должны быть кратными, а синхроимпульсы опроса - синфазными по положительному перепаду импульсов.

На фиг.4 приведена временная диаграмма работы устройства на примере опроса двух областей, причем период опроса Т0 в два раза меньше периода Т1. По фронту тактовых импульсов в регистры 2 и 3 адресов записываются адреса пикселов в картинной плоскости (адрес строки и столбца), с которых необходимо считать коды видеоинформации в данном такте. Последовательное формирование адресов a 0, a 1, a 2 пикселов от такта к такту для каждой области производит система высшего порядка, например, на базе компьютера автоматически или по командам оператора. При этом моменты времени появления кодов адресов на входах регистров 2…4 адресов выбираются таким образом, чтобы обеспечивалась необходимая временная диаграмма работы устройства.

Имеет место следующая структура каждого адреса: нулевой разряд - признак чтения с последующим сбросом выходного счетчика пиксела, разряды с 1 по m - коды порогов для работы компараторов в составе пиксела, разряды с m+1 по k - непосредственные коды адреса строки и столбца пиксела. Непосредственные коды адреса строки и столбца поступают на соответствующие дешифраторы 5…7 адресов a 0, a 1, a 2, на выходах которых и формируются разрешающие сигналы для строки и столбца определенного пиксела. Для увеличения скорости опроса в одной строке могут быть активизированы для опроса несколько столбцов, при этом количество разрядов для одновременного считывания данных по выходным шинам данных d0, d1 и d2 будет соответственно увеличено.

Схема 8 сравнения адресов выполняет функцию схемы приоритета. Так, при совпадении адресов высшим приоритетом обладает запрос по адресу с меньшим номером, т.е. наивысший приоритет имеет адрес a 0, а наименьший - адрес a 2. Соответственно этому вырабатываются сигналы для считывания видеоинформации по адресу a 1 - «Разрешение а 1», или по адресу а 2 - «Разрешение a 2» (фиг.2).

В каждом пикселе световой поток преобразуется в электрический заряд с помощью фотодиода 1.1 (фиг.3). С выхода усилителя 1.3 накопленный заряд поступает на компаратор 1.4, на второй вход которого последовательно через одну из трех m-разрядных сборок схем 1.12…1.14 И, m-разрядную сборку схем 1.15 ИЛИ, m-разрядный триггер 1.16 и ЦАП 1.17 поступает значение порога срабатывания компаратора. Чем выше уровень сигнала с выхода ЦАП 1.17, тем при более высоком уровне сигнала с выхода усилителя 1.3 срабатывает компаратор 1.4. Компаратор построен таким образом, что обладает гистерезисной характеристикой [4, Приемы и трюки использования встроенного компаратора в контроллерах Microchip // Алексей Сафронов, Компоненты и технологии, 2004, №7], [5, http://www.compel.ru/catalog/microcontrollers/microchip/articles/a004]. Это обеспечивает добавление единицы младшего разряда в счетчик 1.5 и полный разряд после этого емкости фотодиода 1.1. При этом m-разрядный триггер 1.16 представляет собой триггер-защелку, на вход которого с помощью схем 1.6…1.8 И и комбинации разрешающих сигналов «Разрешение a 1», «Разрешение а 2» с выхода схемы 8 сравнения адресов обеспечивается коммутация кодов одного из порогов а 0…а 2. На выходе m-разрядного триггера 1.16 код порога формируется по положительному уровню сигнала с выхода второй схемы 1.19 ИЛИ.

На эпюрах показано, как формируются сигналы для разных адресов с разными порогами адресов a 0 и а 2 на выходах усилителей 1.3, компараторов 1.4 и счетчиков 1.5.

Схемы 1.6…1.8 И и комбинация разрешающих сигналов «Разрешение а 1», «Разрешение а 2» обеспечивают коммутацию выхода счетчика 1.5 одновременно для опрашиваемого пиксела на одну из трех выходных шин данных d0…d2 через одну из первой, второй или третьей n-разрядной сборки 1.23…1.25 схем И.

Схемы 1.9…1.11 И и первая схема 1.18 ИЛИ служат для формирования сигнала сброса счетчика при наличии в нулевом разряде адреса на выходах регистров 2…4 адресов (фиг.1) признаков чтения с последующим сбросом выходного счетчика пиксела. Временную задержку, необходимую для съема потребителем информации с выходных шин данных d0…d2 перед обнулением счетчика 1.5, обеспечивают первая, вторая и третья схемы 1.20…1.22 И-НЕ. Так, на эпюрах показано, что при отсутствии признака сброса счетчика по адресу а 0 по окончании тактового синхроимпульса Т0 сброса счетчика 1.5 в k-м такте не происходит, а по адресу a 1 - наоборот, в k'-м такте происходит сброс счетчика 1.5.

Таким образом, заявляемое устройство позволяет достичь технического результата, заключающегося в возможности съема видеоинформации одновременно с разных участков фотосенсора с разными режимами накопления светового потока на этих участках при различной контрастной освещенности объектов.

1. Устройство формирования видеосигнала от КМОП-матрицы, содержащее массив пикселов, первый регистр адреса, первый дешифратор адреса, первую шину синхросигнала, отличающееся тем, что в него введены второй и третий регистры адресов, второй и третий дешифраторы адресов, вторая и третья шины синхросигналов, с первой по третью шины выходных данных, при этом нулевые разряды трех регистров адреса подключены к соответствующим шинам сброса цифровых пикселов, с первых по m-е разряды - к соответствующим пороговым шинам пикселов, с m+1 по k-е разряды - к соответствующим входам схемы сравнения адресов и соответствующим трем дешифраторам адресов, выходы которых подключены к соответствующим адресным входам массива пикселов, шины синхросигналов подключены к соответствующим входам массива пикселов, а шины выходных данных - к соответствующим выходам пикселов, первый и второй выходы схемы сравнения адресов, соответствующие сигналам разрешения первого и второго адресов, подключены к соответствующим шинам массива пикселов, с первой по третью шины синхросигналов подключены к соответствующим шинам массива пикселов и синхровходам соответствующих регистров адреса.

2. Устройство по п.1, отличающееся тем, что схема сравнения адресов содержит первый, второй и третий цифровые компараторы, первый, второй, третий инверторы и схему И, при этом код а0 нулевого адреса подается на первые входы первого и второго цифровых компараторов, код a1 первого адреса подается на второй вход первого цифрового компаратора и первый вход третьего цифрового компаратора, код а2 второго адреса подается на вторые входы второго и третьего цифровых компараторов, выходы которых соединены соответственно с входами второго и третьего инверторов, выходы которых подключены соответственно к первому и второму входам схемы И, выход которой подключен к шине разрешения второго а2 адреса, выход первого компаратора через первый инвертор подключен к шине разрешения первого a1 адреса.

3. Устройство по пп.1 и 2, отличающееся тем, что активный цифровой пиксел содержит фотодиод, транзистор сброса, соединенные последовательно усилитель, компаратор и счетчик, с первой по шестую схемы И, с первой по третью m-разрядные сборки схем И, m-разрядную сборку схем ИЛИ, m-разрядный регистр, ЦАП, первую и вторую схемы ИЛИ, с первой по третью схемы И-НЕ, с первой по третью n-разрядные сборки схем И, при этом анод диода соединен с шиной нулевого потенциала, а катод - с входом усилителя и истоком транзистора сброса, сток которого соединен с шиной положительного потенциала источника питания, а затвор - с выходом компаратора, первые, вторые и третьи входы первой, второй и третьей схем И соединены с соответствующими номеру строки и столбца пиксела выходами первого, второго и третьего дешифраторов соответственно и соответствующими шинами синхросигналов, выходы первой, второй и третьей схем И подключены к первым входам соответственно с четвертой по шестую схем И, первым входам с первой по третью n-разрядных сборок схем И, к первым входам с первой по третью m-разрядных сборок схем И, а также к первому, второму и третьему входам второй схемы ИЛИ, на вторые входы с четвертой по шестую схем И поступают сигналы сброса активных цифровых пикселов с соответствующих а0, a1 и a2 регистров адресов, на вторые входы с первой по третью m-разрядных сборок схем И поступают m-разрядные коды порогов с соответствующих регистров адресов, вторые входы с первой по третью n-разрядных сборок схем И подключены к выходу n-разрядного счетчика, на третьи входы пятой схемы И, второй m-разрядной сборки схем И, второй n-разрядной сборки подается сигнал разрешения первого адреса с первого выхода схемы сравнения адресов, а на третьи входы шестой схемы И, третьей m-разрядной сборки схем И, третьей n-разрядной сборки схем И подается сигнал разрешения второго адреса с второго выхода схемы сравнения адресов, выходы с первой по третью m-разрядных сборок схем И подключены к соответствующим входам m-разрядной сборки схем ИЛИ, выход которой последовательно через m-разрядный регистр и цифроаналоговый преобразователь подключен к второму входу компаратора, выходы с четвертой по шестую схем И подключены к первому, второму и третьему входам первой схемы ИЛИ, выход которой через последовательно соединенные первую, вторую и третью схемы И-НЕ подключен к второму входу счетчика, выход первой схемы И-НЕ подключен также к второму входу третьей схемы И-НЕ, выход второй схемы ИЛИ подключен к четвертому входу двухразрядного регистра, выходы с первой по третью сборок n-разрядных схем И являются соответствующими первой, второй и третьей выходными шинами данных.