Устройство поиска информации

Иллюстрации

Показать всеЗаявленное техническое решение относится к области электросвязи и может быть применено для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов. Техническим результатом является расширение области его применения за счет параллельной идентификации нескольких одновременно реализуемых между двумя абонентами сеансов обмена данными по протоколу. Устройство состоит из N, где N≥2, блоков селекции, N блоков хранения маски, R, где R=N-1, блоков формирования очереди ожидания и обеспечивает возможность параллельной идентификации нескольких одновременно реализуемых сеансов обмена данными по протоколу за счет согласованного функционирования разноуровневых очередей, каждая из которых предназначена для хранения признаков ожидания во входном потоке данных очередных пакетов, соответствующих тому или иному этапу реализации сеанса обмена данными, причем поиск пакетов соответствующих типов осуществляется параллельно для всех сеансов обмена данными, а необходимый порядок обнаружения пакетов обеспечивается последовательным (поэтапным) перемещением признаков ожидания между соответствующими очередями, что за счет реализации параллельно-последовательного принципа идентификации сеансов обмена данными по протоколу обеспечивает расширение области применения устройства. 1 з.п. ф-лы, 5 ил.

Реферат

Заявленное техническое решение относится к области электросвязи и может быть применено для поиска и оперативной идентификации информации в сетях передачи данных с коммутацией пакетов.

Известно устройство поиска информации - см., например, патент РФ №2115952 "Устройство поиска информации", МПК G06F 17/40, опубликованное 20.07.98. Первый аналог содержит делитель частоты, вычитающий счетчик, коммутатор, блок памяти, блоки селекции, регистр стратегии поиска, формирователь временных интервалов и блок индикации. Устройство позволяет принимать однозначное решение о наличии в потоке данных элементов протокола прикладного уровня TFTP (Trivial File Transfer Protocol) за счет синтаксического распознавания данного протокола, основанного на операции идентификации передаваемых по каналу пакетов и правил обмена ими в ходе сеанса связи. Однако данное устройство имеет ряд недостатков. Основными из них являются:

относительно низкое быстродействие, обусловленное тем, что идентификация пакетов осуществляется путем последовательного анализа значений идентификационных признаков, что затрудняет применение устройства в современных высокоскоростных сетях передачи данных;

узкая область применения, а именно только для анализа протокола TFTP на предмет соответствия наблюдаемой последовательности пакетов правилам, установленным для данного протокола.

Известно устройство поиска информации - см., например, патент РФ №2296365 "Устройство поиска информации", МПК G06F 17/30, опубликованное 27.03.2007. Второй аналог содержит N формирователей временных интервалов, где N≥1, N блоков селекции, делитель частоты, N регистров временного хранения, регистр хранения маски, блок управления и ряд других элементов, позволяющих осуществлять поиск информации. Устройство обеспечивает повышение быстродействия за счет идентификации пакетов путем параллельного анализа значений признаков идентификации. Кроме того, устройство обеспечивает идентификацию пакетов широкого спектра протоколов передачи данных, однако не позволяет реализовать идентификацию сеанса обмена данными, осуществляемого по заданному протоколу пакетной передачи данных, так как ориентировано только на обнаружение последовательностей повторяющихся пакетов с одновременным контролем допустимых временных интервалов их следования.

Из известных наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является устройство по патенту РФ №2313128 "Устройство поиска информации", МПК G06F 17/30, опубликованное 20.12.2007.

Устройство-прототип включает N≥2 блоков селекции, N блоков хранения маски, регистр стратегии поиска, формирователь временных интервалов, блок индикации, делитель частоты, тактовый вход которого является первым тактовым входом устройства, выходы "Результат сравнения" блоков селекции соединены с соответствующими входами "Результат сравнения" регистра стратегии поиска, и блок формирования адреса маски переходов. При этом в устройстве-прототипе K-разрядный, где K=(log2N)+1, выход "Код события" блока формирования адреса маски переходов подключен к K-разрядным входам "Код события" регистра стратегии поиска и блока индикации. Входы разрешения записи всех блоков хранения маски соединены между собой и являются входом разрешения записи устройства. Соответствующие разряды L-разрядных информационных входов, где L≥2, блоков селекции объединены и являются соответствующими разрядами L-разрядного информационного входа устройства. Первые L-разрядные входы "Маска 1" и "Маска 2" j-го блока хранения маски, где j=1, 2, …, N, являются j-ми первыми L-разрядными входами соответственно "Маска 1" и "Маска 2" устройства. Вторые L-разрядные выходы "Маска 1" и "Маска 2" j-го блока хранения маски подключены к соответствующим вторым L-разрядным входам "Маска 1" и "Маска 2" j-го блока селекции. Выходы "Результат сравнения" блоков селекции соединены с соответствующими входами "Результат сравнения" блока формирования адреса маски переходов. Выход делителя частоты соединен с тактовым входом формирователя временных интервалов. Вход "Начальный сброс" формирователя временных интервалов соединен с входом "Начальный сброс" блока формирования адреса маски переходов и является входом "Начальный сброс" устройства. При этом M-разрядный вход "Код времени ожидания" формирователя временных интервалов, где M≥2 - разрядность кода времени ожидания, является M-разрядным входом "Код времени ожидания" устройства, а выход формирователя временных интервалов соединен с входом "Сброс" блока формирования адреса маски переходов. Сигнальный выход регистра стратегии поиска соединен с сигнальными входами формирователя временных интервалов и блока формирования адреса маски переходов. K-разрядный адресный вход, управляющий вход, N-разрядный информационный вход и разрешающий вход регистра стратегии поиска являются соответственно K-разрядным адресным входом, управляющим входом, N-разрядным информационным входом и разрешающим входом устройства. Входы "Выбор кристалла" и "Чтение/запись" регистра стратегии поиска являются соответственно входами "Выбор кристалла" и "Чтение/запись" устройства. N-разрядный вход "Правило завершения поиска" и выход "Результат поиска" блока индикации являются соответственно N-разрядным входом "Правило завершения поиска" и выходом "Результат поиска" устройства.

Такая схема, по сравнению с устройствами-аналогами, позволяет идентифицировать пакеты и распознавать порядок их следования в соответствии с произвольными, априорно заданными правилами, что обеспечивает возможность идентификации сеанса обмена, осуществляемого по заданному протоколу пакетной передачи данных.

Однако устройство-прототип имеет недостаток - ограниченную область применения, а именно только для идентификации одиночных сеансов обмена данными между двумя абонентами, что не позволяет использовать устройство для анализа нескольких одновременно реализуемых сеансов обмена данными между абонентами. Это ограничивает применение устройства-прототипа в современных сетях передачи данных, характеризующихся значительным числом абонентов (узлов) и высокой интенсивностью одновременно реализуемых сеансов обмена между ними. Указанный недостаток обусловлен особенностью алгоритма функционирования устройства-прототипа, предполагающего переход после идентификации очередного пакета в сеансе обмена к поиску (обнаружению) следующего пакета, ожидаемого в соответствии с заданным сценарием поиска, что исключает возможность идентификации пакетов, принадлежащих другим одновременно реализуемым между абонентами сеансам обмена данными по анализируемому протоколу.

Целью заявленного технического решения является разработка устройства поиска информации, обеспечивающего расширение области его применения за счет реализации параллельно-последовательного принципа идентификации сеансов обмена данными, что позволяет выявить несколько параллельно реализуемых сеансов обмена данными по протоколу.

Поставленная цель в заявленном устройстве поиска информации достигается тем, что в известном устройстве поиска информации, содержащем N≥2 блоков селекции, N блоков хранения маски, входы разрешения записи которых соединены между собой и являются входом разрешения записи устройства, L-разрядные, где L≥2, входы "Ввод маски 1" и "Ввод маски 2" j-го блока хранения маски, где j=1, 2, …, N, являются j-ми L-разрядными входами соответственно "Ввод маски 1" и "Ввод маски 2" устройства, L-разрядные выходы "Маска 1" и "Маска 2" j-го блока хранения маски подключены к соответствующим L-разрядным входам "Маска 1" и "Маска 2" j-го блока селекции, соответствующие разряды L-разрядных информационных входов 6 блоков селекции соединены между собой и являются соответствующими разрядами L-разрядного информационного входа 6 устройства, дополнительно введены R, где R=N-1, блоков формирования очереди ожидания 31-3R. Входы "Режим работы" 13 блоков формирования очереди ожидания (БФОО) соединены между собой и являются входом "Режим работы" 13 устройства. Первый и второй тактовые входы 4 и 5 устройства подключены соответственно к первому и второму тактовым входам каждого из блоков формирования очереди ожидания 31-3R. Выход "Результат сравнения" (i+1)-го блока селекции, где i=1, 2, …, R, соединен с входом "Результат сравнения" i-го блока формирования очереди ожидания, а выход "Результат сравнения" первого блока селекции соединен с информационным входом первого блока формирования очереди ожидания. Выход "Перенос" h-го блока формирования очереди ожидания, где h=1, 2, …, (R-1), соединен с информационным входом (h+1)-го блока формирования очереди ожидания, причем выход "Перенос" R-го блока формирования очереди ожидания является выходом "Результат поиска" устройства.

Каждый блок формирования очереди ожидания состоит из K≥2D-триггеров первой ступени 3.91-3.9K, KD-триггеров второй ступени 3.101-3.10K, K двухвходовых элементов И 3.81-3.8K, входного инвертора 3.1, инвертора результата сравнения 3.2, К двухвходовых элементов И-НЕ 3.31-3.3K, шифратора приоритетов 3.4, M инверторов 3.51-3.5M, где M=log2K, дешифратора 3.6, K-входового элемента И 3.7. Выход K-входового элемента И 3.7 является выходом "Перенос" 15R блока формирования очереди ожидания, а его p-й вход, где p=1, 2, …, K, соединен с p-м инверсным выходом дешифратора 3.6, g-й вход которого, где g=1, 2, …, M, соединен с инверсным выходом g-го инвертора 3.51-3.5M. Вход g-го инвертора соединен с g-м инверсным выходом шифратора приоритетов 3.4, p-й инверсный вход которого соединен с инверсным выходом p-го двухвходового элемента И-НЕ 3.31-3.3K. Первые входы двухвходовых элементов И-НЕ соединены между собой и подключены к инверсному выходу инвертора результата сравнения 3.2, вход которого является входом "Результат сравнения" 12R блока формирования очереди ожидания. Второй вход p-го двухвходового элемента И-НЕ соединен с выходом p-го D-триггера второй ступени 3.101-3.10K, при этом выход s-го D-триггера второй ступени, где s=1, 2, …, (K-1), соединен со вторым входом (s+1)-го двухвходового элемента И. Первый вход (s+1)-го двухвходового элемента И соединен с s-м инверсным выходом дешифратора 3.6. Выход p-го двухвходового элемента И 3.81-3.8K соединен с первым информационным входом p-го D-триггера первой ступени 3.91-3.9K, выход которого соединен с первым информационным входом р-го D-триггера второй ступени. Вторые информационные входы D-триггеров первой ступени соединены между собой и являются первым тактовым входом 4 блока формирования очереди ожидания. Вторые информационные входы D-триггеров второй ступени соединены между собой и являются вторым тактовым входом 5 блока формирования очереди ожидания. Первый вход первого двухвходового элемента И 3.81 является входом "Режим работы" 13, второй вход первого двухвходового элемента И 3.81 подключен к инверсному выходу входного инвертора 3.1, вход которого является информационным входом 14R блока формирования очереди ожидания.

Заявленные объекты изобретения поясняются чертежами, на которых показаны:

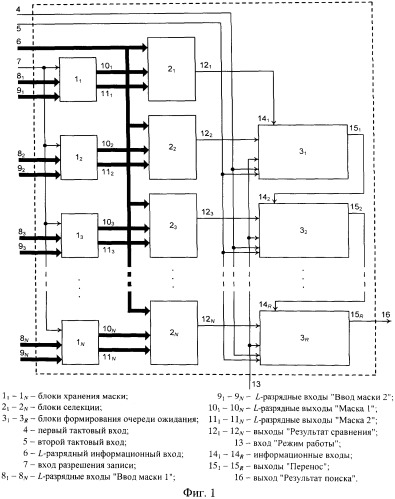

на фиг.1 - общая структурная схема устройства поиска информации;

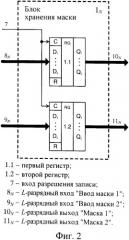

на фиг.2 - схема блока хранения маски;

на фиг.3 - схема блока селекции;

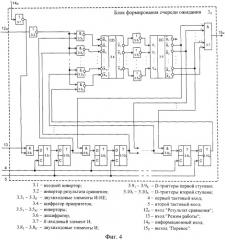

на фиг.4 - схема блока формирования очереди ожидания;

на фиг.5 - пример порядка следования пакетов при обмене данными между двумя абонентами (узлами) по нескольким одновременно реализуемым сеансам обмена данными по протоколу.

Устройство (см. фиг.1) состоит из N≥2 блоков хранения маски 11-1N, N блоков селекции 21-2N, R, где R=N-1, блоков формирования очереди ожидания 31-3R.

Элементы соединены между собой следующим образом (см. фиг.1). Входы разрешения записи блоков хранения маски соединены между собой и являются входом разрешения записи 7 устройства. L-разрядные, где L≥2, входы "Ввод маски 1" и "Ввод маски 2" j-го блока хранения маски, где j=1, 2, …, N, являются j-ми L-разрядными входами "Ввод маски 1" 81-8N и j-ми L-разрядными входами "Ввод маски 2" 91-9N устройства. L-разрядные выходы "Маска 1" 101-10N и L-разрядные выходы "Маска 2" 111-11N j-го блока хранения маски подключены к соответствующим L-разрядным входам "Маска 1" и "Маска 2" j-го блока селекции. Соответствующие разряды L-разрядных информационных входов блоков селекции соединены между собой и являются соответствующими разрядами L-разрядного информационного входа 6 устройства. Входы "Режим работы" блоков формирования очереди ожидания соединены между собой и являются входом "Режим работы" 13 устройства. Первый и второй тактовые входы 4 и 5 устройства подключены соответственно к первому и второму тактовым входам каждого из блоков формирования очереди ожидания. Выход "Результат сравнения" (i+1)-го блока селекции, где i=1, 2, …, R, соединен с входом "Результат сравнения" i-го блока формирования очереди ожидания, а выход "Результат сравнения" первого блока селекции соединен с информационным входом первого блока формирования очереди ожидания. Выход "Перенос" h-го блока формирования очереди ожидания, где h=1, 2, …, (R-1), соединен с информационным входом (h+1)-го блока формирования очереди ожидания, причем выход "Перенос" R-го блока формирования очереди ожидания является выходом "Результат поиска" 16 устройства.

Блоки хранения маски 11-1N, предназначены для хранения битовых масок, используемых для идентификации элементов входящего потока данных. Схема реализации блока хранения маски известна и показана, например в устройстве по патенту РФ №2313128 "Устройство поиска информации", МПК G06F 17/30, опубликованное 20.12.2007, бюллетень №35. В частности его схема, показанная на фиг.2, состоит из первого 1.1 и второго 1.2 регистров. Информационные выходы первого регистра 1.1 являются соответствующими разрядами 1-разрядного выхода "Маска 1" блока хранения маски, а информационные выходы второго регистра 1.2 являются соответствующими разрядами L-разрядного выхода "Маска 2" блока хранения маски. Входы разрешения записи первого 1.1 и второго 1.2 регистров соединены между собой и являются входом разрешения записи 7 блока хранения маски. Информационные входы первого регистра 1.1 являются соответствующими разрядами L-разрядного входа "Ввод маски 1" блока хранения маски, а информационные входы второго регистра 1.2 являются соответствующими разрядами L-разрядного входа "Ввод маски 2" блока хранения маски.

Первый 1.1 и второй 1.2 регистры предназначены для хранения соответственно первой и второй битовой маски. Описание работы и схема таких регистров известны и приведены, например, в книге: П.П.Мальцев, Н.С.Долидзе и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с.57-62.

Блоки селекции 21-2N предназначены для идентификации элементов входящего потока данных и формирования сигнала в случае соответствия поступившего элемента входного потока данных заданному типу. Схема реализации блока селекции известна и показана, например, в устройстве по патенту РФ №2313128 "Устройство поиска информации" МПК G06F 17/30, опубликованное 20.12.2007, бюллетень №35. В частности, его схема, показанная на фиг.3, состоит из первой и второй групп двухвходовых элементов И 2.11-2.1L, 2.21-2.2L по L элементов в каждой группе, компаратора 2.3, инвертора 2.4, инверсный выход которого является выходом "Результат сравнения" 12N блока селекции. Вход инвертора подключен к выходу равенства компаратора. При этом i-й, где i=1, 2, …, L, вход первой группы информационных входов компаратора соединен с выходом i-го двухвходового элемента И первой группы двухвходовых элементов И 2.11-2.1L, а i-й вход второй группы информационных входов компаратора соединен с выходом i-го двухвходового элемента И второй группы двухвходовых элементов И 2.21-2.2L. Первый вход i-го двухвходового элемента И первой группы двухвходовых элементов И 2.11-2.1L, является i-м разрядом L-разрядного информационного входа 6 блока селекции. Второй вход i-го двухвходового элемента И первой группы двухвходовых элементов И 2.11-2.1L соединен с первым входом i-го двухвходового элемента И второй группы двухвходовых элементов И 2.21-2.2L и является i-м разрядом L-разрядного входа "Маска 1" 10N блока селекции, а второй вход i-го двухвходового элемента И второй группы двухвходовых элементов И 2.21-2.2L является i-м разрядом L-разрядного входа "Маска 2" 11N блока селекции.

Двухвходовые элементы И 2.11- 2.1L и 2.21- 2.2L предназначены для коммутации на свой выход сигнала на одном из своих входов при наличии разрешающего сигнала высокого логического уровня на другом его входе. Схема реализации двухвходового элемента И известна. См., например, в книге: П.П.Мальцев, Н.С.Долидзе и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с.30-32.

Компаратор 2.3 предназначен для сравнения двоичных кодов установленных на его входах и формирования результата сравнения. Описание работы и схема компаратора приведены, например, в книге: В.Л.Шило. Популярные микросхемы ТТЛ. - М.: АРГУС, 1993, с.183-184.

Инвертор 2.4 предназначен для инвертирования сигнала, поступающего на его вход. Схема реализации инвертора известна. См., например, в книге: И.И.Петровский и др. Логические ИС КР1533, КР1554. Справочник в двух частях. Часть 2. - М.: Бином, 1993, с.272-273.

Блоки формирования очереди ожидания 31-3R (см. фиг.4) предназначены для приема сигналов об идентификации элементов входного потока данных соответствующих типов, формирования на основании поступивших сигналов признака (маркера) ожидания очередного в соответствии с правилами протокола элемента потока данных (пакета), хранения сформированных маркеров в виде очереди ожидания и последующего удаления маркеров из очереди по истечении заданного времени ожидания или при поступлении сигнала об идентификации ожидаемого пакета с одновременным формированием на своем выходе соответствующего сигнала. Блок формирования очереди ожидания может быть реализован по любой известной схеме с учетом описанных функций. В частности, его схема, показанная на фиг.4, состоит из K≥2 D-триггеров первой ступени 3.91-3.9K, K D-триггеров второй ступени 3.101-3.10K, K двухвходовых элементов И 3.81-3.8K, входного инвертора 3.1, инвертора результата сравнения 3.2, K двухвходовых элементов И-НЕ 3.31-3.3K, шифратора приоритетов 3.4, M инверторов 3.51-3.5M, где M=log2K, дешифратора 3.6, K-входового элемента И 3.7.

Элементы соединены между собой следующим образом (см. фиг.4). Выход K-входового элемента И 3.7 является выходом "Перенос" 15R блока формирования очереди ожидания, а его p-й вход, где p=1, 2, …, K, соединен с p-м инверсным выходом дешифратора 3.6, g-й вход которого, где g=1, 2, …, M, соединен с инверсным выходом g-го инвертора 3.51-3.5M, вход которого соединен с g-м инверсным выходом шифратора приоритетов 3.4, p-й инверсный вход которого соединен с инверсным выходом p-го двухвходового элемента И-НЕ 3.31-3.3K. Первые входы двухвходовых элементов И-НЕ 3.31-3.3K объединены между собой и подключены к инверсному выходу инвертора результата сравнения 3.2, вход которого является входом "Результат сравнения" 12R блока формирования очереди ожидания. Второй вход p-го двухвходового элемента И-НЕ соединен с выходом p-го D-триггера второй ступени 3.101-3.10K, при этом выход s-го D-триггера второй ступени, где s=1, 2, …, (K-1), соединен со вторым входом (s+1)-го двухвходового элемента И, первый вход которого соединен с s-м инверсным выходом дешифратора 3.6. Выход p-го двухвходового элемента И 3.81-3.8K соединен с первым информационным входом p-го D-триггера первой ступени 3.91-3.9K. Выход p-го D-триггера первой ступени соединен с первым информационным входом p-го D-триггера второй ступени 3.101-3.1.K. Вторые информационные входы D-триггеров первой ступени 3.91-3.9K соединены между собой и являются первым тактовым входом 4 блока формирования очереди ожидания, вторые информационные входы D-триггеров второй ступени 3.101-3.10K соединены между собой и являются вторым тактовым входом 5 блока формирования очереди ожидания. Первый вход первого двухвходового элемента И 3.81 является входом "Режим работы" 13 устройства, второй вход первого двухвходового элемента И 3.81 подключен к инверсному выходу входного инвертора 3.1, вход которого является информационным входом 14R блока формирования очереди ожидания.

D-триггеры первой ступени 3.91-3.9K и D-триггеры второй ступени 3.101-3.10K предназначены для хранения логического значения сигналов, поступивших на их информационные входы. Схема реализации D-триггеров известна. См., например, в книге: П.П.Мальцев, Н.С.Долидзе и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с.50-51.

Двухвходовые элементы И 3.81-3.8K предназначены для коммутации на свой выход сигнала на одном из своих входов при наличии разрешающего сигнала высокого логического уровня на другом его входе. Схема реализации двухвходового элемента И известна. См., например, в книге: П.П.Мальцев, Н.С.Долидзе и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с.30-32.

Входной инвертор 3.1, инвертор результата сравнения 3.2, инверторы 3.51-3.5M предназначены для инвертирования сигналов, поступающих на их вход. Схема реализации инвертора известна. См., например, в книге: И.И.Петровский и др. Логические ИС КР1533, КР1554. Справочник в двух частях. Часть 2. - М.: Бином, 1993, с.272-273.

Двухвходовые элементы И-НЕ 3.31-3.3K предназначены для коммутации на свой выход сигнала на одном из своих входов при наличии разрешающего сигнала высокого логического уровня на другом его входе с одновременным инвертированием выходного сигнала. Схема реализации двухвходового элемента И-НЕ известна. См., например, в книге: П.П.Мальцев, И.С.Долидзе и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с.30-32.

Шифратор приоритетов 3.4 предназначен для преобразования сигнала низкого уровня на одном или нескольких его входах в соответствующий двоичный код на его выходах, причем преобразование осуществляется с учетом приоритетов сигналов, соответствующих номерам входов. Схема реализации шифратора приоритетов известна. См., например, в книге: В.Л.Шило. Популярные цифровые микросхемы: справочник. - М.: Радио и связь, 1987, с.139-142.

Дешифратор 3.6 предназначен для преобразования двоичного кода на его входе в сигнал низкого уровня на одном из его выходов, номер которого соответствует числу в двоичном коде, установленному на входе дешифратора. Схемы реализации дешифратора известны. См., например, в книге: П.П.Мальцев, Н.С.Долидзе и др., Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994, с.41-47.

K-входовый элемент И 3.7 предназначен для формирования сигнала низкого уровня на своем выходе при наличии сигнала низкого уровня хотя бы на одном из его входов. Схема реализации K-входового элемента И известна. См., например, в книге: И.И.Петровский и др. Логические ИС КР1533, КР1554 Справочник в двух частях. Часть 2. - М.: Бином, 1993, с.262-267.

Заявленное устройство работает следующим образом. В устройстве реализован параллельно-последовательный принцип идентификации сеансов обмена данными между двумя абонентами, обеспечиваемый системой согласованно функционирующих разноуровневых очередей, каждая из которых предназначена для хранения признаков ожидания (далее маркеров) во входном потоке данных очередных блоков двоичной информации (пакетов протокола), соответствующих тому или иному этапу реализации сеанса обмена данными, причем поиск блоков двоичной информации (БДИ) соответствующих типов осуществляется параллельно для всех сеансов обмена данными, а необходимый порядок обнаружения БДИ обеспечивается последовательным (поэтапным) перемещением маркеров между соответствующими очередями.

Особенностью устройства является последовательное хранение в очереди нескольких маркеров ожидания БДИ соответствующего типа, что в отличие от устройства-прототипа позволяет выявить несколько параллельно реализуемых между двумя абонентами сеансов обмена данными по протоколу. Пример порядка следования БДИ при обмене данными между двумя абонентами по нескольким одновременно реализуемым сеансам обмена данными по протоколу приведен на фиг.5.

Распознавание каждого сеанса обмена данными по протоколу между двумя абонентами (узлами) реализуется на основе сигнатурного подхода к идентификации отдельных элементов поступающего потока данных - БДИ, с одновременным контролем порядка их поступления на предмет соответствия заданным правилам.

Идентификация БДИ в устройстве осуществляется путем сравнения значений идентификационных битов БДИ с предварительно заданными эталонными значениями. Под идентификационными битами БДИ понимаются биты, значения которых позволяют однозначно идентифицировать тип БДИ. Для различных типов БДИ количество идентификационных битов, их значения и позиции в рамках БДИ могут различаться. В связи с этим каждому типу БДИ ставятся в соответствие пара битовых масок - первая битовая маска и вторая битовая маска. Каждая битовая маска состоит из L разрядов, где L - максимально возможное количество разрядов в БДИ. Разряды битовых масок могут принимать значение логического нуля или логической единицы. Первая битовая маска используется для указания позиций идентификационных битов БДИ. В разрядах первой битовой маски, которые соответствуют разрядам идентификационных битов БДИ, должны быть установлены значения логической единицы. Во всех остальных разрядах битовой маски должны быть установлены значения логического нуля. Вторая битовая маска предназначена для задания эталонных значений, которым должны соответствовать значения идентификационных битов. В разрядах второй битовой маски, не являющихся идентификационными, могут быть установлены произвольные значения. При этом идентификация БДИ осуществляется путем сравнения результатов выполнения логической операции "И" над соответствующими разрядами поступившего БДИ и первой битовой маски с результатами выполнения логической операции "И" над соответствующими разрядами второй и первой битовых масок.

Идентификация БДИ осуществляется в блоках селекции. Каждый блок селекции обеспечивает идентификацию только того типа БДИ, который задан соответствующей парой битовых масок. Порядковый номер блока селекции соответствует порядковому номеру типа БДИ в обнаруживаемом фрагменте сеанса обмена данными по протоколу пакетной передачи данных.

При поступлении БДИ одного из заданных типов на вход устройства на выходе соответствующего блока селекции формируется сигнал. Последовательная (конвейерная) обработка сигналов от блоков селекции позволяет учесть очередность следования БДИ заданных типов. Контроль порядка следования БДИ на предмет соответствия заданной последовательности заключается в последовательной фиксации сигналов "срабатывания j-го блока селекции только после фиксации сигнала "срабатывания" (j-1)-го блока селекции. При этом формируется маркер ожидания очередного (j+1)-го в соответствии с правилами поиска типа БДИ.

Формирование очереди ожидания, обеспечивающей хранение нескольких маркеров ожидания БДИ определенного типа с одновременным контролем допустимого времени ожидания, реализуется блоком формирования очереди ожидания. В основе функционирования БФОО лежит регистр последовательного сдвига, реализованный в виде последовательно соединенных регистров промежуточного хранения, каждый из которых состоит из пары последовательно соединенных D-триггеров - D-триггера первой ступени и D-триггера второй ступени, обеспечивающих хранение одного маркера. Перенос маркера из одного регистра промежуточного хранения в другой осуществляется в два такта при поступлении сигналов логической единицы на первый тактовый вход 4 и второй тактовый вход 5 устройства, соединенные со вторыми информационными входами соответственно D-триггеров первой и второй ступени. Кроме того, возможность переноса маркера определяется наличием разрешающего сигнала логической единицы на первом входе соответствующего двухвходового элемента И, коммутирующего перемещение маркера. Маркер ожидания БДИ очередного типа формируется в блоке формирования очереди ожидания только в том случае, если последовательно были зафиксированы сигналы об обнаружении типов БДИ, порядок следования которых в заданной последовательности определен правилами поиска.

При поступлении на информационный вход БФОО сигнала низкого уровня в первый регистр промежуточного хранения БФОО записывается маркер. Перемещение маркера от входа очереди к ее выходу обеспечивается тактовыми импульсами, поступающими на первый и второй тактовые входы устройства. Перемещение маркера ожидания БДИ j-го типа прекращается при поступлении на вход "Результат сравнения" БФОО сигнала "срабатывания" j-го блока селекции или достижения маркером последнего в очереди регистра промежуточного хранения. В первом случае маркер обнуляется и формируется сигнал на выходе "Перенос" (признак обнаружения БДИ j-го типа) БФОО, обеспечивающий размещение маркера ожидания ВДИ (j+1)-го типа в первом регистре промежуточного хранения следующего БФОО. Во втором случае указанный сигнал не формируется. Появление сигнала "Перенос" на выходе последнего БФОО свидетельствует об обнаружении заданной последовательности БДИ.

Для пояснения работы устройства рассмотрим следующие режимы его функционирования:

инициализацию устройства;

работу устройства при поступлении подлежащих анализу БДИ.

Инициализация устройства включает в себя проведение следующих операций:

установка первой и второй битовых масок;

начальный сброс БФОО.

Установка первой и второй битовых масок, обеспечивающих идентификацию каждого из N типов БДИ, осуществляется в соответствующие блоки хранения маски 11-1N. Для этого на L-разрядных входах "Ввод маски 1" 81-8N устройства устанавливают соответствующие первые битовые маски, а на L-разрядных входах "Ввод маски 2" 91-9N устройства устанавливают соответствующие вторые битовые маски. На входе разрешения записи 7 устройства устанавливают разрешающий сигнал логической единицы, который поступает на входы инициализации первых 1.1 и вторых 1.2 регистров каждого из N блоков хранения маски и обеспечивает запись первых и вторых битовых масок в соответствующие регистры. По окончании операции записи на входе разрешения записи 7 устройства устанавливают сигнал логического нуля. В результате выполненных действий на L-разрядных выходах "Маска 1" 101-10N и L-разрядных выходах "Маска 2" 111-11N устанавливаются соответственно логические уровни сигналов, указывающие позиции идентификационных битов БДИ и логические уровни сигналов, указывающие значения в разрядах идентификационных битов БДИ.

Начальный сброс БФОО осуществляется следующим образом.

На входе "Режим работы" 13 устройства устанавливается сигнал логического нуля. Сигнал логического нуля, поступивший на первый вход первого двухвходового элемента И 3.81, коммутируется на вход первого D-триггера первой ступени 3.91. По тактовым импульсам, поступающим на первый и второй тактовые входы 4 и 5 устройства, значение логического нуля записывается во все D-триггеры первой и второй ступени всех БФОО. Значение логического нуля с выходов D-триггеров второй ступени подается на соответствующие вторые входы двухвходовых элементов И-НЕ 3.31-3.3K. Двухвходовые элементы И-НЕ 3.31-3.3K, на входы которых поступил сигнал логического нуля, формируют на входе шифратора приоритетов 3.4 сигналы логической единицы. По прохождении K тактовых импульсов на всех входах шифратора приоритетов 3.4 устанавливаются значения логической единицы. В соответствии с таблицей истинности шифратора приоритетов 3.4 на его выходах устанавливается двоичный код, во всех разрядах которого установлены значения логической единицы. Двоичный код через инверторы 3.51-3.5M поступает на вход дешифратора 3.6. Так как на всех входах дешифратора 3.6 установлены значения логического нуля, то в соответствии с таблицей истинности дешифратора на его выходах устанавливаются значения логической единицы. С выходов дешифратора 3.6 сигналы логической единицы поступают на соответствующие первые входы двухвходовых элементов И 3.82-3.8K. Одновременно с выходов дешифратора 3.6 сигналы логической единицы поступают на соответствующие входы K-входового элемента И 3.7, на выходе которого формируется сигнал логической единицы. Таким образом, в результате проведенной операции начального сброса БФОО на выходах "Перенос" 15R всех БФОО устанавливаются значения логической единицы.

После выполнения указанных операций устройство готово к работе.

Работа устройства при поступлении подлежащих анализу БДИ заключается в следующем.

При поступлении БДИ, подлежащего анализу, на L-разрядном информационном входе 6 устройства устанавливаются логические значения сигналов, соответствующие значениям двоичных разрядов БДИ. Момент времени, соответствующий установке значений двоичных разрядов БДИ на L-разрядном информационном входе 6 устройства, обозначим как T1. С L-разрядного информационного входа 6 устройства логические значения сигналов соответствующих разрядов БДИ поступают на L-разрядные информационные входы блоков селекции 21-2N. Каждый блок селекции осуществляет идентификацию БДИ соответствующего типа. Тип БДИ определяется первой и второй битовыми масками, поступающими с L-разрядного выхода "Маска 1" и L-разрядного выхода "Маска 2" блока хранения маски соответственно на L-разрядный вход "Маска 1" и L-разрядный вход "Маска 2" блока селекции. В компараторе 2.3 каждого блока селекции 21-2N происходит сравнение логических значений сигналов идентификационных битов поступившего БДИ с значениями логических значений сигналов соответствующих битов второй битовой маски. Выделение идентификационных битов осуществляется в первой и второй группах двухвходовых элементов И 2.11-2.1L, 2.21-2.2L каждого блока селекции на основании соответствующей первой битовой маски. В случае равенства сравниваемых значений на выходе равенства "А=В" компаратора 2.3 установится значение логической единицы, в противном случае - значение логического нуля. Логическое значение, соответствующее результату сравнения, с выхода "А=В" компаратора 2.3 инвертируется инвертором 2.4 и поступает на выход "Результат сравнения" блока селекции. Таким образом, при поступлении на вход устройства БДИ, соответствующего одному из ожидаемых типов БДИ, на выходе "Результат сравнения" блока селекции, в котором обнаружено совпадение значений идентификационных битов поступившего БДИ с соответствующими значениями второй битовой маски, будет установлено значение логического нуля, а на выходах "Результат сравнения" всех остальных блоков селекции - значение логической единицы. Сигнал с выхода "Результат сравнения" первого блока селекции поступает на информационный вход первого блока формирования очереди ожидания, а сигналы с выходов "Результат сравнения" j-х блоков селекции, где j=2, 3, …, N, поступают на входы "Результат сравнения" (j-1)-х блоков формирования очереди ожидания. При поступлении на вход устройства БДИ, не соответствующего ни одному из ожидаемых (заданных масками) типов идентифицируемых БДИ, на выходах "Результат сравнения" 121-12N всех блоков селекции будет установлено значение логической единицы. Момент времени, соответствующий установке логических значений сигналов на выходах "Результат сравнения" блоков селекции, обозначим как T2.

Момент времени T2, определяется как:

где: T1 - момент времени установки логических значений разрядов БДИ на L-разрядном информационном входе 6 устройства,

ΔT2 - время задержки срабатывания блока селекции.

Время ΔT2, определяется как:

где: ΔT2.1 - время задержки срабатывания двухвходово