Параллельная вычислительная система с программируемой архитектурой

Иллюстрации

Показать всеИзобретение относится к области вычислительной техники и может использоваться в высокопроизводительных системах обработки больших массивов данных, передаваемых по высокоскоростным каналам передачи (приема), в том числе и в режиме реального времени. Технический результат - повышение быстродействия. Параллельная вычислительная система с программируемой архитектурой (далее по тексту ПВС), содержащая первый, второй, третий и четвертый микропроцессоры, ОЗУ, ПЗУ, первая и вторая группы входов ПВС соединены с первой группой входов системного контроллера и первыми группами входов первого, второго, третьего и четвертого микропроцессоров, отличающаяся тем, что в ПВС дополнительно введены второе, третье и четвертое ПЗУ, второе, третье и четвертое, пятое и шестое ОЗУ, системный контроллер, первый, второй, третий и четвертый приемо-передатчики LVDS, первый, второй, третий и четвертый приемопередатчики Fibre channal TLK 1201, контроллер LINK Fibre channal, генератор на 106,25 МГц, генератор на 10 МГц, генератор на 40 МГц, узел сброса по питанию, контроллер LINK MKO, первый и второй приемопередатчики МКО HI-1574, первый LINK коммутатор, второй LINK коммутатор и соответствующие связи между узлами ПВС. 16 з.п. ф-лы, 57 ил.

Реферат

Изобретение относится к области вычислительной техники и может использоваться в высокопроизводительных системах обработки больших массивов данных, передаваемых по высокоскоростным каналам передачи (приема), в том числе и в режиме реального времени.

Известна параллельная вычислительная система с программируемой архитектурой, включающая параллельный процессор, который содержит матрицу процессорных элементов, и ОЗУ, дополнительно снабженная первой коммуникационной средой и N параллельными процессорами, причем каждый параллельный процессор дополнительно содержит управляющий процессор, системную шину, служебное ОЗУ, буферное ОЗУ и узел загрузки, первая группа входов-выходов которого соединена с первой коммуникационной средой, при этом вторая группа входов-выходов узла загрузки соединена с группой информационных входов-выходов буферного ОЗУ, группа управляющих входов которого соединена с первой группой управляющих выходов узла загрузки, третья группа входов-выходов которого соединена с группой информационных входов-выходов служебного ОЗУ, группа управляющих входов которого соединена со второй группой управляющих выходов узла загрузки, четвертая группа входов-выходов которого соединена с группой информационных входов-выходов ОЗУ, группа управляющих входов которого соединена с третьей группой управляющих выходов узла загрузки, первая группа выходов которого связана с группой информационных входов матрицы процессорных элементов, группа информационных выходов которой связана с группой входов блока загрузки, группа управляющих выходов которого связана с группой управляющих входов матрицы процессорных элементов, группа управляющих выходов которой связана с группой управляющих входов блока загрузки, пятая группа входов-выходов которого соединена с системной шиной, которая также соединяется с группой входов-выходов управляющего процессора. [1]

Существенным недостатком такой системы является жесткая взаимосвязь между собой отдельных параллельных процессоров, что при решении многих задач обусловливает низкую производительность системы в целом, особенно в случае отказов в работе некоторых процессоров, а также затрудняет наращивание производительности системы путем подключения дополнительных блоков. Кроме того, большое число параллельных процессоров, работающих с одним блоком управления, снижает эффективность их использования. Стоит отметить также, что параллельные процессоры неэффективны для задач, при решении которых требуется жестко последовательное выполнение, друг за другом, отдельных модулей и команд программы, реализующих отдельные части задачи.

Увеличение же числа параллельных процессоров наряду с введением в состав каждого параллельного процессора управляющего процессора, введение в состав системы вычислительных узлов, состоящих из процессоров другого типа (последовательных), объединенных одной или несколькими коммуникационными средами, позволяет наиболее быстро и эффективно выполнять сложные программы.

Наиболее близкой к описываемому изобретению (прототип) является система Т2-РМС с качественной мультиобработкой, масштабируемостью и скоростной пропускной способностью ввода-вывода [2], содержащая четыре процессора Analog Devices ADSP-TS20/S Tiger SHARC DSPs, ОЗУ, ПЗУ, контроллер ввода-вывода, который обеспечивает прием и передачу данных с внешними устройствами через LINK0 и LINK1 порты и обработку прерываний, контроллер шины PCI, отладчик Jtag, группа входов-выходов которого соединена с группами входов-выходов контроллера ввода-вывода, первого, второго, третьего и четвертого процессоров, связанных между собой контроллер шины PCI, отладчик Jtag, группа входов-выходов которого соединена с группами входов-выходов контроллера ввода-вывода, первого, второго, третьего и четвертого процессоров, связанных между собой двунаправленной 64 разрядной cluster шиной, которая соединена с ОЗУ и контроллером PCI, 8-разрядная периферийная шина которого соединена с ПЗУ и контроллером ввода-вывода, четыре двунаправленных LINK0 порта соединены с двунаправленными LINK0 портами четырех процессоров, двунаправленные LINK1 порты которых соединены с четырьмя двунаправленными LINK1 портами контроллера ввода-вывода, группа входов-выходов прерываний и флагов которого соединена с первой группой входов-выходов четырех процессоров, вторая группа входов-выходов прерываний и флагов которых соединена с контроллером PCI, 64-разрядная шина PCI которого является 64-разрядной шиной PCI системы Т2-РМС, шина расширения РМС которой соединена с шиной РМС контроллера ввода-вывода, причем двунаправленный LINK2 порт первого процессора соединен с двунаправленным LINK3 портом четвертого процессора, двунаправленный LINK2 порт которого соединен с двунаправленным LINK3 портом третьего процессора, двунаправленный LINK2 порт которого соединен с двунаправленным LINK3 портом второго процессора, двунаправленный LINK2 порт которого соединен с двунаправленным LINK3 портом первого процессора.

Недостатком такой системы является низкое быстродействие за счет обращения четырех процессоров к одной памяти ОЗУ, жесткая взаимосвязь между собой отдельных параллельных процессоров, обусловливает низкую производительность системы в целом, особенно в случае отказов некоторых процессоров. Связь между процессорами полудуплексная с необходимостью согласования направления передачи данных.

Задачей изобретения является повышение быстродействия за счет введения ОЗУ каждому процессору, прием и передача данных (дуплексный режим) по высокоскоростным каналам приема и передачи, организация высоких скоростей передачи данных между процессорами, высококачественная обработка принятых данных, устойчивая к отказам и сбоям в системе передачи данных в реальном времени.

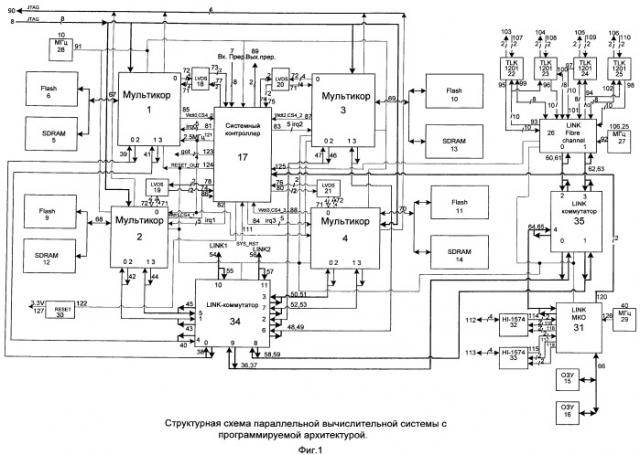

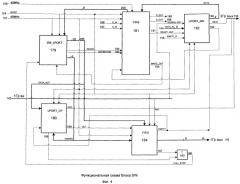

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.1-55, где:

- на фиг.1 представлена структурная схема параллельной вычислительной системы с программируемой архитектурой (далее по тексту ПВС);

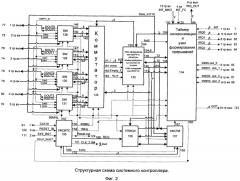

- на фиг.2 представлена структурная схема системного контроллера;

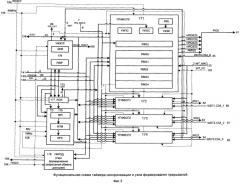

- на фиг.3 представлена функциональная схема таймера синхронизации и узла формирования прерываний;

- на фиг.4 представлена функциональная схема блока SW;

- на фиг.5 представлена функциональная схема узла SW;

- на фиг.6 представлена функциональная схема LPORT_OY;

- на фиг.7 представлена функциональная схема узла SW_LPORT;

- на фиг.8 представлена функциональная схема узла LPORT_SW;

- на фиг.9 представлена функциональная схема узла формирования сигнала программной инициализации;

- на фиг.10 представлена функциональная схема узла с управляемым разрешением счета (REG_COUNT);

- на фиг.11 представлена функциональная схема узла формирования сигналов инициализации и тактовых сигналов;

- на фиг.12 представлена функциональная схема узла формирования задержанного сигнала реинициализации;

- на фиг.13 представлена функциональная схема узла коммутации;

- на фиг.14 представлена функциональная схема таймера синхронизации;

- на фиг.15 представлена функциональная схема узла RCP-2;

- на фиг.16 представлена функциональная схема узла команд модификации.;

- на фиг.17 представлена функциональная схема узла формирования разрешения обмена данными;

- на фиг.18 представлен алгоритм работы машины состояний узла SW;

- на фиг.19 представлен алгоритм работы передатчика;

- на фиг.20, 20а, 20б представлен алгоритм работы приемника;

- на фиг.21, 21а представлен алгоритм работы МС узла LPORT_OY;

- на фиг.22,22а представлен алгоритм работы МС узла SWJ-PORT;

- на фиг.23 представлен алгоритм работы МС узла LPORT_SPW;

- на фиг.24 представлен алгоритм работы узла приема и фиксации сигналов инициализации;

- на фиг.25 представлен алгоритм работы узла коммутации;

- на фиг.26, 26а, 26б, 26в, 26г, 26д представлен алгоритм работы МС узла RCP_2;

- на фиг.27, 27а представлен алгоритм работы узла Protocol-reg;

- на фиг.28, 28а представлен алгоритм работы узла регистра команд (Cmd_reg);

- на фиг.29, 29а, 29б представлен алгоритм работы МС узла команд модификации;

- на фиг.30 представлен формат символов;

- на фиг.31 представлено DS-кодирование;

- на фиг.32 представлена диаграмма состояний интерфейса связи SpaceWire;

- на фиг.33 представлен формат регистра запросов на прерывание;

- на фиг.34 представлен формат регистра предустановки задержанных прерываний;

- на фиг.35 представлен формат регистра управления таймером синхронизации;

- на фиг.36 представлен формат информационного регистра Rinf узла УФЗСР;

- на фиг.37 представлен формат регистра предустановки RPR узла УФЗСР;

- на фиг.38 представлен формат регистров предустановки, счетчика и фиксации таймера синхронизации RPI, RTM И RFX;

- на фиг.39 представлен формат регистра предустановки программной инициализации RG3;

- на фиг.40 представлен формат регистра разрешения программной инициализации RG1, RG2;

- на фиг.41 представлена адресация регистров системного контроллера;

- на фиг.42 представлен общий вид входного сообщения протокола RCP-2;

- на фиг.43 представлен формат параметра заголовка;

- на фиг.44 представлен формат команды обмена;

- на фиг.45 представлен тип операции записи/модификации;

- на фиг.46 представлен способ задания адреса ОУ по инициативе микропроцессоров;

- на фиг.47 представлена временная диаграмма интерфейса чтения командной информации;

- на фиг.48 представлен формат выходного сообщения по протоколу RCP-2;

- на фиг.49 представлен формат параметра заголовка;

- на фиг.50 представлен формат результата обмена;

- на фиг.51 представлено поле кода ошибки;

- на фиг.52 представлено ответное сообщение при способе задания адреса СК по инициативе микропроцессоров;

- на фиг.53 представлена временная диаграмма операции чтения регистра из узла 133 RCP-2;

- на фиг.54 представлена временная диаграмма операции записи регистра из узла 133 RCP-2;

- на фиг.55 представлена временная диаграмма операции чтения-модификации-записи-чтения регистра из узла 133 RCP-2;

- на фиг.56 представлены характеристики управляющей и обрабатывающей подсистем;

- на фиг.57 представлены внешние и внутренние интерфейсы.

Указанные преимущества заявляемой ПВС перед прототипом достигаются за счет того, что в ПВС, содержащую первый 1, второй 2, третий 3 и четвертый 4 микропроцессоры, ОЗУ 5, ПЗУ 6, первая 7 и вторая 8 группы входов ПВС соединены с первой группой входов системного контроллера 17 и первыми группами входов первого 1, второго, 2, третьего 3 и четвертого 4 процессоров, дополнительно введены второе 9, третье 10 и четвертое 11 ПЗУ, второе 12, третье 13 и четвертое 14, пятое 15 и шестое 16 ОЗУ, системный контроллер 17, первый 18, второй 19, третий 20 и четвертый 21 приемопередатчики LVDS, первый 22, второй 23, третий 24 и четвертый 25 приемопередатчики Fibre channal TLK 1201, контроллер 26 LINK Fibre channal, генератор 27 на 106,25 МГц, генератор 28 на 10 МГц, генератор 29 на 40 МГц, узел сброса по питанию 30, контроллер 31 LINK МКО, первый 32 и второй 33 приемо-передатчики МКО HI-1574, первый 34 LINK коммутатор, второй 35 LINK коммутатор, первые группы входов 36 и выходов 37 которого соединены с первыми группами входов и выходов первого 34 LINK коммутатора, вторые группы входов 38 и выходов 39 которого соединены со второй группой входов и первой группой выходов первого 1 микропроцессора, третья группа входов и вторая группа выходов которого соединены с третьими группами входов 40 и выходов 41 первого 34 LINK коммутатора, четвертые группы входов 42 и выходов 43 которого соединены со второй группой входов и первой группой выходов второго 2 микропроцессора, третья группа входов и вторая группа выходов которого соединены с пятыми группами входов 44 и выходов 45 первого 34 LINK коммутатора, шестые группы входов 46 и выходов 47 которого соединены со второй группой входов и первой группой выходов третьего 3 микропроцессора, третья группа входов и вторая группа выходов которого соединены с седьмыми группами входов 48 и выходов 49 первого 34 LINK коммутатора, восьмые группы входов 50 и выходов 51 которого соединены со второй группой входов и первой группой выходов четвертого 4 микропроцессора, третья группа входов и вторая группа выходов которого соединены с девятыми группами входов 52 и выходов 53 первого 34 LINK коммутатора, десятые группы входов 55 и выходов 54 которого являются третьей группой входов и первой группой выходов ПВС, четвертая группа входов и вторая группа выходов которой соединены с одиннадцатыми группами входов 57 и выходов 56 первого 34 LINK коммутатора, двенадцатые группы входов 58 и выходов 59 которого соединены со вторыми группами входов и выходов второго 35 LINK коммутатора, третьи группы входов и выходов которого соединены с первыми 60 группами входов и выходов 61 контроллера LINK Fibre channal, вторые группы входов и выходов которого соединены с четвертыми группами входов 62 и выходов 63 второго 35 LINK коммутатора, пятые группы входов 64 и выходов 65 которого соединены с первыми группами входов и выходов контроллера LINK МКО 31, первая 66 группа входов-выходов которого соединена с группами входов-выходов пятого 15 и шестого 16 ОЗУ, причем группы входов-выходов 67, 68, 69, 70 первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров соединены с группами входов-выходов первых 5, 6, вторых 12, 9, третьих 13, 10 и четвертых 14, 11 ОЗУ и ПЗУ соответсвенно, причем четвертые группы входов 71 и третьи группы выходов 72 первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров соединены с первыми группами входов и выходов первого 18, второго 19, третьего 20 и четвертого 21 приемопередатчиков LVDS, вторые группы входов и выходов которых соединены со вторыми 73, третьими 74, четвертыми 75 и пятыми 76 группами входов и с первыми 77, вторыми 78, третьими 79 и четвертыми 80 группами выходов системного контроллера 17, пятая 81, шестая 82, седьмая 83 и восьмая 84 группы выходов которого соединены с пятыми группами входов первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров, четвертые группы выходов которых соединены с шестой 85, седьмой 86, восьмой 87 и девятой 88 группами входов системного контроллера 17, девятая 89 группа выходов которого является первой группой выходов ПВС, вторая 90 группа выходов которой соединена с первыми выходами первого 1, второго, 2 третьего 3 и четвертого 4 микропроцессоров, первые входы которых соединены с первым входом системного контроллера 17 и с выходом 91 генератора 28 на 10 МГц, причем генератор 27 на 106.25 МГц соединен с первым 92 входом контроллера LINK Fibre channal 26, третья 93 группа выходов которого соединена с первыми группами входов первого 22 и второго 23 приемопередатчиков Fibre channal TLK 1201, a четвертая 94 группа выходов соединена с первыми группами входов третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201, первые группы выходов первого 22, второго 23, третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201 соединены с первой 95, второй 96, третьей 97 и четвертой 98 группами входов контроллера LINK Fibre channal 26, пятые 99, шестые 100, седьмые 101 и восьмые 102 управляющие группы входов и выходов которого соединены со вторыми группами входов и выходов первого 22, второго 23, третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201, вторые группы выходов которых являются третьей 103, четвертой 104, пятой 105 и шестой 106 группами выходов ЛВС, третья 107, четвертая 108, пятая 109 и шестая 110 группы входов которой соединены с третьими группами входов первого 22, второго 23, третьего 24 и четвертого 25 приемопередатчиков Fibre channal TLK 1201, причем первый 111 вход ПВС соединен со вторым входом системного контроллера 17, первая 112 и вторая 113 группы входов-выходов ПВС соединены с группами входов-выходов первого 32 и второго 33 приемопередатчиков МКО HI-1574, группы выходов которых соединены со второй 114 и третьей 115 группами входов контроллера LINK МКО 31, вторая 116 и третья 117 группы выходов которого соединены с первыми группами входов первого 32 и второго 33 приемопередатчиков МКО HI-1574, вторые группы входов которых соединены с четвертой 118 и пятой 119 группами выходов контроллера LINK МКО 31, шестая 120 группа выходов которого соединена с десятой группой входов системного контроллера 17, первый 121 выход которого соединен со вторыми входами первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров, причем выход 122 узла сброса по питанию 30 соединен с третьим входом системного контроллера 17, десятая группа выходов которого является третьей 123 группой выходов ПВС, причем второй 124 выход системного контроллера 17 соединен с третьими входами первого 1, второго 2, третьего 3 и четвертого 4 микропроцессоров, с первыми входами первого 34 и второго 35 LINK коммутаторами и контроллером LINK МКО 31, вторым входом контроллера LINK Fibre channal 26, первый 125 выход которого соединен с четвертым входом системного контроллера 17, причем выход 126 генератора 29 на 40 МГц соединен со вторым входом контроллера LINK МКО 31, а вход 127 узла сброса по питанию 30 соединен с питанием 3.3V.

Системный контроллер 17 содержит первый 128, второй 129, третий 130, четвертый 131 блоки Space Wire, коммутатор 132, узел формирования зап/чт в регистры коммуникационных систем на основе LINK-интерфейсов (далее по тексту узел RCP_2) 133, таймер синхронизации и узел формирования прерываний (ТСУФП) 134, узел формирования сигналов инициализации и тактовых сигналов (УФСИТС) 135, узел приема и фиксации сигналов инициализации (УПФСИ) 136, узел формирования сигнала программной инициализации (УФСПИ) 137, первая 138 группа выходов которого соединена с первыми группами выходов УПФСИ 136 и ТСУФП 134 и первой группой входов узла 133 RCP_2, первая 139 группа выходов которого соединена с первыми группами входов УПФСИ 136, УФСПИ 137 и ТСУФП 134, вторая группа входов которого соединена со вторыми группами входов УПФСИ 136 и УФСПИ 137 и второй 140 группой выходов узла 133 RCP_2, третья 141 группа выходов которого соединена с третьими группами входов УПФСИ 136, УФСПИ 137, ТСУФП 134 и первой группой входов коммутатора 132, первая 142, вторая 143, третья 144 и четвертая 145 группы выходов которого соединены с первыми группами входов первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, первые группы выходов которых соединены со второй 146, третьей 147, четвертой 148 и пятой 149 группами входов коммутатора 132, шестая 150, седьмая 151, восьмая 152 и девятая 153 группы входов которого соединены со вторыми группами выходов первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, первый и второй выходы которых являются первой 77, второй 78, третьей 79 и четвертой 80 группами выходов системного контроллера 17 соответственно, вторая 73, третья 74, четвертая 75 и пятая 76 группы входов которого являются первым и вторым входами первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, вторые группы входов которых соединены с четвертой 154 группой выходов узла 133 RCP_2, пятая 155 группа выходов которого соединена с десятой группой входов коммутатора 132 и с третьими входами первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, четвертые входы которых соединены между собой, с первыми входами коммутатора 132, УПФСИ 136, УФСПИ 137, ТСУФП 134, узла 133 RCP_2 и первым 156 выходом УФСИТС 135, второй 157 выход которого соединен с пятыми входами первого 128, второго 129, третьего 130 и четвертого 131 блоков Space Wire, шестые входы которых соединены между собой и со вторыми входами ТСУФП 134 и узла 133 RCP_2, с третьим 124 выходом УФСИТС 135 и является первым выходом системного контроллера 17, второй 121 выход которого соединен с четвертым выходом УФСИТС 135, пятый 158 выход которого соединен с третьим входом ТСУФП 134, вторая 159 группа выходов которого соединена со второй группой входов узла 135 RCP_2, третья группа входов которого соединена с пятой 160 группой выходов коммутатора 132, первый 161, второй 162 и третий 163 выходы которого соединены с третьим, четвертым и пятым входами узла 133 RCP_2, первый 164 выход которого соединен с четвертым входом ТСУФП 134, первый 165 выход которого соединен с первым входом УФСИТС 135, первая 166 группа выходов которого соединена с четвертой группой входов УПФСИ 136, причем шестой вход ТСУФП 134 соединен с первым 167 выходом УФСПИ 137, второй 168 выход которого соединен со вторым входом УФСИТС 135, шестой 169 выход которого соединен со вторым входом УФСПИ 137, причем третий, четвертый и пятый входы УФСИТС 135 являются первым 91, третьим 122 и вторым 111 входами системного контроллера 17, пятая 81, шестая 82, седьмая 83, восьмая 84 группы выходов которого соединены с третьей, четвертой, пятой и шестой группами выходов ТСУФП 134, седьмая и восьмая группы выходов которого соединены с девятой 89 и десятой 123 группами выходов системного контроллера 17, четвертая, пятая, шестая, седьмая и восьмая группы входов которого соединены с первой 7, шестой 85, седьмой 86, восьмой 87 и девятой 88 группами входов системного контроллера 17 соответственно, десятая 120 группа входов которого соединена с девятой группой входов ТСУФП 134, пятый вход которого является и четвертым 125 входом системного контроллера 17, причем вторая 170 группа выходов УФСИТС 135 соединена с четвертой группой входов УФСПИ 137.

Таймер синхронизации и узел формирования прерываний (ТСУФП) 134 содержат первый 171, второй 172, третий 173 и четвертый 174 узлы приема, фиксации и выдачи сигналов прерываний (УПФВСП), таймер синхронизации (ТС) 175, узел формирования задержанного сигнала реинициализации (УФЗСР) 176, регистр управления таймером синхронизации (RCR) 177, узел формирования разрешения обмена данными (УФРОД) 178, группа выходов которого является второй 159 группой выходов ТСУФП 134, первая 138 группа выходов которого соединена с первыми группами выходов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, УФЗСР 176, RCR 177 и ТС 175, первая 314 группа входов которого соединена со второй группой выходов RCR 177, третья группа выходов которого соединена с первыми группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, вторые группы входов которых соединены между собой, с первыми группами входов УФЗСР 176, RCR 177 и второй группой входов ТС 175 и являются первой 139 группой входов ТСУФП 134, вторая 140 группа входов которого соединена с первой группой входов УФРОД, со вторыми группами входов УФЗСР 176, RCR 177, третьей группой входов ТС 175 и с третьими группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, четвертые группы входов которых соединены между собой, со второй группой входов УФРОД, с третьими группами входов УФЗСР 176, RCR 177, с четвертой группой входов ТС 175 и являются третьей 141 группой входов ТСУФП 134, третья 81, четвертая 82, пятая 83 и шестая 84 группы выходов которого соединены со вторыми группами выходов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, первые входы которых соединены между собой и с первыми входами УФЗСР 176, RCR 177, УФРОД 178, ТС 175 и являются первым 156 входом ТСУФП 134, второй 124 вход которого соединен со вторыми входами УФЗСР 176, RCR 177, УФРОД 178, ТС 175 и первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, пятые группы входов которых являются пятой 85, шестой 86, седьмой 87 и восьмой 88 группами входов ТСУФП 134, девятая 120 группа входов которого соединена с шестыми группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП, третьи входы которых соединены с пятым 125 входом ТСУФП 134, третий 158 вход которого соединен с третьим входом ТС 175, причем четвертый 164 вход ТСУФП 134 соединен с третьими входами УФРОД 178 и УФЗСР 176, первый выход которого является первым 165 выходом ТСУФП 134, седьмая 89 и восьмая 123 группы выходов которого соединены со второй группой выходов УФЗСР 176 и с четвертой группой выходов RCR 177, причем четвертая 7 группа входов ТСУФП 134 соединена с седьмыми группами входов первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП и с четвертым входом ТС 175, четвертая группа входов УФЗСР 176 соединена с первыми сигналами пятой 85, шестой 86, седьмой 87 и восьмой 88 группами входов ТСУФП 134, причем первый выход ТС соединен с четвертыми входами первого 171, второго 172, третьего 173 и четвертого 174 УПФВСП.

Блок SW (128, 129, 130, 131) содержит узел SW_LPORT 179, узел LPORT_OY 180, узел SW (YSW) 181, узел LPORT_SW 182, элемент ИЛИ 183, FIFO 184, первая группа выходов которого является первой 146 группой выходов блока SW 128, вторая 150 группа выходов которого соединена с первыми выходами узла LPORT_SW 182, узла LPORT_OY 180 и FIFO 184, первый выход которой соединен с первым входом узла LPORT_OY 180, первая группа входов которого соединена с первой группой входов FIFO 184 и с первой 185 группой выходов узла SW_LPORT 179, первый вход которого соединен с первыми входами YSW 181, узла LPORT_ SW 182, FIFO 184, со вторым входом узла LPORT_OY 180 и является пятым 157 входом блока SW 128, первый 186 и второй 187 входы которого соединены со вторым и третьим входами YSW 181, первый и второй выходы которого являются первым 188 и вторым 189 выходами блока SW 128, первая 142 группа входов которого соединена со вторыми входами FIFO 184 и узла LPORT_SW 182, группа выходов 190 которого соединена с первой группой входов YSW 181, третий 191 выход которого соединен с третьим входом узла LPORT_ SW 182, второй 192 выход которого соединен с четвертым входом YSW 181, пятый 193 и шестой 194 входы которого соединены с первым и вторым выходами узла SW_LPORT 179, второй вход которого соединен с третьими входами узла LPORT_OY 180 и FIFO 184, с четвертым и седьмым входами узла LPORT_SW 182 и YSW 181 и является шестым 124 входом блока SW 128, четвертый 156 вход которого соединен с восьмым входом YSW 181, четвертый 195 выход которого соединен с третьим входом узла SW_LPORT 179, четвертый вход которого соединен с выходом 196 элемента ИЛИ 183, первый и второй входы которого соединены со вторыми 197,198 выходами FIFO 184 и узла LPORT_OY 180, третий 199 выход которого соединен с четвертым входом FIFO 184, причем третий 155 вход блока SW 128 соединен с пятым входом узла LPORT_SW 182, группа выходов 200 YSW 181 соединена с группой входов узла SW_LPORT 179, вторая VWORD группа выходов которого соединена со вторыми группами входов LPORT_OY 180 и FIFO 184, вторая 154 группа входов блока SW 128 соединена с группой входов LPORT_SW 182.

Узел SW 181 содержит приемник 201, машину состояний (МС) 202, передатчик 203, первый, второй и третий выходы которого являются первым 188, вторым 189 и третьим 191 выходами узла SW 181, четвертый 195 выход которого соединен с первым входом передатчика 203 и первым выходом приемника 201, второй, третий, четвертый, пятый, шестой, седьмой, восьмой выходы которого соединены с первым, вторым, третьим, четвертым, пятым, шестым, седьмым входами МС 202, первый выход которой соединен с первым входом приемника 201, первая и вторая группы выходов которого соединены с первой и второй группами входов передатчика 203, второй вход которого соединен с восьмым входом МС 202 и с первым 157 входом узла SW 181, второй 186 и третий 187 входы которого соединены со вторым и третьим входами приемника 201, четвертый, пятый и шестой входы которого соединены с восьмым 156, шестым 194, четвертым 192 входами узла SW 181 соответственно, пятый 193 вход которого соединен с девятым входом МС 202, десятый вход которого соединен с третьим входом передатчика 203, седьмым входом приемника 201 и является седьмым 124 входом узла SW 181, причем четвертый вход передатчика 203 соединен с одиннадцатым входом МС 202, с питанием 3.3v и с двенадцатым входом МС 202, второй, третий, четвертый, пятый, шестой и седьмой выходы которой соединены с пятым, шестым, седьмым, восьмым, девятым и десятым входами передатчика 203, одиннадцатый вход которого соединен с пятым выходом приемника 201, девятый выход которого соединен с двенадцатым входом передатчика 203, причем тринадцатый вход МС 202 соединен с корпусом, а восьмой выход МС 202 с восьмым входом приемника 201, причем первая 200 группа выходов и первая 190 группа входов узла SW 181 соединены с третьей группой выходов приемника 201 и с третьей группой входов передатчика 203.

Узел LPORT_OY 180 содержит сумматор 204, инвертор 205, МС 206 и узел контроля полей заголовка 207, группа выходов которого соединена с первой группой входов МС 206, группа выходов которой соединена с первой группой входов узла контроля полей заголовка 207, первый, второй и третий выходы которого соединены с первым, вторым и третьим входами МС 206, первый, второй и третий выходы которой являются третьим сигналом второй группы выходов 150, первым 198 и вторым 199 выходами узла LPORT_OY 180 соответственно, первая 185 группа входов которого соединена с первой группой входов сумматора 204 и второй группой входов узла контроля полей заголовка 207, четвертый выход которого соединен с четвертым входом МС 206 и входом инвертора 205, выход которого соединен с пятым входом МС 206, четвертый выход которой соединен с первым входом сумматора 204, группа выходов которого соединена со второй группой входов МС 206 и третьей группой входов узла контроля полей заголовка 207, первый вход которого соединен со вторым входом сумматора 204, шестым входом МС 206 и является вторым 157 входом узла LPORT_OY 180, вторая VWORD группа входов которого соединена со второй группой входов сумматора 204 и третьей группой входов МС 206, седьмой вход которой является вторым сигналом второй группы выходов 150 узла LPORT_OY 180, третий 124 вход которого соединен со вторым входом узла контроля полей заголовка 207, с третьим входом сумматора 204 и с восьмым входом МС 206, девятый вход которой соединен с выходом сумматора 204, причем десятый вход МС 206 соединен с питанием +3.3v, а одиннадцатый вход соединен с «корпусом».

Узел SW_LPORT 179 содержит сдвиговый регистр 208, первый 209, второй 210 и третий 211 регистры, МС 212 и константу 213, группа выходов которой соединена с группой входов сдвигового регистра 208, группа выходов которого соединена с группой входов МС 212 и является второй 201 группой выходов узла SW_LPORT 179, первая 185 группа выходов которого соединена с группой выходов третьего 211 регистра, группа входов которого соединена с группой выходов второго 210 регистра, группа входов которого соединена с группой выходов первого 209 регистра, группа входов которого является группой входов 200 узла SW_LPORT 179, а восьмой разряд соединен с первым входом МС 212, первый и второй выходы которой являются первым 193 и вторым 194 выходами узла SW_LPORT 179, первый 157 вход которого соединен с тактовыми входами сдвигового регистр 208, первого 209, второго 210 и третьего 211 регистров, сбросовые входы которых соединены между собой и являются вторым 124 входом узла SW_LPORT 179, третий 195 и четвертый 196 входы которого соединены со вторым и третьим входами МС 212, третий, четвертый и пятый выходы которой соединены с разрешающими входами третьего 211 регистра, первого 209 регистра и второго 210 регистра соответственно.

Узел LPORT_SW 182 содержит счетчик 214, первый 215 и второй 216 регистры, первый 217 и второй 218 мультиплексоры, МС 219 и константу 220, группа выходов которой соединена с первой группой входов второго 218 мультиплексора, группа выходов которого соединена с информационной группой входов второго 216 регистра, группа выходов которого является группой выходов 190 узла LPORT_SW 182, первый сигнал второй группы выходов 150 и второй 192 выход которого соединены с первым и вторым выходами МС 219, третий выход которой соединен со входом второго 218 мультиплексора и с разрешающим входом второго 216 регистра, тактовый вход которого соединен с тактовыми входами счетчика 214 и первого 215 регистра, с первым входом МС 219 и является первым 157 входом узла LPORT_SW 182, второй сигнал первой группы входов 142, третий 19d и пятый 155 (первый сигнал) входы которого соединены со вторым, третьим и четвертым входами МС 219, четвертый выход которой соединен с прямым и инверсным входами первого 217 мультиплексора, первая и вторая группы выходов которого соединены с информационными входами первого 215 регистра, сбросовый вход которого соединен со сбросовыми входами счетчика 214 и второго 216 регистра, с пятым входом МС 219 и является четвертым 124 входом узла LPORT_SW 182, группа входов 154 которого соединена с первой и второй группами входов первого 217 мультиплексора, третья группа входов которого соединена с первой и второй группами выходов первого 215 регистра и второй группой входов второго 218 мультиплексора, причем группа выходов счетчика 214 соединена с группой входов МС 219, пятый выход которой соединен с разрешающим входом счетчика 214.

Узел формирования сигнала программной инициализации (УФСПИ) 137 содержит первый 221, второй 222 и третий 223 регистры, первый 224 и второй 225 узлы REG_COUNT, элемент ИЛИ 226, блок констант 227, схему сравнения 228, первый 229, второй 230 и третий 231 элемент И, триггер 232, выход которого соединен с первым входом третьего 231 элемента И, выход которого соединен с первым входом первого 224 узла REG_COUNT, выход которого соединен с инверсным входом первого 229 элемента И и является первым 167 выходом УФСПИ 137, второй 168 выход которого соединен с выходом первого 229 элемента И, прямой вход которого соединен с выходом элемента ИЛИ 226, группа входов которого соединена с первой группой выходов второго 222 регистра, вторая группа выходов которого соединена с первой и второй группами выходов первого 221 регистра, с первой группой входов схемы сравнения 228, с группами выходов третьего 223 регистра, первого 224 и второго 225 узла REG_COUNT и является первой 138 группой выходов УФСПИ 137, первая 139 группа входов которого соединена с информационными группами входов первого 221, второго 222 и третьего 223 регистров, первые группы входов которых соединены с первыми группами входов первого 224 и второго 225 узлов REG_COUNT и являются третьей 141 группой входов УФСПИ 137, вторая 140 группа входов которого соединена с разрешающими входами первого 221, второго 222 и третьего 223 регистров и со вторым входом первого 224 узла REG_COUNT и первым входом второго 225 узла REG_COUNT, второй вход которого соединен с третим входом первого 224 узла REG_COUNT и с тактовыми входами первого 221, второго 222, третьего 223 регистров и триггера 232 и является первым 156 входом УФСПИ 137, первый сигнал четвертой 170 группы входов соединен со сбросовыми входами первого 221, третьего 223 регистров и триггера 232, с четвертым входом первого 224 узла REG_COUNT и третьим входом второго 225 узла REG_COUNT, второй сигнал четвертой 170 группы входов соединен со сбросовым входом второго 222 регистра, причем выход второго 225 узла REG_COUNT соединен с прямым входом второго 230 элемента И, инверсный вход которого соединен с четвертым входом второго 225 узла REG_COUNT и инверсным выходом схемы сравнения 228, вторая группа входов которой соединена с первой группой выходов блока констант 227, вторая группа выходов которого соединена со вторыми группами входов первого 224 и второго 225 узлов REG_COUNT, пятые входы которых соединены со вторым 169 входом УФСПИ 137, причем выход второго 230 элемента И соединен с информационным входом триггера 232 и вторым входом третьего 231 элемента И.

Узел с управляемым разрешением счета (REG_COUNT)(224, 225) содержит счетчик 233, дешифратор 234, элемент И 235 и триггер 236, выход которого является выходом 167 узла REG_COUNT 224, группа выходов 138 которого соединена с первой группой выходов счетчика 233, вторая группа выходов которого соединена с группой входов дешифратора 234, выход которого соединен с первым входом элемента И 235 и информационным входом триггера 236, тактовый вход которого соединен с тактовым входом счетчика 233 и является первым 156 входом узла REG_COUNT 224, пятый 169 вход которого соединен со вторым входом элемента И 235, выход которого соединен с разрешающим входом счетчика 233, информационная группа входов которого является второй 227 группой входов узла REG_COUNT 224, первая 141 группа входов которого соединена с группой входов счетчика 233, сбросовый вход которого соединен с установочным входом триггера 236 и является первым сигналом четвертой 170 группы входов узла REG_COUNT 224, второй 140 вход которого соединен с третьим входом элемента И 235.

Узел формирования сигналов инициализации и тактовых сигналов (УФСИТС) 135 содержит первый 238 счетчик, второй 239 счетчик, третий 240 счетчик, четвертый 241 счетчик, PLL 242, первый 243 элемент ИЛИ, второй 244 элемент ИЛИ, третий 245 элемент ИЛИ, первый 246 триггер, второй 247 триггер, первый 248 дешифратор, второй 249 дешифратор, инвертор 250, выход которого является первым сигналом первой 166 группы выходов УФСИТС 135, второй сигнал которой соединен с инверсным выходом первого 246 триггера, прямой выход которого соединен с первым входом второго 244 элемента ИЛИ и сбросовым входом четвертого 241 счетчика, выход которого является четвертым 121 выходом УФСИТС 135, третий сигнал первой 166 группы выходов которого соединен со вторым входом второго 244 элемента ИЛИ и является пятым 111 входом УФСИТС 135, четвертый сигнал первой 166 группы выходов которого соединен с первым входом третьего 245 элемента ИЛИ и является вторым 165 входом УФСИТС 135, первый сигнал второй 170 группы выходов которого соединен с выходом третьего 245 элемента ИЛИ и является третьим 124 выходом УФСИТС 135, второй сигнал второй 170 группы выходов которого соединен с выходом второго 247 триггера, со вторым входом третьего 245 элемента ИЛИ, сбросовым входом