Схема возбуждения дисплея, дисплейная панель и устройство отображения

Иллюстрации

Показать всеИзобретение относится к схеме возбуждения дисплея, посредством которого сигнальные линии одновременно выбирают в заданный момент времени. Техническим результатом является обеспечение стабильной работы сдвигового регистра после окончания одновременного выбора множества сигнальных линий, выполняемого схемой возбуждения дисплея в заданные моменты времени. Устройство содержит сдвиговый регистр, при этом: разряд сдвигового регистра включает в себя асинхронный RS триггер, выполненный с возможностью приема сигнала инициализации, и схему генерации сигнала, выполненную с возможностью приема сигнала одновременного выбора, причем схема генерации сигнала выполнена с возможностью генерировать выходной сигнал разряда с помощью выходного сигнала триггера; выходной сигнал разряда становится активным под действием сигнала одновременного выбора и затем сохраняется активным в течение одновременного выбора; выходной сигнал триггера неактивен, когда сигнал инициализации является активным, независимо от того, является ли каждый сигнал из сигнала установки и сигнала сброса активным или неактивным; и сигнал инициализации становится активным до окончания одновременного выбора и становится неактивным после окончания одновременного выбора. 3 н. и 21 з.п. ф-лы, 43 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к схеме возбуждения дисплея (различные виды возбудителей дисплея), посредством которого сигнальные линии одновременно выбирают в заданный момент времени.

Уровень техники

Патентная литература 1 (см. фиг.38) раскрывает драйвер затвора, используемый в жидкокристаллическом дисплейном устройстве, причем драйвер затвора включает в себя сдвиговый регистр, имеющий множество разрядов. Каждый разряд из множества разрядов имеет (i) асинхронный RS триггер, включающий в себя вход инициализации (INI), и (ii) схему логического элемента, включающую в себя аналоговый переключатель 43 и транзистор 44 с каналом n-типа. Более того, тактовый сигнал СК поступает на аналоговый переключатель 43, исток транзистора 44 соединен с VSS, а выходной сигнал On каждого разряда поступает на соответствующую сигнальную линию развертки. В данной конфигурации, когда электропитание жидкокристаллического устройства отображения включено, выходные сигналы (On-1, On, On+1 и т.п.) всех разрядов последовательно активизируют после каждой задержки, вызывая активизацию стартового импульса ST, тогда как тактовый сигнал СК устанавливают в активный (см. фиг.39). Это делает возможным одновременный выбор всех сигнальных линий развертки, так что Vcom (общий электродный электрический потенциал) записывают на все пиксели.

Список литературы

Патентная литература 1

Международная публикация № WO 2007/108177 (дата публикации: 27 сентября 2007 года)

Раскрытие изобретения

Техническая задача

В стандартной конфигурации, однако, существует проблема, что работа сдвигового регистра становится нестабильной, так как выходной сигнал триггера не определен в течение интервала времени после того, как выходной сигнал каждого разряда становится неактивным, когда тактовый сигнал СК становится неактивным (Низким) (то есть, после окончания одновременного выбора), и до тех пор, пока INI сигнал (сигнал инициализации) не становится активным (Высоким) (см. фиг.39). Причина состоит в том, что когда выходной сигнал каждого разряда становится неактивным и тем самым SB-сигнал и R-сигнал, которые подают на каждый разряд, возвращаются в неактивное состояние, выход триггера изменяется в зависимости от соотношения между моментом времени, в который SB-сигнал возвращают в неактивное состояние, и моментом времени, в который R-сигнал возвращают в неактивное состояние. Например, в случае, когда и SB-сигнал, и R-сигнал смещают следующим образом: "активный → неактивный", триггер сохраняет выход Q Высоким (см. фиг.40); в случае, если SB-сигнал смещают следующим образом: "активный → неактивный → неактивный", а R-сигнал смещают следующим образом: "активный → активный → неактивный", триггер сбрасывается и таким образом выход Q становится Низким (см. фиг.41); а в случае, когда SB-сигнал смещают следующим образом: "активный → активный → неактивный", а R-сигнал смещают следующим образом: "активный → неактивный → неактивный", триггер устанавливается на нуль, так что выход Q становится Высоким (см. фиг.42).

Задачей настоящего изобретения является стабилизировать работу сдвигового регистра после того, как одновременный выбор множества сигнальных линий выполнен схемой возбуждения дисплея в заданный момент времени.

Решение задачи

Схема возбуждения дисплея настоящего изобретения включает в себя сдвиговый регистр, при этом схема возбуждения дисплея выполняет одновременный выбор множества сигнальных линий в заданный момент времени, при этом: разряд сдвигового регистра включает в себя (i) асинхронный RS триггер, принимающий сигнал инициализации, и (ii) схему генерации сигнала, принимающую сигнал одновременного выбора, при этом схема генерации сигнала генерирует выходной сигнал разряда с помощью выходного сигнала триггера; выходной сигнал разряда (i) становится активным вследствие активизации сигнала одновременного выбора и затем (ii) остается активным во время одновременного выбора; выход триггера является неактивным, а сигнал инициализации является активным, независимо от того, является ли каждый из сигнала установки и сигнала сброса активным или неактивным; при этом сигнал инициализации становится активным до окончания сигнала одновременного выбора и становится неактивным после окончания одновременного выбора.

По данной конфигурации, инициирование сдвигового регистра (т.е., инициирование триггера в каждом разряде) завершено, когда завершен одновременный выбор, и сигнал установки и сигнал сброса становятся неактивными. Это позволяет стабилизировать работу сдвигового регистра после одновременного выбора по сравнению со стандартной схемой возбуждения (см. фиг.38 и 39), в котором триггер не определен после окончания одновременного выбора, до тех пор, пока INI сигнал не подан на триггер.

Полезные результаты изобретения

Настоящее изобретение позволяет стабилизировать работу сдвигового регистра после выполнения одновременного выбора множества сигнальных линий схемой возбуждения дисплея в заданный момент времени.

Краткое описание чертежей

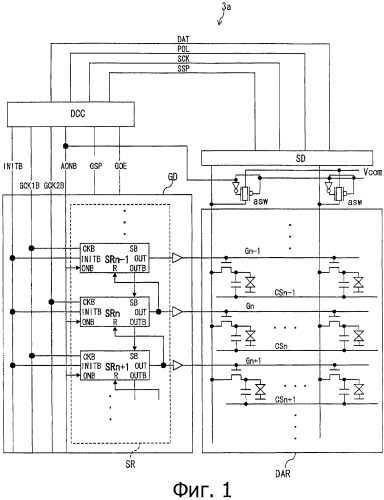

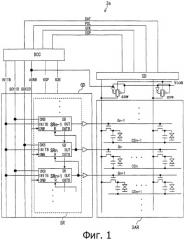

Фиг.1 представляет собой схематичный вид, иллюстрирующий конфигурацию жидкокристаллического дисплейного устройства Варианта осуществления 1 настоящего изобретения.

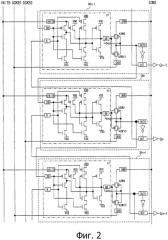

Фиг.2 представляет собой электрическую схему, частично иллюстрирующую сдвиговый регистр жидкокристаллического дисплейного устройства, показанного на фиг.1.

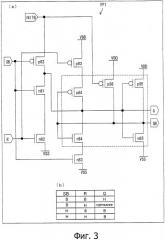

Фиг.3(а) представляет собой электрическую схему триггера сдвигового регистра, показанного на фиг.2, а (b) представляет собой таблицу истинности триггера.

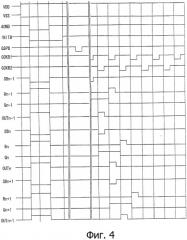

Фиг.4 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.1 (когда электропитание включено).

Фиг.5 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.1 (в случае, когда SB-сигнал и R-сигнал возвращаются одновременно).

Фиг.6 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.1 (в случае, когда SB-сигнал возвращается до возвращения R-сигнала).

Фиг.7 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.1 (в случае, когда SB-сигнал возвращается после возвращения R-сигнала).

Фиг.8 представляет собой схематичный вид, иллюстрирующий другую конфигурацию жидкокристаллического дисплейного устройства Варианта осуществления 1 настоящего изобретения.

Фиг.9 представляет собой схематичный вид, иллюстрирующий еще одну конфигурацию жидкокристаллического дисплейного устройства Варианта осуществления 1 настоящего изобретения.

Фиг.10 представляет собой электрическую схему, частично иллюстрирующую сдвиговый регистр жидкокристаллического дисплейного устройства, показанного на фиг.9.

Фиг.11(а) представляет собой электрическую схему триггера сдвигового регистра, показанного на фиг.10, (b) представляет собой временную диаграмму работы триггера, а (с) представляет собой таблицу истинности триггера.

Фиг.12 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.9 (когда электропитание включено).

Фиг.13 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.9 (в случае, если SB-сигнал и R-сигнал возвращаются одновременно).

Фиг.14 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.9 (в случае, если SB-сигнал возвращается до возвращения R-сигнала).

Фиг.15 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.9 (в случае, если SB-сигнал возвращается после возвращения R-сигнала).

Фиг.16(а) представляет собой вид, иллюстрирующий процесс генерации сигнала инициализации, а (b) представляет собой временную диаграмму, иллюстрирующую процесс генерации.

Фиг.17(а) представляет собой вид, иллюстрирующий другой процесс генерации сигнала инициализации, а (b) представляет собой временную диаграмму, иллюстрирующую процесс генерации.

Фиг.18 представляет собой схематичный вид, иллюстрирующий еще одну конфигурацию жидкокристаллического дисплейного устройства Варианта осуществления 2 настоящего изобретения.

Фиг.19 представляет собой электрическую схему, частично иллюстрирующую сдвиговый регистр жидкокристаллического дисплейного устройства, показанного на фиг.18.

Фиг.20 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.18 (когда электропитание включено).

Фиг.21 (а) представляет собой электрическую схему триггера сдвигового регистра, показанного на фиг.18, (b) представляет собой временную диаграмму работы триггера, а (с) представляет собой таблицу истинности триггера.

Фиг.22 представляет собой электрическую схему триггера сдвигового регистра, показанного на фиг.18.

Фиг.23 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.18 (в случае, если SB-сигнал возвращается после возвращения R-сигнала).

Фиг.24(а) представляет собой электрическую схему триггера сдвигового регистра, показанного на фиг.18, (b) представляет собой временную диаграмму работы триггера, а (с) представляет собой таблицу истинности триггера.

Фиг.25 представляет собой электрическую схему, иллюстрирующую точную конфигурацию микросхемы NAND, показанной на фиг.19.

Фиг.26 представляет собой схематичный вид, иллюстрирующий конфигурацию жидкокристаллического дисплейного устройства Варианта осуществления 3 настоящего изобретения.

Фиг.27 представляет собой схематичный вид, иллюстрирующий каждый разряд сдвигового регистра жидкокристаллического дисплейного устройства, показанного на фиг.26.

Фиг.28 представляет собой электрическую схему, иллюстрирующую триггерную запирающую D-схему драйвера G-CS жидкокристаллического дисплейного устройства, показанного на фиг.26.

Фиг.29 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.26.

Фиг.30 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.26.

Фиг.31 представляет собой схематичный вид, иллюстрирующий конфигурацию жидкокристаллического дисплейного устройства Варианта осуществления 4 настоящего изобретения.

Фиг.32 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.31.

Фиг.33 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством, показанным на фиг.31.

Фиг.34 представляет собой электрическую схему, иллюстрирующую пример конфигурации каждого разряда сдвигового регистра.

Фиг.35 представляет собой временную диаграмму, иллюстрирующую измененный пример конфигурации, показанной на фиг.20.

Фиг.36 представляет собой временную диаграмму, иллюстрирующую другой измененный пример конфигурации, показанной на фиг.20.

Фиг.37 представляет собой временную диаграмму, иллюстрирующую другой измененный пример конфигурации, показанной на фиг.20.

Фиг.38 представляет собой электрическую схему, иллюстрирующую конфигурацию стандартного сдвигового регистра.

Фиг.39 представляет собой временную диаграмму, иллюстрирующую управление стандартным сдвиговым регистром.

Фиг.40 представляет собой временную диаграмму, иллюстрирующую управление стандартным сдвиговым регистром (в случае, если SB-сигнал и R-сигнал возвращаются одновременно).

Фиг.41 представляет собой временную диаграмму, иллюстрирующую управление стандартным сдвиговым регистром (в случае, если SB-сигнал возвращается до возвращения R-сигнала).

Фиг.42 представляет собой временную диаграмму, иллюстрирующую управление стандартным сдвиговым регистром (в случае, если SB-сигнал возвращается после возвращения R-сигнала).

Фиг.43 представляет собой электрическую схему, иллюстрирующую конфигурацию стандартного драйвера затвора.

Осуществление изобретения

Нижеследующее описывает варианты осуществления настоящего изобретения со ссылкой на фиг.1-37. Отметим, что в следующих описаниях предполагают, что асинхронный RS триггер (ниже иногда сокращенно именуемый "FF") имеет (i) вход установки единицы (S-вход или SB-вход), на который подают сигнал установки единицы (S-сигнал или SB-сигнал), (ii) вход установки нуля (R-вход или RB-вход), на который подают сигнал установки нуля (R-сигнал или RB-сигнал), (iii) вход инициализации (INI-вход или INITB-вход), на который подают сигнал инициализации (INI-сигнал или INITB-сигнал), (iv) прямой выход (Q-выход), от которого поступает Q-сигнал, и (v) инверсный выход (QB-выход), от которого поступает QB-сигнал. Отметим, что электрический потенциал электропитания высокого напряжения (VDD) именуют "Vdd" (ниже, иногда именуют также "Высоким"), а электрический потенциал электропитания низкого напряжения (VSS) именуют "Vss" (ниже, иногда именуют также "Низким"). S-сигнал (сигнал установки единицы), R-сигнал (сигнал установки нуля) и O-сигнал (сигнал прямого выхода) становятся Высокими, когда каждый из этих сигналов находится в активном состоянии. SB-сигнал (сигнал установки единицы), RB-сигнал (сигнал установки нуля) и QB-сигнал (сигнал инверсного выхода) становятся Низкими, когда каждый из этих сигналов находится в активном состоянии.

Вариант осуществления 1

Фиг.1 представляет собой электрическую схему, иллюстрирующую конфигурацию жидкокристаллического дисплейного устройства 3а настоящего изобретения. Жидкокристаллическое дисплейное устройство 3а включает в себя рабочее поле экрана DAR, драйвер затвора GD, драйвер стока SD и микросхему дисплейного контроллера DCC. Схема возбуждения дисплея DCC подает на драйвер затвора GD INITB-сигнал (сигнал инициализации), AONB-сигнал (сигнал одновременного набора), стартовый импульс загрузки драйвера затвора GSP, сигнал разрешения работы драйвера затвора GOE и тактовые сигналы драйвера затвора GCKB1 и GCKB2. Более того, схема возбуждения дисплея DCC подает на драйвер стока SD стартовый импульс загрузки драйвера стока SSP, цифровые данные DAT, сигнал полярности POL и тактовый сигнал драйвера стока SCK. Драйвер затвора GD включает в себя сдвиговый регистр SR, имеющий множество разрядов. Ниже, i-ый разряд (i=1, … n-1, n, n+1, …) сдвигового регистра соответственно сокращенно именуют "i-ым разрядом SRi".

Выходной сигнал (OUT-сигнал) i-ого разряда SRi сдвигового регистра поступает на сигнальную линию развертки Gi рабочего поля экрана DAR через буфер. Например, OUT-сигнал n-ого разряда SRn поступает на сигнальную линию развертки Gn через буфер. В рабочем поле экрана DAR сигнальная линия развертки Gn соединена с затвором транзистора, который соединен с пиксельным электродом в пикселе PIXn. Конденсатор хранения (дополнительный конденсатор) образован пиксельным электродом в пикселе PIXn и линией конденсатора хранения CSn.

Кроме того, один (1) аналоговый переключатель и один (1) инвертер предусмотрены для каждой сигнальной линии передачи данных. Инвертер имеет вход, соединенный с линией AONB-сигнала. Один электрод проводимости аналогового переключателя asw соединен с концом сигнальной линии передачи данных, а другой электрод проводимости аналогового переключателя asw соединен с электропитанием Vcom (общий электродный электрический потенциал). Затвор с каналом n-типа аналогового переключателя asw соединен с выходом инвертера, а затвор с каналом p-типа аналогового переключателя asw соединен с линией передачи AONB-сигнала.

Фиг.2 представляет собой электрическую схему, частично иллюстрирующую точную конфигурацию сдвигового регистра SR. Как показано на фиг.2, каждый разряд сдвигового регистра включает в себя (i) асинхронный RS триггер FF, имеющий SB-вход, R-вход и INITB-вход, (ii) два аналоговых переключателя ASW9 и ASW10, (in) инвертер, (iv) СКВ выход, (v) ONB выход, (vi) OUTB выход и (vii) OUT выход. Q-выход триггера FF соединен с затвором с каналом p-типа аналогового переключателя ASW9 и затвором с каналом n-типа аналогового переключателя ASW10. QB-выход триггера FF соединен с затвором с каналом n-типа аналогового переключателя ASW9 и затвором с каналом p-типа аналогового переключателя ASW10. Один электрод проводимости аналогового переключателя ASW9 соединен с ONB выходом, а один электрод проводимости аналогового переключателя ASW10 соединен с СК выходом. Другой электрод проводимости аналогового переключателя ASW9, другой электрод проводимости аналогового переключателя ASW10 и OUTB выход, который служит выходом того разряда, соединены друг с другом. OUTB выход соединен с OUT выходом через инвертер.

В сдвиговом регистре SR каждый разряд имеет OUTB выход и R-вход, которые соединены соответственно с SB-входом и OUT выходом следующего разряда. Например, OUTB выход n-ого разряда SRn соединен с SB-входом (n+1)-ого разряда SRn+1, a OUT выход (n+1)-ого разряда SRn+1 соединен с R-входом n-ого разряда SRn. Отметим, что первый разряд SR1 сдвигового регистра SR имеет SB-вход, на который подают GSPB сигнал. В драйвере затвора GD INITB-входы триггеров соответствующих разрядов соединены с линией передачи INITB-сигнала, а ONB выходы соответствующих разрядов соединены с линией передачи AONB-сигнала. Более того, СКВ выход разряда с нечетным номером соединен с линией GCKB (через которую подают тактовый сигнал драйвера затвора GCKB), отличной от линии GCKB, с которой соединен СКВ выход разряда с четным номером. Например, СКВ выход n-ого разряда SRn соединен с линией передачи сигнала GCK2B, а СКВ выход (n+1)-ого разряда SRn+1 соединен с линией передачи сигнала GCK1B.

В качестве триггера FF, показанного на фиг.2, используется триггер FF1, показанный на фиг.3. Как показано на фиг.3, триггер FF1 включает в себя (i) транзистор с каналом p-типа р84 и транзистор с каналом n-типа n84, которые образуют микросхему CMOS, (ii) транзистор с каналом p-типа р85 и транзистор с каналом n-типа n85, которые образуют микросхему CMOS, (iii) транзисторы с каналом p-типа р82, р83 и р86, (iv) транзисторы с каналом n-типа n81, n82 и n83 и (v) SB-вход, R-вход, Q-выход и QB-выход. Затвор транзистора р84, затвор транзистора n84, сток транзистора р85, сток транзистора n85, сток транзистора р86 и QB-выход соединены друг с другом. Сток транзистора р84, сток транзистора n84, сток транзистора р82, сток транзистора n81, затвор транзистора р85, затвор транзистора n85 и Q-выход соединены друг с другом. Исток транзистора n84 соединен со стоком транзистора n83. Исток транзистора n84 соединен со стоком транзистора n83. Исток транзистора n81 соединен со стоком транзистора n82. INITB-вход соединен с истоком транзистора р82 и затвором транзистора р86. SB-вход соединен с затвором транзистора р82, затвором транзистора n81 и затвором транзистора n83. R-вход соединен с затвором транзистора n82 и затвором транзистора р83. Исток транзистора n85 соединен с VSS. Истоки транзисторов р82, р83, р85 и р86 соединены с VDD. Истоки транзисторов n82, n83 и n85 соединены с VSS.

(b) на фиг.3 представляет собой таблицу истинности триггера FF1. Q-сигнал триггера FF1 должен иметь состояние, как описано ниже (см. (b) на фиг.3): в течение интервала времени, в который SB-сигнал является Высоким (неактивным) и R-сигнал является Высоким (активным), Q-сигнал является Низким (неактивным); в течение интервала времени, в который SB-сигнал является Высоким (неактивным) и R-сигнал является Низким (неактивным), Q-сигнал находится в состоянии удержания; в течение интервала времени, в который SB-сигнал является Низким (активным) и R-сигнал является Высоким (активным), Q-сигнал является Высоким (активным); и в течение интервала времени, в который SB-сигнал является Низким (активным) и R-сигнал является Низким (неактивным), Q-сигнал является Высоким (активным).

В триггере FF1, в случае, если и SB-сигнал, и R-сигнал становятся неактивными, тогда как INITB-вход является активным (Низким), транзистор р82 и транзистор n86 выключены, а транзисторы р85, р86, n83 и n84 включены, и посредством этого Q-сигнал становится Низким и QB-сигнал становится Высоким (неактивным). В случае, когда и SB-сигнал, и R-сигнал активизируют, тогда как INITB-вход является активным (Низким), транзисторы р82, р86 и р85 включены, и посредством этого Q-сигнал становится Низким и QB-сигнал становится Высоким (неактивным). Более того, в триггере FF1 в случае, если SB-сигнал становится активным (Низким) и R-сигнал становится неактивным (Высоким), тогда как INITB-вход является активным (Низким), транзистор р82 и транзистор р85 включены и транзистор р84 выключен, и посредством этого Q-сигнал становится Низким и QB-сигнал становится Высоким (неактивным). В случае, когда SB-сигнал становится неактивным (Высоким) и R-сигнал становится активным (Высоким), тогда как INITB-вход является активным (Низким), транзисторы n81, n82 и р85 включены, и посредством этого Q-сигнал становится Низким и QB-сигнал становится Высоким (неактивным).

Фиг.4 представляет собой временную диаграмму, иллюстрирующую управление жидкокристаллическим дисплейным устройством 3a, когда электропитание включено. Отметим, что на каждом чертеже "AONB" обозначает AONB-сигнал (сигнал одновременного набора), "INITB" обозначает INITB-сигнал (сигнал инициализации), "GSPB" обозначает стартовый импульс загрузки драйвера затвора, "GCK1B" обозначает сигнал GCK1B, "GCK2B" обозначает сигнал GCK2B. Более того, "SBi", "Ri", "Qi" и "OUTi" (i=n-1, n, n+1) обозначают SB-сигнал (т.е., электрический потенциал SB-входа), R-сигнал (т.е., электрический потенциал на R-входе), Q-сигнал (т.е., электрический потенциал на Q-выходе) и OUT-сигнал (т.е., электрический потенциал на OUT выходе) соответственно на i-ом разряде SRi.

В жидкокристаллическом дисплейном устройстве 3a, например, выполняют следующую предварительную операцию, когда электропитание включено. В частности, AONB-сигнал и INITB-сигнал одновременно активизируют (Низкий) и затем INITB-сигнал возвращают в неактивный (Высокий) после того, как AONB-сигнал возвращают в неактивный (Высокий). В каждом разряде сдвигового регистра SR аналоговый переключатель ASW9 находится в состоянии on. Следовательно, OUT-сигналы всех разрядов активизируют (Высокие), и таким образом выбраны все сигнальные линии развертки. Тогда аналоговые переключатели asw, предусмотренные для соответствующих столбцовых сигнальных линий, включены, и таким образом Vcom применяют ко всем столбцовым сигнальным линиям. Более того, в триггере каждого разряда INITB-сигнал активизируют (Низкий), и посредством этого Q-сигнал становится Низким (неактивным), QB-сигнал становится Высоким (неактивным). После окончания предварительной операции (т.е., после того, как AONB-сигнал становится неактивным), Vcom записывают на все пиксели PIX в рабочем поле экрана DAR, и инициализируют сдвиговый регистр SR (т.е., выход триггера в каждом разряде становится неактивным).

Более того, в сдвиговом регистре SR жидкокристаллического дисплейного устройства 3а выполняют следующую операцию в каждом периоде кадровой развертки (в котором отображается кадр). В частности, каждый разряд сдвигового регистра SR выполнен как описано ниже. Когда SB-сигнал, поступающий на разряд в сдвиговом регистре SR, становится активным (Низким), триггер FF разряда устанавливают на единицу и таким образом Q-сигнал становится Высоким (активным). Это вызывает прием сигнала GCKB разрядом через аналоговый переключатель ASW10. Когда сигнал GCKB в разряде активизируют (Высокий), активизируют OUTB-сигнал разряда (Низкий) и активизируют SB-сигнал в разряде, следующем за данным. Это вызывает активизацию OUTB-сигнала триггера FF разряда, следующего за данным, и таким образом сигнал GCKB принимают разрядом, следующим за данным. Когда сигнал GCKB в разряде, следующем за данным, становится активным (Низким), триггер FF разряда устанавливают на нуль и таким образом Q-сигнал становится Низким (неактивным). Это вызывает включение аналогового переключателя ASW9 разряда. Тогда AONB-сигнал является Высоким, и таким образом OUTB-сигнал разряда становится также Высоким (неактивным).

В жидкокристаллическом дисплейном устройстве 3а, например, возможно применить идентичный электрический потенциал (например, Vcom) для всех пикселей одновременным выбором всех сигнальных линий развертки, когда электропитание включено. Это позволяет предотвратить неупорядоченный экран, который появляется, когда электропитание включено. Здесь, нижеупомянутое описывает состояние выхода Q триггера в сдвиговом регистре в течение интервала времени, в который INITB-сигнал является активным (Низким). То есть, даже в случае, когда и SB-сигнал, и R-сигнал смещают следующим образом: "активный → неактивный" (см. фиг.5), выход Q триггера является постоянно неактивным (Низким); даже в случае, когда SB-сигнал смещают следующим образом: "активный → неактивный → неактивный", тогда как R-сигнал смещают следующим образом: "активный → активный → неактивный" (см. фиг.6), выход Q триггера является постоянно неактивным (Низким); и даже в случае, если SB-сигнал смещают следующим образом: "активный → активный → неактивный", тогда как R-сигнал смещают следующим образом: "активный → неактивный → неактивный" (см. фиг.7), выход Q триггера является постоянно неактивным (Низким). Это позволяет стабилизировать работу сдвигового регистра, тогда как сдвиговый регистр возвращают из одновременного набора и после одновременного набора.

AONB-сигнал подают на аналоговый переключатель ASW9, и следовательно возможно уменьшить габариты драйвера затвора по сравнению со стандартной конфигурацией, аналогичной показанной на фиг.43. Более того, возможно завершить предварительную операцию быстрее по сравнению со стандартной конфигурацией, в которой одновременный выбор и инициализация сдвигового регистра выполняются раздельно.

Фиг.8 представляет собой электрическую схему, иллюстрирующую конфигурацию жидкокристаллического дисплейного устройства 3b, в которой сдвиговый регистр SR, показанный на фиг.1, предусмотрен в драйвере стока. В данной конфигурации стартовый импульс загрузки драйвера стока SSP подают на первый разряд сдвигового регистра SR, и тактовый сигнал драйвера стока SCK1B или SCK2B подают на СКВ выход каждого разряда. Более того, OUT-сигнал, поступающий от i-ого разряда SRi, подают на схему выборки SAC, и данные, отобранные на основе OUT-сигнала, подают на столбцовую сигнальную линию SLi рабочего поля экрана DAR через DAC. Например, OUT-сигнал n-ого разряда SRn подают на схему выборки SAC и затем данные, отобранные на основе OUT-сигнала, подают на столбцовую сигнальную линию SLn рабочего поля экрана DAR через DAC. В рабочем поле экрана DAR столбцовая сигнальная линия SLn соединена с истоком транзистора, соединенным с пиксельным электродом в пикселе PIXn.

Фиг.9 представляет собой электрическую схему, иллюстрирующую конфигурацию жидкокристаллического дисплейного устройства 3с, которая выполнена изменением жидкокристаллического дисплейного устройства 3а. Фиг.10 представляет собой электрическую схему, частично иллюстрирующую сдвиговый регистр SR жидкокристаллического дисплейного устройства 3с. Как показано на фиг.10, каждый разряд сдвигового регистра включает в себя (i) асинхронный RS триггер FF, имеющий SB-вход, RB-вход и INITB-вход, (ii) два аналоговых переключателя ASW3 и ASW4, (iii) инвертер и (iv) СКВ выход, ONB выход, OUT выход и OUTB выход. Q-выход триггера FF соединен с затвором с каналом p-типа аналогового переключателя ASW3 и затвором с каналом n-типа аналогового переключателя ASW4. QB-выход триггера FF соединен с затвором с каналом n-типа аналогового переключателя ASW3 и затвором с каналом p-типа аналогового переключателя ASW4. Один электрод проводимости аналогового переключателя ASW3 соединен с ONB выходом, а один электрод проводимости аналогового переключателя ASW4 соединен с СКВ выходом. Другой электрод проводимости аналогового переключателя ASW3, другой электрод проводимости аналогового переключателя ASW4 и OUTB выход, который служит выходом того разряда, соединены друг с другом. OUTB выход соединен с OUT выходом через инвертер.

В сдвиговом регистре SR каждый разряд имеет OUTB выход и RB-вход, которые соединены соответственно с SB-входом и OUTB выходом следующего разряда. Например, OUTB выход n-ого разряда SRn соединен с SB-входом (n+1)-ого разряда SRn+1, a OUTB выход (n+1)-ого разряда SRn+1 соединен с RB-входом n-ого разряда SRn. Отметим, что первый разряд SR1 сдвигового регистра SR имеет SB-вход, на который подают GSPB сигнал. В драйвере затвора GD INITB-входы триггеров соответствующих разрядов соединены с линией передачи INITB-сигнала, а ONB выходы соответствующих разрядов соединены с линией передачи AONB-сигнала. Более того, СКВ выход разряда с нечетным номером соединен с линией GCKB (через которую подают тактовый сигнал драйвера затвора GCKB), отличной от линии GCKB, с которой соединен СКВ выход разряда с четным номером. Например, СКВ выход n-ого разряда SRn соединен с линией передачи сигнала GCK2B, а СКВ выход (n+1)-ого разряда SRn+1 соединен с линией передачи сигнала GCK1B.

В качестве триггера FF, показанного на фиг.10, используется триггер FF2, показанный на фиг.11. Как показано на фиг.11, триггер FF2 включает в себя (i) транзистор с каналом p-типа р6 и транзистор с каналом n-типа n5, которые образуют микросхему CMOS, (ii) транзистор с каналом p-типа р8 и транзистор с каналом n-типа n7, которые образуют микросхему CMOS, (iii) транзисторы с каналом p-типа р5 и р7, (iv) транзисторы с каналом n-типа n6 и n8 и (v) INITB-вход, SB-вход, RB-вход, Q-выход и QB-выход. Затвор транзистора р6, затвор транзистора n5, сток транзистора р7, сток транзистора р8, сток транзистора n7 и QB-выход соединены друг с другом. Сток транзистора р6, сток транзистора n5, сток транзистора р5, затвор транзистора р8 и затвор транзистора n7 и Q-выход соединены друг с другом. Исток транзистора n5 соединен со стоком транзистора n6. Исток транзистора n7 соединен со стоком транзистора n8. SB-вход соединен с затвором транзистора р5 и затвором транзистора n6. RB-вход соединен с истоком транзистора р5, затвором транзистора р7 и затвором транзистора n8. INITB-вход соединен с истоком транзистора р6. Истоки транзисторов р7 и р8 соединены с VDD, а истоки транзисторов n6 и n8 соединены с VSS. Здесь, транзисторы р6, n5, р8 и n7 образуют триггерную запирающую схему LC, транзистор р5 служит транзистором с установкой ST, транзистор р7 служит транзистором со сбросом RT и каждый из транзисторов n6 и n8 служит транзистором сброса запирающего триггера (транзистором сброса) LRT.

(b) на фиг.11 представляет собой временную диаграмму, иллюстрирующую управление триггером FF2, а (c) на фиг.11 представляет собой таблицу истинности триггера FF2. В триггере FF2, Q-сигнал находится в состоянии, как описано ниже (см. (b) и (c) на фиг.11): в течение интервала времени, в который SB-сигнал является Низким (активным) и RB-сигнал является Низким (активным), Q-сигнал является Низким (неактивным); в течение интервала времени, в который SB-сигнал является Низким (активным) и RB-сигнал является Высоким (неактивным), Q-сигнал является Высоким (активным); в течение интервала времени, в который SB-сигнал является Высоким (неактивным) и RB-сигнал является Низким (активным), Q-сигнал является Низким (неактивным); и в течение интервала времени, в который SB-сигнал является Высоким (неактивным) и RB-сигнал является Высоким (неактивным), Q-сигнал находится в состоянии удержания.

Фиг.12 иллюстрирует управление жидкокристаллическим дисплейным устройством 3с, когда электропитание включено. В данной конфигурации, в течение интервала времени, в который INITB-сигнал является активным (Низким), выход Q триггера имеет состояние, как описано ниже. То есть, даже в случае, если и SB-сигнал, и RB-сигнал смещают следующим образом: "активный → неактивный" (см. фиг.13), выход Q триггера является постоянно неактивным (Низким); даже в случае, когда SB-сигнал смещают следующим образом: "активный → неактивный → неактивный", тогда как RB-сигнал смещают следующим образом: "активный → активный → неактивный" (см. фиг.14), выход Q триггера является постоянно неактивным (Низким); и даже в случае, когда SB-сигнал смещают следующим образом: "активный → активный → неактивный", тогда как RB-сигнал смещают следующим образом: "активный → неактивный → неактивный" (см. фиг.15), выход Q триггера является в основном неактивным (Низким), за исключением момента времени, когда выход Q не определен (т.е., в течение интервала времени, в который SB-сигнал является активным и RB-сигнал является неактивным). Это позволяет стабилизировать работу сдвигового регистра, тогда как сдвиговый регистр возвращается из одновременного выбора и после одновременного выбора.

Отметим, что INITB-сигнал, который используется в каждом из жидкокристаллических дисплейных устройств 3а-3с, может быть образован, как показано, например, на (a) и (b) на фиг.16. В частности, AONB-сигнал поступает на схему задержки, выполненную множеством схем инвертера, которые соединены друг с другом каскадированием, и выход схемы задержки и AONB-сигнал подают на микросхему AND. Затем, выход микросхемы AND используют в качестве INITB-сигнала. И наоборот, INITB-сигнал может быть образован, как показано на (a) и (b) Фиг.17. В частности, AONB-сигнал поступает на SB-вход (вход установки единицы) асинхронного RS триггера и GSPB (стартовый импульс загрузки драйвера затвора) поступает на RB-вход (вход установки нуля) триггера, и затем выход (QB-сигнал) триггера используется в качестве INITB-сигнала.

Вариант осуществления 2

Фиг.18 представляет собой электрическую схему, иллюстрирующую конфигурацию жидкокристаллического дисплейного устройства 3d настоящего изобретения. Жидкокристаллическое дисплейное устройство 3d включает в себя рабочее поле экрана DAR, драйвер затвора GD, драйвер стока SD и микросхему дисплейного контроллера DCC. Схема возбуждения дисплея DCC подает на драйвер затвора GD INITB-сигнал (сигнал инициализации), AONB-сигнал (сигнал одновременного набора), стартовый импульс загрузки драйвера затвора GSP, сигнал разрешения работы драйвера затвора GOE и тактовые сигналы драйвера затвора GCK1B и GCK2B. Более того, схема возбуждения дисплея DCC подает на драйвер стока SD стартовый импульс загрузки драйвера стока SSP, цифровые данные DAT, сигнал полярности POL и тактовый сигнал драйвера стока SCK. Драйвер затвора GD включает в себя сдвиговый регистр SR, имеющий множество разрядов. Ниже, i-ый разряд (i=1, … n-1, n, n+1, …) сдвигового регистра соответственно сокращенно именуют "i-ым разрядом SRi".

Выходной сигнал (OUT-сигнал) i-ого разряда SRi сдвигового регистра поступает на сигнальную линию развертки Gi рабочего поля экрана DAR через буфер. Например, OUTB-сигнал n-ого разряда SRn поступает на сигнальную линию развертки Gn через буфер. В рабочем поле экрана DAR сигнальная линия развертки Gn соединена с затвором транзистора, который соединен с пиксельным электродом в пикселе PIXn. Конденсатор хранения (дополнительный конденсатор) образован пиксельным электродом в пикселе PIXn и линией конденсатора хранения CSn.

Более того, один (1) аналоговый переключатель asw и один (1) инвертор предусмотрены для каждой столбцовой сигнальной линии. Инвертер имеет вход, соединенный с линией передачи AONB-сигнала. Один электрод проводимости аналогового переключателя asw соединен с концом столбцовой сигнальной линии, а другой электрод проводимости аналогового переключателя asw соединен с электропитанием Vcom (общий электродный электрический потенциал). Затвор с каналом n-типа аналогового переключателя asw соединен с выходом инвертера, а затвор с каналом р-типа аналогового переключателя asw соединен с линией AONB-сигнала.

Фиг.19 представляет собой электрическую схему, частично иллюстрирующую точную конфигурацию сдвигового регистра SR. Как показано на фиг.19, каждый разряд сдвигового регистра включает в себя (i) триггер FF (триггер FF2, показанный на фиг.11), имеющий INITB-вход, SB-вход и RB-вход, (ii) два аналоговых переключателя ASW5 и ASW6 (схему логического элемента), (iii) микросхему NAND (логическую схему), (iv) инвертор, (v) СКВ выход, (vi) ONB выход и (vii) OUTB выход. QB-выход триггера FF соединен с одним входом микросхемы NAND, а выход микросхемы NAND соединен с входом инвертора, затвором с каналом p-типа аналогового переключателя ASW5 и затвором с каналом n-типа аналогового переключателя ASW6. Выход инвертера соединен с затвором с каналом n-типа аналогового переключателя ASW5 и затвором с каналом p-типа аналогового переключателя ASW6. Один электрод проводимости аналогового переключателя ASW5 соединен с ONB выходом, а один электрод проводимости аналогового переключателя ASW6 соединен с СКВ выходом. Другой электрод проводимости аналогового переключате