Схема и способ управления мощностью в множестве каналов

Иллюстрации

Показать всеИзобретение относится к области технологий устройств связи и предназначено для управления мощностью в множестве каналов. Технический результат - уменьшение времени измерения мощности. Способ осуществляет выбор, в соответствии с сигналом выбора канала в последнем цикле тактовой синхронизации, сигнала одного канала из принимаемых сигналов, по меньшей мере, одного канала в последнем цикле тактовой синхронизации; усиление, в соответствии с сигналом управления коэффициентом усиления в последнем цикле тактовой синхронизации, сигнала одного выбранного канала для получения первого сигнала; выполнение аналогово-цифрового преобразования первого сигнала для получения второго сигнала; и генерацию, в соответствии со вторым сигналом, сигнала управления коэффициентом усиления в следующем цикле тактовой синхронизации, для усиления, в соответствии с сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации, сигнала одного выбранного канала в следующем цикле тактовой синхронизации во время следующего цикла тактовой синхронизации. Данная схема может быть применена для измерения мощности в множестве каналов сигнала, при этом ее реализация является простой. 2 н. и 9 з.п. ф-лы, 7 ил.

Реферат

Область техники

Настоящее изобретение относится к области технологий устройств связи, в частности к схеме и способу управления мощностью в множестве каналов.

Предпосылки создания изобретения

В системах передачи оптических сигналов для реализации мультиплексирования с добавлением/ответвлением оптических сигналов часто применяют платы блоков добавления/ответвления оптических сигналов (optical add/drop, OAD), при этом принцип организации путей оптических сигналов показан на фиг.1. Роль OAD в системе передачи оптических сигналов заключается в обеспечении мультиплексирования и демультиплексирования с добавлением/ответвлением каналов в одной полосе частот, при этом А1, А2, A3 и А4 - оптические порты в канале добавления, состоящем из четырех сигналов с определенными длинами волн OAD, причем локальные службы, обеспечивающие передачу в восходящем направлении, подключают к системе через эти четыре оптических порта, a D1, D2, D3 и D4 - оптические порты в канале ответвления, состоящем из четырех сигналов с определенными длинами волны OAD, причем службы, обеспечивающие передачу в системе в нисходящем направлении, доставляют данные в локальную область через эти четыре оптических порта, a IN и OUT - входные и выходные оптические порты OAD, соответственно. На практике в сетевых системах необходимо измерять мощность оптических сигналов в оптических портах А1, А2, A3, А4, D1, D2, D3, и D4 в каналах добавления и ответвления, соответственно. Функцию обслуживания канала добавления/ответвления реализуют посредством одного модуля мультиплексирования и демультиплексирования оптических сигналов, размещаемого в блоке OAD, при этом в упомянутый модуль интегрируют PIN-диод. С помощью PIN-диода оптический сигнал, проходящий через восемь оптических портов в каналах добавления и ответвления, преобразуют в сигнал тока, который, как правило, является очень слабым и может быть использован только после усиления.

Вследствие влияния таких факторов, как интенсивность сигнала, эффективность фотоэлектрического преобразования PIN-диода, а также вносимых потерь сигнала, интенсивности сигналов в различных оптических портах в канале добавления/ответвления могут значительно отличаться друг от друга. Если коэффициент усиления схемы усилителя остается постоянным, сильный сигнал может уйти в насыщение, а слабые сигналы могут быть потеряны, вследствие чего происходит искажение сигнала. Соответственно, коэффициент усиления схемы усилителя должен меняться в зависимости от интенсивности входного сигнала, при этом необходимо измерять интенсивность сигнала в каждом канале. Для реализации схемы измерения в множестве каналов на существующем уровне техники в каждом канале необходимо использовать отдельную схему измерения, при этом используется большое количество резисторов, конденсаторов и активных устройств, в результате чего схема получается относительно сложной.

Сущность изобретения

Технической задачей, которую решает настоящее изобретение, является предоставление простой схемы и способа управления мощностью в множестве каналов.

Для решения указанной технической задачи в примерах осуществления настоящего изобретения предложена следующая техническая схема:

с одной стороны, в настоящем изобретении предложена схема для управления мощностью в множестве каналов, содержащая:

модуль выбора отдельного канала, сконфигурированный таким образом, что его первый вход осуществляет ввод сигнала выбора канала в последнем цикле тактовой синхронизации; его второй вход осуществляет ввод сигнала по меньшей мере одного канала в последнем цикле тактовой синхронизации; его выход осуществляет вывод в последнем цикле тактовой синхронизации сигнала одного канала, выбранного из сигналов по меньшей мере одного канала в последнем цикле тактовой синхронизации, в соответствии с сигналом выбора канала в последнем цикле тактовой синхронизации;

модуль усиления, сконфигурированный таким образом, что его первый вход осуществляет ввод сигнала управления коэффициентом усиления в последнем цикле тактовой синхронизации; его второй вход осуществляет ввод упомянутого сигнала одного канала, выбранного в последнем цикле тактовой синхронизации; а его выход осуществляет вывод первого сигнала, полученного путем усиления упомянутого сигнала одного канала, выбранного в последнем цикле тактовой синхронизации, в соответствии с упомянутым сигналом управления коэффициентом усиления в последнем цикле тактовой синхронизации;

модуль аналогово-цифрового преобразования, сконфигурированный таким образом, что его вход осуществляет ввод упомянутого первого сигнала; его выход осуществляет вывод второго сигнала, полученного путем аналогово-цифрового преобразования первого сигнала; и

модуль управления усилением, сконфигурированный таким образом, что его вход осуществляет ввод упомянутого второго сигнала; его первый выход соединен с первым входом модуля выбора отдельного канала и осуществляет вывод сигналов выбора канала в последнем цикле тактовой синхронизации и в следующем цикле тактовой синхронизации, при этом сигнал выбора канала в следующем цикле тактовой синхронизации является тем же самым, что и в последнем цикле тактовой синхронизации; его второй выход соединен с первым входом упомянутого модуля усиления и осуществляет вывод сигнала управления коэффициентом усиления в последнем цикле тактовой синхронизации, а также осуществляет вывод сигнала управления коэффициентом усиления в следующем цикле тактовой синхронизации, сгенерированного в соответствии со вторым сигналом, так что модуль усиления усиливает сигнал одного канала, выбираемого в следующем цикле тактовой синхронизации, в соответствии с упомянутым сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации.

Упомянутый модуль усиления включает:

первый усилитель, сконфигурированный таким образом, что его неинвертирующий вход соединен с выходом упомянутого модуля выбора отдельного канала; инвертирующий вход, соответственно, соединен с первым выводом резистора делителя и первым выводом по меньшей мере одного резистора обратной связи; при этом его выход соединен со входом упомянутого модуля аналогово-цифрового преобразования; и

первый аналоговый переключатель типа "один из множества", сконфигурированный таким образом, что его по меньшей мере один первый вход соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора обратной связи; его второй вход соединен со вторым выходом упомянутого модуля управления усилением;

при этом второй вывод упомянутого резистора делителя соединен с землей, а количество резисторов обратной связи совпадает с количеством первых входов упомянутого аналогового переключателя типа "один из множества".

Упомянутый модуль усиления содержит:

первый усилитель, сконфигурированный таким образом, что его неинвертирующий вход соединен с выходом упомянутого модуля выбора отдельного канала; инвертирующий вход, соответственно, соединен с первым выводом резистора делителя и первым выводом по меньшей мере одного резистора обратной связи;

первый аналоговый переключатель типа "один из множества", сконфигурированный таким образом, что его по меньшей мере один первый вход соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора обратной связи; его второй вход соединен со вторым выходом упомянутого модуля управления усилением; и

второй усилитель, сконфигурированный таким образом, что его неинвертирующий вход соединен с выходом упомянутого первого усилителя; его инвертирующий вход соединен с выходом второго усилителя; его выход соединен со входом упомянутого модуля аналогово-цифрового преобразования;

при этом второй вывод упомянутого резистора делителя соединен с землей, и количество резисторов обратной связи совпадает с количеством первых входов упомянутого переключателя типа "один из множества".

Упомянутый модуль усиления содержит:

первый усилитель, сконфигурированный таким образом, что его неинвертирующий вход соединен с выходом упомянутого модуля выбора отдельного канала; инвертирующий вход, соответственно, соединен с первым выводом резистора делителя и первым выводом по меньшей мере одного резистора обратной связи;

первый аналоговый переключатель типа "один из множества", сконфигурированный таким образом, что его по меньшей мере один первый вход соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора обратной связи; его второй вход соединен со вторым выходом упомянутого модуля управления усилением; его выход соединен с выходом упомянутого первого усилителя; и

второй аналоговый переключатель типа "один из множества", сконфигурированный таким образом, что его по меньшей мере один первый вход соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора обратной связи; его второй вход соединен со вторым выходом упомянутого модуля управления усилением; его выход соединен со входом упомянутого модуля аналогово-цифрового преобразования;

при этом второй вывод упомянутого резистора делителя соединен с землей, количество резисторов обратной связи совпадает с количеством первых входов упомянутого первого переключателя типа "один из множества", и количество первых входов упомянутого второго аналогового переключателя типа "один из множества" совпадает с количеством первых входов упомянутого первого аналогового переключателя типа "один из множества".

Упомянутый модуль усиления содержит:

первый усилитель, сконфигурированный таким образом, что его неинвертирующий вход соединен с выходом упомянутого модуля выбора отдельного канала; инвертирующий вход, соответственно, соединен с первым выводом резистора делителя и первым выводом по меньшей мере одного резистора обратной связи;

первый аналоговый переключатель типа "один из множества", сконфигурированный таким образом, что его по меньшей мере один первый вход соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора обратной связи; его второй вход соединен со вторым выходом упомянутого модуля управления усилением; его выход соединен с выходом упомянутого первого усилителя; и

второй аналоговый переключатель типа "один из множества", сконфигурированный таким образом, что его по меньшей мере один первый вход соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора обратной связи; его второй вход соединен со вторым выходом упомянутого модуля управления усилением; и

второй усилитель, сконфигурированный таким образом, что его неинвертирующий вход соединен с выходом упомянутого второго аналогового переключателя типа "один из множества"; его инвертирующий вход соединен с выходом второго усилителя; и выход второго усилителя соединен со входом упомянутого модуля аналогово-цифрового преобразования;

при этом второй вывод упомянутого резистора делителя соединен с землей, количество резисторов обратной связи совпадает с количеством первых входов упомянутого первого переключателя типа "один из множества", и количество первых входов упомянутого второго аналогового переключателя типа "один из множества" совпадает с количеством первых входов упомянутого первого аналогового переключателя типа "один из множества".

Коэффициент усиления в упомянутом сигнале управления коэффициентом усиления в следующем цикле тактовой синхронизации составляет k=1+Rf/R0, где Rf - сопротивление резистора, выбираемого из по меньшей мере одного резистора обратной связи в соответствии с сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации, a R0 - сопротивление резистора делителя.

Коэффициент усиления k устанавливают равным степени числа 2.

Упомянутый модуль выбора отдельного канала также сконфигурирован: для соединения его второго входа с выходом модуля мультиплексирования и демультиплексирования оптических сигналов на плате блока добавления/ответвления оптических сигналов (OAD).

Если присутствует более одного упомянутого резистора обратной связи, то значения сопротивления этих резисторов являются различными.

Упомянутый сигнал выбора канала представляет собой сигнал, выбираемый поочередным циклическим перебором сигналов каждого канала из принимаемых сигналов упомянутого по меньшей мере одного канала.

С другой стороны, в настоящем изобретении предложен способ управления мощностью в множестве каналов, содержащий:

выбор в последнем цикле тактовой синхронизации сигнала одного канала из принимаемых сигналов по меньшей мере одного канала в последнем цикле тактовой синхронизации в соответствии с сигналом выбора канала в последнем цикле тактовой синхронизации;

усиление упомянутого сигнала одного канала, выбранного в последнем цикле тактовой синхронизации, в соответствии с сигналом управления коэффициентом усиления в последнем цикле тактовой синхронизации для получения первого сигнала;

выполнение аналогово-цифрового преобразования первого сигнала для получения второго сигнала; и

генерирование сигнала управления коэффициентом усиления в следующем цикле тактовой синхронизации в соответствии с упомянутым вторым сигналом для усиления упомянутого сигнала одного канала, выбираемого в следующем цикле тактовой синхронизации в соответствии с сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации при его наступлении, при этом упомянутый сигнал одного канала, выбранный в последнем цикле тактовой синхронизации, является тем же самым, что и сигнал одного канала, выбираемый в следующем цикле тактовой синхронизации.

Примеры настоящего изобретения обладают следующими преимуществами:

В описанной выше схеме в течение последнего цикла тактовой синхронизации модуль выбора отдельного канала выбирает сигнал одного канала в последнем цикле тактовой синхронизации из сигналов по меньшей мере одного канала, принимаемых в последнем цикле тактовой синхронизации, в соответствии с сигналом выбора канала в последнем цикле тактовой синхронизации; модуль усиления усиливает выбранный сигнал одного канала в последнем цикле тактовой синхронизации в соответствии с сигналом управления коэффициентом усиления в последнем цикле тактовой синхронизации для получения первого сигнала; модуль аналогово-цифрового преобразования осуществляет аналогово-цифровое преобразование первого сигнала для получения второго сигнала; модуль управления усилением генерирует сигнал управления коэффициентом усиления в следующем цикле тактовой синхронизации в соответствии с упомянутым вторым сигналом.

Сигнал выбора канала в следующем цикле тактовой синхронизации является тем же самым, что и в последнем цикле тактовой синхронизации, соответственно, выбранный сигнал одного канала в последнем цикле тактовой синхронизации является тем же самым, что и сигнал в следующем цикле тактовой синхронизации. В следующем цикле тактовой синхронизации модуль выбора отдельного канала выбирает сигнал одного канала, который является тем же самым, что и сигнал канала, выбранного в последнем цикле тактовой синхронизации; модуль усиления усиливает сигнал выбранного канала в следующем цикле тактовой синхронизации в соответствии с сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации. Следовательно, в следующем цикле тактовой синхронизации сигнал выбранного канала может быть усилен с использованием подходящего коэффициента усиления. Для многоканального сигнала, подаваемого на вход модуля выбора отдельного канала, не требуется установка отдельной схемы измерения сигналов каждого канала, и схема управления мощностью в множестве каналов может использоваться совместно, соответственно, реализация схемы является относительно простой.

Краткое описание чертежей

Фиг.1 представляет собой схему пути оптического сигнала в блоке OAD на существующем уровне техники.

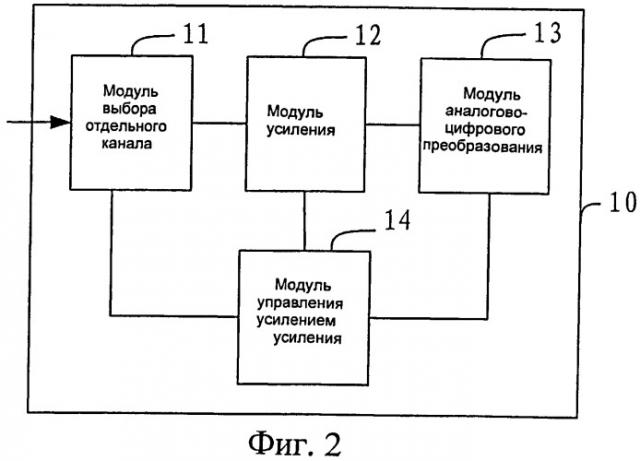

Фиг.2 представляет собой схему соединений одного из примеров схемы для управления мощностью в множестве каналов в соответствии с настоящим изобретением.

Фиг.3 представляет собой схему соединений другого примера схемы для управления мощностью в множестве каналов в соответствии с настоящим изобретением.

Фиг.4 представляет собой схему соединений еще одного примера схемы для управления мощностью в множестве каналов в соответствии с настоящим изобретением.

Фиг.5 представляет собой схему соединений еще одного примера схемы для управления мощностью в множестве каналов в соответствии с настоящим изобретением.

Фиг.6 представляет собой схему соединений еще одного примера схемы для управления мощностью в множестве каналов в соответствии с настоящим изобретением.

Фиг.7 представляет собой блок-схему алгоритма одного из примеров способа управления мощностью в множестве каналов в соответствии с настоящим изобретением.

Предпочтительные варианты осуществления настоящего изобретения

Для пояснения упомянутой, требующей решения, технической задачи, технической схемы и преимуществ настоящего изобретения, оно будет описано более подробно совместно с приложенными чертежами и конкретными примерами.

Для решения проблемы, заключающейся в сложности схемы существующего уровня техники и возникающей вследствие применения отдельной схемы измерения для каждого канала, в одном из примеров настоящего изобретения предложены схема и способ управления мощностью в множестве каналов.

Фиг.2 представляет собой один из примеров схемы 10 управления мощностью в множестве каналов, в соответствии с настоящим изобретением, при этом схема содержит:

модуль 11 выбора отдельного канала, модуль 12 усиления, модуль 13 аналогово-цифрового преобразования, и модуль 14 управления усилением.

Модуль 11 выбора отдельного канала сконфигурирован таким образом, что его первый вход осуществляет ввод сигнала выбора канала в последнем цикле тактовой синхронизации; его второй вход осуществляет ввод сигнала по меньшей мере одного канала в последнем цикле тактовой синхронизации; его выход в последнем цикле тактовой синхронизации осуществляет вывод сигнала одного канала, выбранного в последнем цикле тактовой синхронизации из упомянутых сигналов по меньшей мере одного канала в соответствии с сигналом выбора канала в последнем цикле тактовой синхронизации;

модуль 12 усиления сконфигурирован таким образом, что его первый вход осуществляет ввод сигнала управления коэффициентом усиления в последнем цикле тактовой синхронизации; его второй вход осуществляет ввод упомянутого сигнала одного канала, выбранного в последнем цикле тактовой синхронизации; и его выход осуществляет вывод первого сигнала, полученного путем усиления упомянутого сигнала одного канала, выбранного в последнем цикле тактовой синхронизации, в соответствии с упомянутым сигналом управления коэффициентом усиления в последнем цикле тактовой синхронизации;

модуль 13 аналогово-цифрового преобразования сконфигурирован таким образом, что его вход осуществляет ввод упомянутого первого сигнала; его выход осуществляет вывод второго сигнала, полученного путем аналогово-цифрового преобразования первого сигнала;

модуль 14 управления усилением сконфигурирован таким образом, что его вход осуществляет ввод упомянутого второго сигнала; его первый выход соединен с первым входом модуля 11 выбора отдельного канала и используется для вывода сигналов выбора канала в последнем цикле тактовой синхронизации и в следующем цикле тактовой синхронизации, при этом сигнал выбора канала в следующем цикле тактовой синхронизации является тем же самым, что и в последнем цикле тактовой синхронизации; его второй выход соединен с первым входом модуля 12 усиления, при этом его используют для вывода сигнала управления коэффициентом усиления в последнем цикле тактовой синхронизации, а также сигнала управления коэффициентом усиления в следующем цикле тактовой синхронизации, сгенерированного в соответствии с упомянутым вторым сигналом, так что модуль 12 усиления усиливает сигнал одного выбранного канала в следующем цикле тактовой синхронизации, в соответствии с упомянутым сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации.

В начале работы схемы управления мощностью в множестве каналов, то есть в последнем цикле тактовой синхронизации, модуль 12 усиления использует коэффициент усиления, задаваемый по умолчанию, то есть модуль 14 управления усилением выдает назначаемый по умолчанию или заданный заранее сигнал управления коэффициентом усиления и определяет выходной сигнал управления коэффициентом усиления в следующем цикле тактовой синхронизации в соответствии с подаваемым на вход вторым сигналом в последнем цикле тактовой синхронизации для управления коэффициентом усиления модуля 12 усиления в следующем цикле тактовой синхронизации.

В описанной выше схеме в течение последнего цикла тактовой синхронизации модуль 11 выбора отдельного канала выбирает сигнал одного канала в последнем цикле тактовой синхронизации из сигналов по меньшей мере одного канала, принимаемых в последнем цикле тактовой синхронизации, в соответствии с сигналом выбора канала в последнем цикле тактовой синхронизации; модуль 12 усиления усиливает сигнал одного канала, выбранного в последнем цикле тактовой синхронизации, в соответствии с сигналом управления коэффициентом усиления в последнем цикле тактовой синхронизации для получения первого сигнала; модуль 13 аналогово-цифрового преобразования осуществляет аналогово-цифровое преобразование первого сигнала для получения второго сигнала; модуль 14 управления усилением генерирует сигнал управления коэффициентом усиления в следующем цикле тактовой синхронизации в соответствии с упомянутым вторым сигналом.

Сигнал выбора канала в следующем цикле тактовой синхронизации является тем же самым, что и в последнем цикле тактовой синхронизации, соответственно, выбранный сигнал одного канала в последнем цикле тактовой синхронизации является тем же самым, что и в следующем цикле тактовой синхронизации. В следующем цикле тактовой синхронизации модуль выбора отдельного канала выбирает сигнал одного канала, который является тем же самым, что и сигнал канала, выбранного в последнем цикле тактовой синхронизации; модуль 12 усиления усиливает сигнал выбранного канала в следующем цикле тактовой синхронизации в соответствии с сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации. Следовательно, в следующем цикле тактовой синхронизации, для усиления упомянутого сигнала может быть использован подходящий коэффициент усиления. Для многоканального сигнала, подаваемого на вход модуля выбора отдельного канала, не требуется применение отдельной схемы измерения для каждого канала, так как схема управления мощностью в множестве каналов может использоваться совместно, соответственно, реализация схемы является относительно простой.

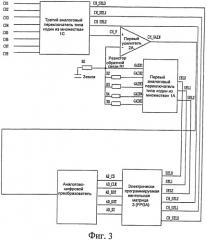

На фиг.3 представлен еще один пример схемы 10 управления мощностью в множестве каналов в соответствии с настоящим изобретением, при этом в данной схеме упомянутый модуль выбора отдельного канала представляет собой аналоговый переключатель 1C типа "один из множества", упомянутый модуль аналогово-цифрового преобразования представляет собой аналогово-цифровой преобразователь 4, и модуль управления усилением представляет собой электрически программируемую вентильную матрицу (field programmable gate array, FPGA) 3 или специальную микросхему управления усилением.

Упомянутый модуль 13 усиления содержит:

первый усилитель 2А, при этом неинвертирующий вход первого усилителя 2А соединен с выходом упомянутого модуля выбора отдельного канала; инвертирующий вход первого усилителя 2А, соответственно, соединен с первым выводом резистора R0 делителя и первым выводом по меньшей мере одного резистора Rf обратной связи; при этом выход первого усилителя соединен со входом упомянутого модуля аналогово-цифрового преобразования;

первый аналоговый переключатель 1А типа "один из множества", при этом по меньшей мере один первый вход первого аналогового переключателя 1А типа "один из множества" соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора Rf обратной связи; второй вход первого аналогового переключателя 1А типа "один из множества" соединен со вторым выходом упомянутого модуля управления усилением; и

при этом второй вывод упомянутого резистора R0 делителя соединен с землей, а количество резисторов обратной связи совпадает с количеством первых входов упомянутого первого переключателя 1А типа "один из множества", при этом значения сопротивления резисторов Rf обратной связи являются различными.

Принцип работы настоящего изобретения будет проиллюстрирован с помощью фиг.3.

В последнем цикле тактовой синхронизации сигналы по меньшей мере одного канала, которыми в настоящем примере являются, соответственно, СН1, СН2, СН3, СН4, СН5, СН6, СН7 и СН8, подают на третий аналоговый переключатель типа "один из множества", и по меньшей мере один сигнал выбора канала, которыми в настоящем примере являются CH_SEL0, CH_SEL1 и CH_SEL2 из FPGA3, при этом на выходе модуля 11 выбора отдельного канала получают сигнал CH_V одного канала, выбранный из сигналов каналов в соответствии с упомянутым сигналом выбора канала.

Неинвертирующий вход первого усилителя 2А соединен с выходом упомянутого модуля выбора отдельного канала, то есть осуществляет ввод выбранного сигнала CH_V одного канала; а инвертирующий вход первого усилителя 2А, соответственно, соединен с первым выводом резистора R0 делителя и первым выводом по меньшей мере одного резистора обратной связи Rf, при этом в данном примере резисторы Rf обратной связи включают R1 (чье сопротивление равно 0 Ом, не показан на чертеже), R2, R3, R4 и R5, а выход первого усилителя 2А соединен со входом модуля аналогово-цифрового преобразования, то есть осуществляет вывод усиленного сигнала CH_GAIN. Специалистам в настоящей области техники следует понимать, что может быть выполнено большее количество резисторов Rf обратной связи. Максимальное количество резисторов Rf обратной связи, которое может быть выполнено зависит как степень числа 2 от количества сигналов управления коэффициентом усиления, то есть если имеются восемь резисторов Rf обратной связи, количество сигналов управления коэффициентом усиления может быть равно трем.

В первом аналоговом переключателе 1А типа "один из множества" по меньшей мере один первый вход (которыми в настоящем примере являются GAIN1, GAIN2, GAIN3, GAIN4 и GAIN5) соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора обратной связи Rf (в данном примере резисторами обратной связи являются R1, R2, R3, R4 и R5), при этом сигнал, подаваемый на второй вход первого аналогового переключателя 1А типа "один из множества", представляет собой сигнал управления коэффициентом усиления из модуля управления усилением, то есть на второй вход первого аналогового переключателя 1А осуществляют ввод вторых сигналов SEL0, SEL1, SEL выбора микросхемы.

Второй вывод упомянутого резистора R0 делителя соединен с землей, а количество резисторов Rf обратной связи совпадает с количеством первых входов упомянутого первого переключателя 1А типа "один из множества", причем значения сопротивления резисторов Rf обратной связи являются различными.

Вход аналогово-цифрового преобразователя 4 осуществляет ввод усиленного сигнала, то есть первого сигнала CH_GAIN, а выход аналогово-цифрового преобразователя 4 осуществляет вывод усиленного и преобразованного в цифровую форму сигнала, то есть второго сигнала AD_OUT.

Вход FPGA 3 осуществляет ввод усиленного и оцифрованного сигнала, то есть второго сигнала AD_OUT, и осуществляет вывод сигналов выбора канала, которыми в настоящем примере являются, соответственно, CH_SEL0, CH_SEL1 и CH_SEL2, а также осуществляет вывод сигналов управления коэффициентом усиления в последнем цикле тактовой синхронизации и в следующем цикле тактовой синхронизации, при этом сигналами управления коэффициентом усиления в настоящем примере являются SEL0, SEL1 и SEL2, а сигнал управления коэффициентом усиления в следующем цикле тактовой синхронизации генерируют в соответствии со значением упомянутого второго сигнала.

В настоящем примере в течение последнего цикла тактовой синхронизации модуль управления усилением осуществляет ввод второго сигнала и генерирует сигнал управления коэффициентом усиления в следующем цикле тактовой синхронизации в соответствии со значением второго сигнала, а также осуществляет вывод сигнала управления коэффициентом усиления в следующем цикле тактовой синхронизации в первый аналоговый переключатель 1А типа "один из множества", так что сигнал управления коэффициентом усиления в следующем цикле тактовой синхронизации может осуществлять выбор резисторов Rf обратной связи с различными значениями сопротивления, следовательно, коэффициент усиления для выходного сигнала усилителя будет различным. Если усиленный и оцифрованный сигнал не превышает первого порога, выбирают коэффициент усиления, который больше, чем второй порог; если усиленный и оцифрованный сигнал больше или равен первому порогу, выбирают коэффициент усиления, который меньше или равен второму порогу. То есть для сильных сигналов применяют малый коэффициент усиления, а для слабых сигналов применяют большой коэффициент усиления. В настоящем примере для вычисления коэффициента усиления в следующем цикле тактовой синхронизации используют следующую формулу: коэффициент усиления схемы составляет: k=1+(Rf+Ron)/R0. Здесь Ron - сопротивление аналогового переключателя типа "один из множества" в открытом состоянии, Rf - сопротивление резистора, выбираемого из упомянутых одного или более резисторов Rf обратной связи в соответствии с сигналом управления коэффициентом усиления в следующем цикле тактовой синхронизации, a R0 - сопротивление резистора делителя.

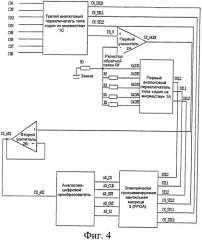

Фиг.4 представляет собой еще один пример схемы 10 управления мощностью в множестве каналов в соответствии с настоящим изобретением, при этом в данной схеме упомянутый модуль выбора отдельного канала представляет собой аналоговый переключатель 1C типа "один из множества", упомянутый модуль аналогово-цифрового преобразования представляет собой аналогово-цифровой преобразователь 4, а модуль управления усилением представляет собой электрически программируемую вентильную матрицу (FPGA) 3 или специальную микросхему управления усилением.

Упомянутый модуль 13 усиления содержит:

первый усилитель 2А, при этом неинвертирующий вход первого усилителя 2А соединен с выходом упомянутого модуля выбора отдельного канала и осуществляет ввод сигнала одного выбранного канала; инвертирующий вход первого усилителя 2А, соответственно, соединен с первым выводом резистора R0 делителя и первым выводом по меньшей мере одного резистора Rf обратной связи;

первый аналоговый переключатель 1А типа "один из множества", при этом по меньшей мере один первый вход первого аналогового переключателя 1А типа "один из множества" соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора Rf обратной связи; и второй вход первого аналогового переключателя 1А типа "один из множества" соединен со вторым выходом упомянутого модуля управления усилением;

второй усилитель 2В, при этом неинвертирующий вход второго усилителя 2В соединен с выходом первого усилителя 2А; инвертирующий вход второго усилителя 2В соединен с выходом второго усилителя 2В; выход второго усилителя 2В соединен со входом упомянутого модуля аналогово-цифрового преобразования;

второй вывод упомянутого резистора R0 делителя соединен с землей, а количество резисторов Rf обратной связи совпадает с количеством первых входов упомянутого первого переключателя 1А типа "один из множества", при этом значения сопротивления резисторов Rf обратной связи являются различными.

По сравнению с примером, изображенным на фиг.3, пример, изображенный на фиг.4, обладает следующими отличиями: усиленный сигнал CH_GAIN на выходе первого усилителя 2А на фиг.4 не подают непосредственно на вход модуля аналогово-цифрового преобразования, а подают через второй усилитель 2В, то есть, сигнал CH_GAIN вводят во второй усилитель 2В, и затем второй усилитель 2В выдает сигнал CH_ADI на вход аналогово-цифрового преобразователя 4. Коэффициент усиления второго усилителя 2В равен 1, и он выполняет функцию стабилизатора напряжения.

Фиг.5 представляет собой еще один пример схемы 10 управления мощностью в множестве каналов в соответствии с настоящим изобретением, при этом в данной схеме упомянутый модуль выбора отдельного канала представляет собой аналоговый переключатель 1C типа "один из множества", упомянутый модуль аналогово-цифрового преобразования представляет собой аналогово-цифровой преобразователь 4, а модуль управления усилением представляет собой FPGA 3 или специальную микросхему управления усилением. Упомянутый модуль 13 усиления содержит:

первый усилитель 2А, при этом его неинвертирующий вход соединен с выходом упомянутого модуля выбора отдельного канала; инвертирующий вход, соответственно, соединен с первым выводом резистора R0 делителя и первым выводом по меньшей мере одного резистора Rf обратной связи;

первый аналоговый переключатель 1А типа "один из множества", при этом по меньшей мере один первый вход первого аналогового переключателя 1А типа "один из множества" соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора Rf обратной связи; второй вход первого аналогового переключателя 1А типа "один из множества" соединен со вторым выходом упомянутого модуля управления усилением; а выход первого аналогового переключателя 1А типа "один из множества" соединен с выходом первого усилителя 2А;

второй аналоговый переключатель 1В типа "один из множества", при этом по меньшей мере один первый вход второго аналогового переключателя 1В типа "один из множества" соединен, соответственно, со вторым выводом упомянутого по меньшей мере одного резистора Rf обратной связи; второй вход второго аналогового переключателя 1В типа "один из множества" соединен со вторым выходом упомянутого модуля управления усилением; и выход второго аналогового переключателя 1В типа "один из множества" соединен со входом упомянутого модуля аналогово-цифрового преобразования;

при этом второй вывод упомянутого резистора R0 делителя соединен с землей, и количество резисторов Rf обратной связи совпадает с количеством первых входов упомянутого первого аналогового переключателя 1А типа "один из множества", и количество первых входов упомянутого второго аналогового переключателя 1В типа "один из множества" совпадает с количеством первых входов упомянутого первого аналогового переключателя 1А типа "один из множества", причем значения сопротивлений резисторов Rf обратной связи являются различными.

Далее описаны принципы работы настоящего изобретения на примере фиг.5.

Роль третьего аналогового переключателя 1C типа "один из множества" заключается в выборе сигнала одного канала из восьми входных каналов (количество входных каналов может быть любым другим) и дальнейшей передаче его в схему усиления для усиления, при этом многоканальный сигнал, ввод которого осуществляет модуль выбора отдельного канала, поступает с выхода модуля мультиплексирования и демультиплексирования оптических сигналов в блок OAD, то есть один из сигналов восьми каналов СН1, СН2, СН3, СН4, СН 5, СН6, СН7 и СН8, выводимых модулем мультиплексирования и демультиплексирования оптических сигналов, расположенном в блоке OAD, выбирают и передают в последующую схему для усиления. Сигналы CH_SEL0, CH_SEL1 и CH_SEL2 выбора канала для третьего аналогового переключателя 1C типа "один из множества" обеспечивает FPGA 3. В настоящем примере третий аналоговый переключатель 1C может представлять собой микросхему МАХ4051 производства фирмы Maxim Integrated Products, при этом микросхема МАХ4051 явля