Устройство перестановок и сдвигов битов данных в микропроцессорах

Иллюстрации

Показать всеИзобретение относится к средствам перестановок и сдвигов битов данных в микропроцессорах. Технический результат заключается в увеличении скорости выполнения операций. Устройство содержит n-разрядный вход данных X1-Xn, n-разрядный выход данных Y1-Yn, n-разрядный вход битов маскирования F1-Fn, m-разрядный вход кода управления устройства C1,1-Cn/2,k, где m=n/2k, k=log2(n), k-разрядный вход значения числа сдвига данных A0-Ak-1, бинарные входы кодов управления режимом функционирования устройства: AOR, RL, AMUX, AIOR, AOUT, АС. Устройство включает многоуровневую коммутационную сеть baseline или ibaseline 1, блок формирования битов маскирования и управления, n-разрядный мультиплексор входных данных, n-разрядный мультиплексор выходных данных, n-разрядный блок маскирования данных на входе, n-разрядный блок маскирования данных на выходе, m-разрядный мультиплексор битов управления, n-разрядный входной соединитель и n-разрядный выходной соединитель. 7 з.п. ф-лы, 9 ил., 2 табл.

Реферат

Устройство относится к области преобразования информации и может быть использовано в микропроцессорах вычислительной техники.

Известен метод и система для осуществления перестановок на базе сетей butterfly (патент US 6922472, МПК H04L 9/34 (20060101); 380/37; Method and system for performing permutations using permutation instructions based on butterfly networks / Lee; Ruby В., Yang; Xiao, Vachharajani; Manish. July 26, 2005). Устройство включает в себя две многоуровневых коммутационных сети с топологией butterfly и инверсной топологией butterfly (ibutterfly). Переключатели сетей управляются битами, поступающими с внешних регистров. Произвольная перестановка битов входных данных осуществляется с использованием двух инструкций bfly и ibfly.

Недостатком предложенного решения является сложность исполнения, связанная с необходимостью использования двух различных сетей и команд для выполнения произвольной перестановки битов данных. Кроме этого устройство не позволяет непосредственно выполнить инструкции циклических и логических сдвигов данных, а также инструкции извлечения и размещения в заданных позициях групп битов данных.

Известен метод и система для осуществления перестановок на базе модифицированных сетей omega и flip (патент US 6952478, МПК G06F 7/76 (20060101); 380/37; Method and system for performing permutations using permutation instructions based on modified omega and flip stages/Lee; Ruby В., Yang; Xiao. October 4, 2005). Устройство включает в себя две многоуровневые коммутационные сети с топологией omega и flip (ibutterfly). Переключатели сетей управляются битами, поступающими с внешних регистров. Произвольная перестановка битов входных данных осуществляется с использованием двух инструкций, связанных с прохождением данных через сети omega и flip.

Недостатком предложенного решения является сложность исполнения, связанная с необходимостью использования двух различных сетей и команд для выполнения произвольной перестановки битов данных. Кроме этого устройство не позволяет непосредственно выполнить инструкции циклических и логических сдвигов данных, а также инструкции извлечения и размещения в заданных позициях групп битов данных.

Известен универсальный блок выполнения сдвигов и перестановок, описанный в работе Hilewitz Y., Lee R.A New Basis for Shifters in General-Purpose Processors for Existing and Advanced Bit Manipulations. / IEEE Transactions on Computing. 2009. Vol.58. №.8. P.1035-1048.

Блок включает в себя две многоуровневые коммутационные сети с топологией butterfly и инверсной топологией butterfly (ibutterfly), формирователь битов управления переключателями сетей, схемы мультиплексирования и маскирования входных и выходных битов данных. Блок позволяет выполнять инструкции циклических и логических сдвигов вправо и влево, команды рех (parallel extract) и pdep (parallel deposit) извлечения и размещения в определенных позициях групп битов входных данных, произвольные перестановки битов входных данных за две команды bfly и ibfly с использованием многоуровневых коммутационных сетей butterfly и ibutterfly.

Недостатком данного решения является необходимость использования двух многоуровневых коммутационных сетей и двух команд для выполнения произвольной перестановки битов данных. Кроме этого для выполнения инструкций рех и pdep также требуется использование двух коммутационных сетей butterfly и ibutterfly.

Задачей настоящего решения является упрощение аппаратурной сложности устройства для выполнения произвольных перестановок, циклических и логических сдвигов данных, операций извлечения и размещения в заданных позициях групп битов данных за счет использования только одной многоуровневой коммутационной сети с топологией baseline или ibaseline.

Техническим результатом является упрощение конструкции устройства при сохранении высокой скорости выполнения операций.

Поставленная задача достигается тем, что устройство перестановок и сдвигов битов данных в микропроцессорах согласно решению включает многоуровневую коммутационную сеть baseline или обратную многоуровневую коммутационную сеть ibaseline, с n-разрядным входом данных X1-Xn, n-разрядным выходом данных Y1-Yn, m-разрядным входом C1,1-Cn/2,k кода управления сетью; устройство также включает n-разрядный мультиплексор 2→1 входных данных с первым n-разрядным входом X1,1-X1,n, вторым n-разрядным входом X2,1-X2,n, входом управления A, соединенным с бинарным входом AOR управления маскированием на выходе и мультиплексором входных данных устройства, n-разрядным выходом Y1-Yn, соединенным с n-разрядным входом данных X1-Xn многоуровневой коммутационной сети; устройство также включает n-разрядный входной соединитель с n-разрядным входом X1-Xn и n-разрядным выходом Y1-Yn, соединенным с первым n-разрядным входом X1,1-X1,n n-разрядного мультиплексора 2→1 входных данных, входной соединитель обеспечивает фиксированные соединения входных и выходных разрядов; устройство также включает n-разрядный блок маскирования данных на входе с первым n-разрядным входом данных X1-Xn, вторым n-разрядным входом F1-Fn, n-разрядным выходом Y1-Yn, соединенным с n-разрядным входом X1-Xn входного соединителя и со вторым n-разрядным входом X2,1-X2,n, n-разрядного мультиплексора 2→1 входных данных; устройство также включает m-разрядный мультиплексор 2→1 битов управления с входом управления AC, первым m-разрядным входом C1,1,1-C1,n/2,k битов управления, вторым m-разрядным входом C2,1,1-C2,n/2,k битов управления, m-разрядным выходом Y1,1-Yn/2,k, соединенным с m-разрядным входом C1,1-Cn/2,k кода управления сетью; устройство также включает блок формирования битов маскирования и управления, с бинарным входом AOR, соединенным с бинарным входом управления маскированием на выходе и мультиплексором входных данных устройства, бинарным входом RL управления направлением сдвига данных, бинарным входом AMUX управления мультиплексором битов маскирования, бинарным входом AIOR управления маскированием на входе, n-разрядным входом F1-Fn битов маскирования, k-разрядным входом A0-Ak-1 значения числа сдвига данных, n-разрядным выходом FI1-FIn битов маскирования входных данных, соединенным со вторым n-разрядным входом F1-Fn блока маскирования данных на входе, n-разрядным выходом FO1-FOn битов маскирования выходных данных, (n-1)-разрядным выходом С1-Cn-1 кода маскирования данных на входе, (n-1)-разрядным выходом C1-Cn-1 кода управления сдвигом, соединенным с вторым m-разрядным входом С2,1,1-C2,n/2,k битов управления мультиплексора 2→1 битов управления; устройство также включает n-разрядный блок маскирования данных на выходе с первым n-разрядным входом Х1-Xn, соединенным с n-разрядным выходом данных Y1-Yn многоуровневой коммутационной сети, вторым n-разрядным входом F1-Fn, соединенным с n-разрядным выходом битов маскирования выходных данных FO1-FOn, n-разрядным выходом Y1-Yn; устройство также включает n-разрядный выходной соединитель с n-разрядным выходом Y1-Yn, n-разрядным входом Х1-Xn, соединенным с n-разрядным выходом Y1-Yn n-разрядного блока маскирования данных на выходе, выходной соединитель обеспечивает фиксированные соединения входных и выходных разрядов; устройство также включает n-разрядный мультиплексор 2→1 выходных данных с первым n-разрядным входом X1,1-X1,n, соединенным с n-разрядным выходом Y1-Yn n-разрядного блока маскирования данных на выходе, вторым n-разрядным входом X2,1-X2,n, соединенным с n-разрядным выходом Y1-Yn n-разрядного выходного соединителя, входом управления A, соединенным с бинарным входом управления мультиплексором выходных данных AOUT устройства, n-разрядным выходом данных Y1-Yn. При использовании сети baseline бит i-го разряда Ci, i = 1, n − 1 ¯ кода управления сдвигом подают на входы разрядов C2,q,r второго m-разрядного входа мультиплексора битов управления, где индекс q - целое число и INT(i-2r-1)·2k-r<q<(INT((i-2r-1))+l)·2k-r+1, r=INT(log2(i))+1, INT - функция, выделяющая целую часть аргумента. При использовании сети ibaseline на входы разрядов C2,q,j, где j = 1, k ¯ , q = 1, n / 2 ¯ , второго m-разрядного входа мультиплексора битов управления подают бит i-го разряда Ci (n-1)-разрядного выхода C1-Cn-1 кода управления сдвигом, причем i=mod(q-1,2j-1)+2j-1, где mod(q-1,2j-1) - функция, вычисляющая число q-1 по модулю 2j-1. Блок формирования битов маскирования и управления включает первый блок побитовой дизъюнкции с n-разрядным входом данных X1-Xn, соединенным с n-разрядным входом F1-Fn битов маскирования, n-разрядным выходом данных Y1-Yn, и входом AOR, первый блок побитовой дизъюнкции осуществляет функции побитовое логическое ИЛИ Yi=Xi∨AOR, где i = 1, n ¯ ; блок формирования битов маскирования и управления также включает n-разрядный мультиплексор битов маскирования, с выходом FO1-FOn, первым n-разрядным входом X1,1-X1,n, вторым n-разрядным входом X2,1-X2,n, соединенным выходом Y1-Yn первого блока побитовой дизъюнкции, входом AMUX, блок формирования битов маскирования и управления также включает n логических инверторов D1-Dn и n-1 модуль формирования битов кода управления сдвигом Mi,j, где i = 1,2 j − 1 ¯ , j = 1, k ¯ , каждый из которых имеет три бинарных входа f, ci, rotr, три бинарных выхода c, f1, f2, и выполняет логические функции: c = f ∧ c i ∨ f ∨ c i ¯ , f 1 = ( r o t r ¯ ∨ f ∨ c i ¯ ) ∧ ( f ∧ c i ¯ ) ¯ , f 2 = ( r o t r ∨ f ∨ c i ¯ ) ∧ ( f ∧ c i ¯ ) ¯ , входы rotr всех модулей Mi,j соединены с входом RL, модули Mi,j соединены так, что образуют двоичное дерево с k уровнями, при этом на уровне j содержится 2j-1 модулей Mi,j, причем выход с каждого из модулей Mi,j соединен с выходом Cp блока формирования битов маскирования и управления, где p=2j-1+i-1, выход f1 каждого модуля Mi,j, расположенного на уровне j соединен с входом f модуля M2i-1,j+,1, расположенного на уровне j+1, выход f2 каждого модуля Mi,j, расположенного на уровне j, соединен с входом f модуля M2i,j+1, расположенного на уровне j+1, вход f модуля M1,1 предназначен для сигнала с низким логическим уровнем, вход ci каждого модуля Mi,j, расположенного на уровне j, соединен с входом разряда Aj-1 входа A0-Ak-1, выход f1 каждого модуля Mi,k, расположенного на k-ом уровне, соединен с входом логического инвертора D2i-1, выход f2 каждого модуля Mi,k, расположенного на k-ом уровне, где i = 1, n / 2 ¯ , соединен с входом логического инвертора D2i каждый выход логического инвертора Di, где i = 1, n ¯ соединен с разрядом X1,i, первого входа мультиплексора битов маскирования; блок формирования битов маскирования и управления включает второй блок побитовой дизъюнкции с n-разрядным входом данных X1-Xn, соединенным с n-разрядным входом F1-Fn битов маскирования, выходом FI1-FIn, входом AIOR, второй блок побитовой дизъюнкции осуществляет функции побитовое логическое ИЛИ Yi=Xi∨AIOR, где i = 1, n ¯ . Многоуровневая коммутационная сеть baseline состоит из переключателей Ti,j, где i = 1, n / 2 ¯ , j = 1, k ¯ , расположенных в матричном порядке по n/2 линиям и k=log2n уровням, каждый переключатель имеет два бинарных входа X1, Х2, два бинарных выхода Y1, Y2 и бинарный вход управляющего сигнала C, каждый переключатель реализует логические функции Y 1 = C ∧ X 1 ∨ C ¯ ∧ X 2 , Y 2 = C ¯ ∧ X 1 ∨ C ∧ X 2 , бинарные входы управляющих сигналов переключателей сети образуют m-разрядный вход C1,1-Cn/2,k кода управления многоуровневой коммутационной сетью baseline, причем бинарный вход C переключателя Ti,j, где i = 1, n / 2 ¯ , j = 1, k ¯ , соединен с входом разряда Ci,j кода управления многоуровневой коммутационной сетью baseline, каждый переключатель сети j-го уровня, где j = 1, k − 1 ¯ , расположенный на линии с номером i, соединен первым выходом Y1 с первым входом X1 при нечетном i или со вторым входом X2 при четном i переключателя j+1 уровня, расположенного на линии с номером u i 1 = I N T ( i + 1 2 ) + 2 k − j − 1 ⋅ I N T ( i ⋅ 2 j − 1 ( 2 k − 1 + 1 ) ) , а вторым выходом Y2 с первым входом X1 при нечетном i или со вторым входом X2 при четном i переключателя j+1 уровня сети, расположенного на линии с номером u i 2 = I N T ( i + 1 2 ) + 2 k − j − 1 ⋅ I N T ( i ⋅ 2 j − 1 ( 2 k − 1 + 1 ) ) + 2 k − j − 1 , где INT - функция вычисления целой части от аргумента; первые входы X1 переключателей первого уровня Ti,1 где i = 1, n / 2 ¯ , являются входами нечетных разрядов X2i-1 n-разрядного входа сети baseline, вторые входы X2 переключателей первого уровня Ti,1, где i = 1, n / 2 ¯ , являются входами четных разрядов X2i, n-разрядного входа сети baseline, первые выходы Y1 переключателей последнего уровня Ti,k, где i = 1, n / 2 ¯ , являются выходами нечетных разрядов Y2i-1 n-разрядного выхода сети baseline, вторые выходы Y2 переключателей последнего уровня Ti,k где i = 1, n / 2 ¯ , являются выходами четных разрядов Y2i, n-разрядного выхода сети baseline. Обратная многоуровневая коммутационная сеть ibaseline состоит из переключателей Ti,j, где i = 1, n / 2 ¯ , j = 1, k ¯ , расположенных в матричном порядке по n/2 линиям и k=log2 n уровням, каждый переключатель имеет два бинарных входа X1, X2, два бинарных выхода Y1, Y2 и бинарный вход управляющего сигнала C, каждый переключатель реализует логические функции Y 1 = C ∧ X 1 ∨ C ¯ ∧ X 2 , Y 2 = C ¯ ∧ X 1 ∨ C ∧ X 2 , бинарные входы управляющих сигналов переключателей сети образуют m-разрядный вход C1,1-Cn/2,k кода управления обратной многоуровневой коммутационной сетью ibaseline, причем бинарный вход C переключателя Ti,j, где i = 1, n / 2 ¯ , j = 1, k ¯ , соединен с входом разряда Ci,j кода управления обратной многоуровневой коммутационной сетью ibaseline, каждый переключатель сети (k-j+1)-го уровня, где j = 1, k − 1 ¯ , расположенный на линии с номером i, соединен первым входом X1 с первым выходом Y1 при нечетном i или со вторым выходом Y2 при четном i переключателя (k-j)-го уровня, расположенного на линии с номером u i 1 = I N T ( i + 1 2 ) + 2 j − 2 ⋅ I N T ( i ⋅ 2 k − j ( 2 k − 1 + 1 ) ) , а вторым входом X2 с первым выходом Y1 при нечетном i или со вторым выходом Y2 при четном i переключателя (k-j)-го уровня сети, расположенного на линии с номером u i 2 = I N T ( i + 1 2 ) + 2 j − 2 ⋅ I N T ( i ⋅ 2 k − j ( 2 k − 1 + 1 ) ) + 2 j − 2 , где INT - функция вычисления целой части от аргумента, первые входы X1 переключателей первого уровня Ti,1, где i = 1, n / 2 ¯ , являются входами нечетных разрядов X2i-1 n-разрядного входа сети ibaseline, вторые входы X2 переключателей первого уровня Ti,1, где i = 1, n / 2 ¯ , являются входами четных разрядов X2i n-разрядного входа сети ibaseline, первые выходы Y1 переключателей последнего уровня Ti,k где i = 1, n / 2 ¯ , являются выходами нечетных разрядов Y2i-1 n-разрядного выхода сети ibaseline, вторые выходы Y2 переключателей последнего уровня Ti,k где i = 1, n / 2 ¯ , являются выходами четных разрядов Y2i n-разрядного выхода сети ibaseline. Каждый входной разряд Xi выходного соединителя соединен с выходным разрядом Yj, причем, если i - нечетное число, то j=m, а если i - четное число, то j=m+n/2, где число m определяют путем последовательного вычисления функции ξp(x)=2х-1+ap, где p = 1, k − 1 ¯ , аргументом функции ξp является значение функции ξp-1, а аргументом функции ξ1 является 1, значение ap определяют из двоичного представления номера i=ak-12k-1+…+a121+a020. Каждый выходной разряд Yi входного соединителя соединен с входным разрядом Xj, причем, если i - нечетное число, то j=m, а если i - четное число, то j=m+n/2, где число m определяют путем последовательного вычисления функции ξp(x)=2х-1+ap, где p = 1, k − 1 ¯ , аргументом функции ξp является значение функции ξp-1, а аргументом функции ξ1 является 1, значение ap определяют из двоичного представления номера i=ak-12k-1+…+a121+a020.

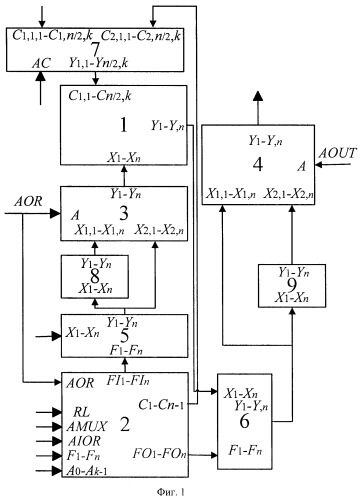

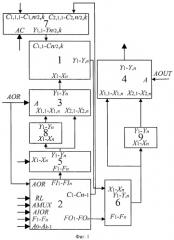

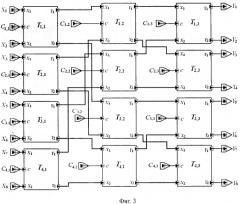

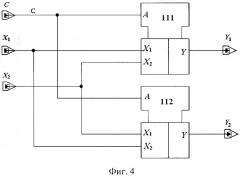

Изобретение поясняется чертежами, где на фиг.1 приведена блок-схема устройства, на фиг.2 приведена схема устройства для случая n=8, где n - число бит входных данных; на фиг.3 приведена схема многоуровневой коммутационной сети baseline для случая n=8; на фиг.4 приведена возможная схема переключателя многоуровневой коммутационной сети baseline или ibaseline; на фиг.5 приведена схема блока формирования битов маскирования и управления осуществлением циклических и логических сдвигов для случая n=8; на фиг.6 приведена схема модуля Mi,j формирования битов кода управления сдвигом; на фиг.7 приведена схема блока мультиплексоров для случая n=8; на фиг.8 приведена схема блока маскирования с использованием логических элементов «2И» для случая n=8; на фиг.9 приведена схема блока побитовой дизъюнкции с использованием логических элементов «2ИЛИ» для случая n=8. Позициями на чертежах обозначены:

1 - многоуровневая коммутационная сеть baseline или обратная многоуровневая коммутационная сеть ibaseline;

2 - блок формирования битов маскирования и управления;

3 - n-разрядный мультиплексор 2→1 входных данных;

4 - n-разрядный мультиплексор 2→1 выходных данных;

5 - n-разрядный блок маскирования данных на входе;

6 - n-разрядный блок маскирования данных на выходе;

7 - m-разрядный мультиплексор 2→1 битов управления, где m=n/2·log2(n);

8 - n-разрядный входной соединитель;

9 - n-разрядный выходной соединитель;

X1-Xn - n-разрядный вход данных многоуровневой коммутационной сети, n-разрядный вход данных n-разрядного блока маскирования данных на входе, n-разрядный вход данных n-разрядного блока маскирования данных на выходе, n-разрядные входы входного и выходного соединителей;

C1,1-Cn/2,k - m-разрядный вход кода управления сетью, где k=log2(n);

X1,1-X1,n - первый n-разрядный вход мультиплексоров 2→1 входных и выходных данных, первый n-разрядный вход n-разрядного мультиплексора 2→1 битов маскирования;

X2,1-X2,n - второй n-разрядный вход мультиплексоров 2→1 входных и выходных данных, второй n-разрядный вход n-разрядного мультиплексора 2→1 битов маскирования;

Y1-Yn - n-разрядные выходы мультиплексоров 2→1 входных и выходных данных, n-разрядные выходы блоков маскирования данных на входе и выходе, n-разрядный выход данных многоуровневой коммутационной сети, n-разрядные выходы входного и выходного соединителей, n-разрядный выход n-разрядного мультиплексора 2→1 битов маскирования;

C1,1,1-C1,n/2,k - первый m-разрядный вход битов управления, где m=n/2·k, k=log2(n);

С2,1,1-С2,n/2,k - второй m-разрядный вход битов управления, где m=n/2·k, k=log2(n);

Y1,1-Yn/2,k - m-разрядный выход мультиплексора, где m=n/2·k, k=log2(n);

C1-Cn-1 - (n-1)-разрядный выход кода управления сдвигом;

А0-Ak-1 - k-разрядный вход значения числа сдвига данных;

AOR - бинарный вход управления маскированием на выходе и мультиплексором входных данных;

RL - бинарный вход управления направлением сдвига данных;

AMUX - бинарный вход управления мультиплексором битов маскирования;

AIOR - бинарный вход управления маскированием на входе;

AOUT - бинарный вход управления мультиплексором выходных данных;

AC - бинарный вход управления мультиплексором битов управления;

F1-Fn - n-разрядный вход битов маскирования;

FO1-FOn - n-разрядный выход битов маскирования выходных данных;

FI1-FIn - n-разрядный выход битов маскирования входных данных;

Ti,j, где i = 1, n / 2 ¯ , i = 1, k ¯ , k=log2(n) - переключатели многоуровневой коммутационной сети baseline с первым Х1 и вторым Х2 бинарными входами данных, первым Y1 и вторым Y2 бинарными выходами данных, бинарным входом кода управления C;

23 - первый блок побитовой дизъюнкции;

24 - второй блок побитовой дизъюнкции;

25 - n-разрядны мультиплексор 2→1 битов маскирования;

Di, где i = 1, n ¯ - логические инверторы;

Mi,j - модули формирования битов кода управления сдвигом, где i = 1,2 j − 1 ¯ , j = 1, k ¯ ;

rotr, ci, f - бинарные входы модуля формирования битов кода управления сдвигом;

c, f1, f2 - бинарные выходы модуля формирования битов кода управления сдвигом;

A - бинарный вход управления мультиплексором 2→1;

211, 212, 213 - логические элементы 2И-НЕ;

214 - логический инвертор;

215, 216 - логические элементы 2ИЛИ;

217 - логический элемент 2ИЛИ-НЕ с инверсией сигнала на первом входе;

218 - логический элемент 2ИЛИ-НЕ;

MX - мультиплексоры 2→1 n-разрядного мультиплексора 2→1.

В дальнейшем изложении n означает число двоичных разрядов данных, k=log2(n) - число уровней преобразования, m=n/2·k - число двоичных разрядов кода управления сетью.

Устройство перестановок и сдвигов битов данных в микропроцессорах, предназначенное для осуществления операций логического и циклического сдвига данных, размещения и выборки группы битов данных, и произвольной перестановки битов данных, включает многоуровневую коммутационную сеть baseline или обратную многоуровневую коммутационную сеть ibaseline 1 с n-разрядным входом X1-Xn данных, n-разрядным выходом Y1-Yn данных, m-разрядным входом C1,1-Cn/2,k кода управления сетью.

Устройство также включает блок формирования битов маскирования и управления 2; n-разрядный мультиплексор 2→1 входных данных 3, n-разрядный мультиплексор 2→1 выходных данных 4, n-разрядный блок маскирования данных на входе 5, n-разрядный блок маскирования данных на выходе 6, m-разрядный мультиплексор 2→1 битов управления 7, n-разрядный входной соединитель 8 и n-разрядный выходной соединитель 9.

Вход данных устройства образован n-разрядным входом данных Х1-Xn n-разрядного блока маскирования данных на входе, на n-разрядный вход битов маскирования F1-Fn которого поступают биты с n-разрядного выхода битов маскирования входных данных FI1-FIn блока формирования битов маскирования и управления.

Блок маскирования данных на входе своим n-разрядным выходом Y1-Yn соединен со вторым n-разрядным входом Х2,1-Х2,n n-разрядного мультиплексора 2→1 входных данных и с n-разрядным входом Х1-Xn входного соединителя, который своим n-разрядным выходом Y1-Yn соединен с первым n-разрядным входом X1,1-X1,n n-разрядного мультиплексора 2→1 входных данных, бинарный вход управления которого A соединен с входом AOR устройства.

Мультиплексор 2→1 входных данных своим n-разрядным выходом Y1-Yn соединен с n-разрядным входом данных Х1-Xn многоуровневой коммутационной сети, которая своим n-разрядным выходом Y1-Yn соединена с n-разрядным входом данных n-разрядного блока маскирования данных на выходе.

Многоуровневая коммутационная сеть своим m-разрядным входом C1,1-Cn/2,k кода управления сетью соединена с m-разрядным выходом Y1,1-Yn/2,k m-разрядного мультиплексора 2→1 битов управления, имеющего первый m-разрядный вход C1,1,1-C1,n/2,k, бинарный вход управления AC, а второй m-разрядный вход С2,1,1-С2,n/2,k, соединенный с (n-1)-разрядным выходом C1-Cn-1 кода управления сдвигом. При этом, если используется многоуровневая коммутационная сеть baseline, бит первого разряда С1 кода управления сдвигом подается на входы разрядов C2,1,1-C2,n/2,1 m-разрядного входа мультиплексора 2→1 битов управления, бит второго разряда C2 кода управления сдвигом подается на входы разрядов C2,1,2-C2,n/4,2 m-разрядного входа мультиплексора 2→1 битов управления, бит третьего разряда C3 кода управления сдвигом подается на входы разрядов C2,n/4+1,2-C2,n/2,2 m-разрядного входа мультиплексора 2→1 битов управления и т.д. В общем случае бит i-го разряда Ci, i = 1, n − 1 ¯ , кода управления сдвигом подается на входы С2,q,r m-разрядного входа мультиплексора 2→1 битов управления, где

INT(i-2r-1)·2k-r<q<(INT((i-2r-1))+1)·2k-r+1, r=INT(log2(i))+1,

INT(x) - функция, выделяющая целую часть аргмента x.

При использовании сети ibaseline вместо сети baseline на входы разрядов C2,q,j, где j = 1, k ¯ , q = 1, n / 2 ¯ , m-разрядного входа мультиплексора 2→1 битов управления подают бит i-го разряда Ci (n-1)-разрядного выхода C1-Cn-1 кода управления сдвигом, причем i=mod(q-1,2j-1)+2j-1, где mod(q-1,2j-1) - функция, вычисляющая число q-1 по модулю 2j-1.

n-разрядный выход Y1-Yn блока маскирования данных на выходе соединен с входом Х1-Xn n-разрядного выходного соединителя и с первым n-разрядным входом мультиплексора 2→1 выходных данных, выход Y1-Yn n-разрядного выходного соединителя соединен со вторым n-разрядным входом мультиплексора 2→1 выходных данных. Вход управления A n-разрядного мультиплексора 2→1 выходных данных соединен с входом AOUT устройства, а n-разрядный выход Y1-Yn мультиплексора 2→1 выходных данных является выходом данных устройства.

n-разрядный выход FO1-FOn битов маскирования выходных данных блока формирования битов маскирования и управления соединен с n-разрядным входом F1-Fn битов маскирования n-разрядного блока маскирования данных на выходе.

Входы AIOR, RL, AMUX, A0-Ak-1, F1-Fn устройства образованы входами AIOR, RL, AMUX, A0-Ak-1, F1-Fn блока формирования битов маскирования и управления. Вход AOR устройства соединен с входом AOR блока формирования битов маскирования и управления и с входом управления A n-разрядного мультиплексора 2→1 входных данных.

Упомянутая ранее многоуровневая коммутационная сеть baseline имеет n бинарных входов, n бинарных выходов и состоит из переключателей Ti,j, где i = 1, n / 2 ¯ , j = 1, k ¯ , расположенных в матричном порядке по n/2 линиям и k=log2n уровням, каждый переключатель имеет два бинарных входа Х1, Х2, два бинарных выхода Y1, Y2 и бинарный вход управляющего сигнала, переключатели реализуют логическую функцию Y 1 = C ∧ X 1 ∨ C ¯ ∧ X 2 , Y 2 = C ¯ ∧ X 1 ∨ C ∧ X 2 , где знак ∨ означает логическую операцию дизъюнкция (логическое ИЛИ), знак ∧ означает логическую операцию конъюнкция (логическое И), а подчеркивание сверху означает операцию логического отрицания.

Бинарные входы управляющих сигналов переключателей сети образуют m-разрядный вход C1,1-Cn/2,k кода управления многоуровневой коммутационной сетью baseline, причем бинарный вход C переключателя Ti,j, где i =