Полупроводниковое устройство

Иллюстрации

Показать всеИзобретение относится к полупроводниковому устройству со схемой защиты от электростатического разряда. Полупроводниковое устройство включает в себя тонкопленочный диод и схему защиты с защитным диодом. Тонкопленочный диод включает в себя полупроводниковый слой с первой, второй и канальной областями, электрод затвора, первый электрод, соединенный с первой областью и электродом затвора, и второй электрод, соединенный со второй областью. Если тип удельной проводимости тонкопленочного диода является n-типом, то анодный электрод защитного диода соединяется с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. Если тип удельной проводимости тонкопленочного диода является P-типом, то катодный электрод защитного диода соединяется с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. Схема защиты не включает в себя другие диоды, которые соединены с линией так, чтобы получать направление течения тока, противоположное защитному диоду. В результате ухудшение свойств тонкопленочного диода может быть уменьшено при сведении к минимуму увеличения размера схемы. 11 з.п. ф-лы, 37 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение относится к полупроводниковому устройству со схемой, включающей в себя схему защиты от электростатического разряда (ЭСР).

УРОВЕНЬ ТЕХНИКИ

Полупроводниковое устройство со схемой, такое как подложка с активной матрицей, обычно имеет встроенную схему для защиты полупроводниковых компонентов в этой схеме от ЭСР. Такая схема защиты называется "схемой ЭСР-защиты".

Обобщенная схема ЭСР-защиты будет описана со ссылкой на Фиг. 35, которая демонстрирует иллюстративную схему ЭСР-защиты, предусмотренную для внутренней схемы ИС с комплементарной структурой металл-оксид-полупроводник (КМОП-структурой). Схема ЭСР-защиты, показанная на Фиг. 35, включает в себя защитное сопротивление R, которое располагается между входным контактом и КМОП-структурой, и два защитных диода D1 и D2 с взаимно разными полярностями. Каждый из этих двух диодов D1 и D2 соединяется с входной сигнальной линией КМОП-структуры.

В схеме ЭСР-защиты, когда входной контакт принимает заряд статического электричества, его потенциал либо повышается (+), либо падает (-). Если потенциал повышается (+), то включается защитный диод D1 и направляет положительные заряды в линию VCC. С другой стороны, если потенциал падает (-), то включается защитный диод D2 и направляет отрицательные заряды в линию VSS. В этом случае направление течения тока регулируется защитным сопротивлением R.

На подложке с активной матрицей устройства отображения схема, включающая в себя тонкопленочные транзисторы (TFT), которые выполняют функции переключающих элементов для пикселей, в большинстве случаев формируется путем нанесения полупроводниковой пленки кремния, металлооксидного полупроводника или любого другого подходящего материала. Кроме того, подложка с активной матрицей обычно имеет схему защиты для того, чтобы предотвратить повреждение этих TFT или межсоединений из-за статического электричества (см. Патентный Документ №1, например).

Фиг. 36 демонстрирует традиционную подложку с активной матрицей со схемами защиты. Эта конфигурация раскрывается в Патентном Документе №1.

Как показано на Фиг. 36, подложка с активной матрицей имеет массив тонкопленочных транзисторов 240, который включает в себя несколько линий 203 развертки и несколько сигнальных линий 204, которые были сформированы на изолирующей подложке, а также некоторое количество тонкопленочных транзисторов 205, которые располагаются на их пересечениях. Каждый из этих тонкопленочных транзисторов 205 имеет свои электрод истока, электрод затвора и электрод стока, соединенные с соотнесенной с ним сигнальной линией 204, соотнесенной с ним линией 203 развертки и соотнесенным с ним электродом пикселя (не показан), соответственно. Повсюду в этом массиве тонкопленочных транзисторов 240 каждая линия 203 развертки соединяется с линией 231 опорного напряжения через соотнесенную с ней схему 250 защиты. Каждая схема 250 защиты включает в себя два тонкопленочных диода 228 и 229 с взаимно разными полярностями. Аналогично, каждая сигнальная линия 204 тоже соединяется с линией 232 опорного напряжения через соотнесенную с ней схему 251 защиты. В соответствии с такой конфигурацией, даже если положительные или отрицательные заряды подаются либо на линию 203 развертки, либо на сигнальную линию 204, схема 250 или 251 защиты может направить эти заряды в соотнесенную с ней линию 231 или 232 опорного напряжения.

Следует отметить, что каждый из тонкопленочных диодов 226 - 229, которые входят в состав схем 250 и 251 защиты, показанных на Фиг. 36, имеет структуру, в которой исток и затвор тонкопленочного транзистора (например, тонкопленочного транзистора 205 пикселя) замыкаются накоротко друг с другом. Диод с такой структурой, в которой затвор и исток или сток тонкопленочного транзистора замыкаются накоротко друг с другом, будем называть в данном документе как "трехконтактный диод".

К тому же, в последнее время все чаще не только такие тонкопленочные транзисторы, выполняющие функции переключающих элементов, но и некоторые или все TFT для использования в периферийной схеме, такой как формирователь сигналов управления, располагаются на подложке с активной матрицей. Периферийная схема помещается не в зоне подложки с активной матрицей, где располагаются пиксели (которую будем называть в данном документе как "зона отображения"), а в другой зоне подложки с активной матрицей (которую будем называть в данном документе как "зона рамки"). В этом случае схемы защиты должны предусматриваться также и для тех элементов, например тонкопленочных транзисторов, которые формируют периферийную схему (см. Патентный Документ № 2, к примеру).

Фиг. 37 демонстрирует схему на транзисторах с изолированными затворами, которая предусматривается для подачи сигнала синхронизации на формирователь сигналов управления, который располагается в зоне рамки подложки с активной матрицей. Конфигурация схемы, показанная на Фиг. 37, раскрывается в Патентном Документе № 2.

Схема, показанная на Фиг. 37, включает в себя схему 1001 на транзисторах с изолированными затворами, которая располагается между контактной площадкой (контактная площадка OLB) 1011, которая принимает сигнал синхронизации, и секцией схемы формирователя сигналов управления, а также две схемы 1013 и 1016 защиты. Схема 1013 защиты располагается на входном конце схемы 1001 и включает в себя два диода 1014 и 1015 с взаимно противоположными полярностями. С другой стороны, схема 1016 защиты располагается на выходном конце схемы 1001 и включает в себя два диода 1017 и 1018 с взаимно противоположными полярностями. Диоды 1014 и 1017 соединяются с линией VDD, тогда как диоды 1015 и 1018 заземляются. В соответствии с такой конфигурацией, статическое электричество, которое было извне подано в линию 1019 через контактную площадку CLB 1011, может сниматься схемой 1013 защиты, а статическое электричество, которое было подано из схемы формирователя сигналов управления в линию 1019, может сниматься схемой 1016 защиты.

Как видно из примеров, продемонстрированных на Фиг. 35, 36 и 37, традиционные схемы ЭСР-защиты предусматриваются главным образом ради защиты трехконтактного тонкопленочного транзистора. Кроме того, каждая из этих схем ЭСР-защиты включает в себя, по меньшей мере, два диода с взаимно противоположными полярностями, которые являются прямосмещенным и обратносмещенным, соответственно, чтобы отводить заряды, подаваемые в защищаемую линию, - неважно, являются ли эти заряды положительными или отрицательными. К тому же, такая схема ЭСР-защиты располагается либо на входном, либо на выходном конце схемы, включающей в себя защищаемые тонкопленочные транзисторы, или даже на обоих ее концах. Именно поэтому схема ЭСР-защиты может препятствовать попаданию статического электричества в схему с трехконтактными тонкопленочными транзисторами на изолирующей подложке через ее либо входной, либо выходной конец. Как следствие, предусматривая такую схему защиты для основанного на активной матрице устройства отображения, например, схема защиты может препятствовать попаданию статического электричества в схему формирователя сигналов управления в зоне рамки (который может быть монолитным формирователем сигналов управления) от внешней соединительной контактной площадки (которая соединяется с формирователем сигналов управления на входном конце), из линии развертки, или из сигнальной линии (которая находится на выходном конце формирователя сигналов управления).

Список противопоставленных материалов

Патентная Литература

Патентный Документ № 1: Выложенная Публикация Заявки на Патент Японии № 11-119256

Патентный Документ № 2: Выложенная Публикация Заявки на Патент Японии № 2000-98338

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ТЕХНИЧЕСКАЯ ПРОБЛЕМА

Каждая из традиционных схем защиты, показанных на Фиг. 35 - 37, включает в себя, по меньшей мере, два диода. По этой причине, с такой схемой защиты, размер схемы неизбежно увеличивается, что является проблемой. Например, если такая традиционная схема защиты применяется к монолитному формирователю сигналов управления, то зона рамки устройства отображения должна увеличиваться и, следовательно, зона отображения может, наоборот, уменьшиться.

Вдобавок ко всему традиционная схема защиты располагается таким образом, чтобы защитить трехконтактные тонкопленочные транзисторы. Тем не менее авторы настоящего изобретения обнаружили с помощью экспериментов, что трехконтактные транзисторы не так легко, как трехконтактные диоды, разрушаются под воздействием статического электричества. Причины этого будут подробно описаны ниже. Именно поэтому схема защиты с традиционной конфигурацией не может предотвратить, для схемы, включающей в себя трехконтактные диоды в качестве ее внутренних схемных компонентов, наличия характеристики ее устройства, подверженной влиянию статического электричества, или неправильную работу из-за присутствия статического электричества.

Следовательно, задача настоящего изобретения состоит в том, чтобы эффективно предотвращать разрушение элементов, входящих в состав схем на изолирующей подложке, под воздействием статического электричества, без чрезмерного увеличения размера схемы.

Решение проблемы

Полупроводниковое устройство в соответствии с настоящим изобретением включает в себя схему, которая была сформирована на подложке и которая включает в себя тонкопленочный диод и схему защиты с защитным диодом. Тонкопленочный диод включает в себя: по меньшей мере, один полупроводниковый слой, который располагается на подложке и который имеет первую область, вторую область и канальную область, находящуюся между первой и второй областями; электрод затвора, который располагается таким образом, чтобы перекрываться с канальной областью; изолирующий слой затвора, который располагается между электродом затвора и полупроводниковым слоем; первый электрод, который располагается на первой области и который электрически соединен с первой областью и электродом затвора; и второй электрод, который располагается на второй области и электрически соединен с ней. В этом полупроводниковом устройстве (a) - тип удельной проводимости тонкопленочного диода может быть N-типом, и анодный электрод защитного диода может соединяться с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. Или (b) - тип удельной проводимости тонкопленочного диода может быть P-типом, и катодный электрод защитного диода может соединяться с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. Защитный диод и тонкопленочный диод не соединяются параллельно. Схема защиты не включает в себя другие диоды, соединенные с линией так, чтобы получать направление течения тока, противоположное защитному диоду.

В одном предпочтительном варианте осуществления защитный диод включает в себя: по меньшей мере, один полупроводниковый слой, который располагается на подложке и который имеет первую область, вторую область и канальную область, находящуюся между первой и второй областями; электрод затвора, который располагается таким образом, чтобы перекрываться с канальной областью; изолирующий слой затвора, который располагается между электродом затвора и полупроводниковым слоем; первый электрод, который располагается на первой области и который электрически соединен с первой областью и электродом затвора; и второй электрод, который располагается на второй области и электрически соединен с ней.

Соответственные полупроводниковые слои тонкопленочного диода и защитного диода могут быть выполнены из одной и той же полупроводниковой пленки.

Полупроводниковое устройство может дополнительно включать в себя множественные тонкопленочные транзисторы, которые имеют тот же тип удельной проводимости, что и тонкопленочный диод. При этом соответственные полупроводниковые слои тонкопленочных транзисторов и тонкопленочного диода могут быть выполнены из одной и той же полупроводниковой пленки.

В другом предпочтительном варианте осуществления не предусматриваются схемы защиты для линии, которая соединяется с электродом затвора каждого тонкопленочного транзистора.

Еще в одном предпочтительном варианте осуществления схема включает в себя либо входную секцию для ввода сигнала от внешнего устройства в схему, либо выходную секцию для вывода сигнала от схемы на внешнее устройство. Линия, которая соединяет друг с другом тонкопленочный диод и защитный диод, имеет меньшую длину, чем линия, которая соединяет друг с другом входную или выходную секцию и защитный диод.

Предпочтительно, если линия, которая соединяет друг с другом тонкопленочный диод и защитный диод, имеет длину 1 мм или меньше.

В другом предпочтительном варианте осуществления, (a) - тип удельной проводимости тонкопленочного диода может быть N-типом, и анодный электрод защитного диода может соединяться с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. При высоком потенциале анодного электрода защитного диода потенциал катодного электрода защитного диода тоже может быть высоким.

В альтернативном предпочтительном варианте осуществления (a) - тип удельной проводимости тонкопленочного диода может быть N-типом, и анодный электрод защитного диода может соединяться с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. Катодный электрод защитного диода может соединяться с линией, ведущей к источнику питания VDD.

Еще в одном предпочтительном варианте осуществления (b) - тип удельной проводимости тонкопленочного диода может быть P-типом, и катодный электрод защитного диода может соединяться с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. При низком потенциале катодного электрода защитного диода потенциал анодного электрода защитного диода тоже может быть низким.

В альтернативном предпочтительном варианте осуществления (b) - тип удельной проводимости тонкопленочного диода может быть P-типом, и катодный электрод защитного диода может соединяться с линией, которая соединена либо с электродом затвора, либо с первым электродом тонкопленочного диода. Анодный электрод защитного диода может соединяться с линией, ведущей к источнику питания VSS.

Схема может включать в себя сдвиговый регистр.

Преимущественные Эффекты Изобретения

Настоящее изобретение может существенно снизить вредное воздействие электростатического разряда на трехконтактные диоды, которые входят в состав схемы на изолирующей подложке, без чрезмерного уменьшения размера схемы. Благодаря этому настоящее изобретение может эффективно предотвращать неправильную работу схемы под влиянием статического электричества.

Настоящее изобретение особенно эффективно в тех случаях, когда применяется к подложке с активной матрицей со схемой формирователя сигналов управления.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

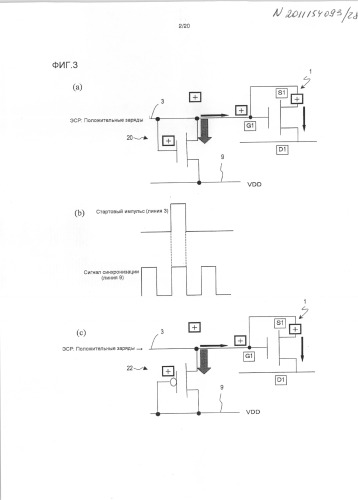

Фиг. 1 демонстрирует, как статическое электричество воздействует на внутрисхемный диод (N-канального типа).

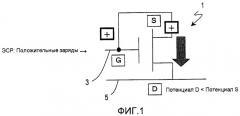

Фиг. 2 демонстрирует, как статическое электричество воздействует на внутрисхемный транзистор (N-канального типа).

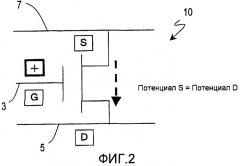

Фиг. 3(a)-3(c) демонстрируют схему в качестве предпочтительного варианта осуществления настоящего изобретения, причем каждая из Фигур 3(a) и 3(c) демонстрирует N-канальный внутрисхемный диод и защитную схему для защиты этого внутрисхемного диода, а Фиг. 3(b) показывает, как формы волны сигналов изменяются относительно друг друга на линиях 3 и 9 этих схем.

Фиг. 4(a)-4(c) демонстрируют схему в качестве предпочтительного варианта осуществления настоящего изобретения, причем каждая из Фиг. 4(a) и 4(c) демонстрирует P-канальный внутрисхемный диод и защитную схему для защиты этого внутрисхемного диода, а Фиг. 4(b) показывает, как формы волны сигналов изменяются относительно друг друга на линиях 3 и 8 этих схем.

Фиг. 5 демонстрирует часть схемы в качестве Примера №1 настоящего изобретения.

Фиг. 6 демонстрирует часть схемы в качестве Примера №2 настоящего изобретения.

Фиг. 7 демонстрирует часть схемы в качестве Примера №3 настоящего изобретения.

Фиг. 8 демонстрирует часть схемы в качестве Примера №4 настоящего изобретения.

Фиг. 9 демонстрирует часть схемы в качестве Примера №5 настоящего изобретения.

Фиг. 10 демонстрирует часть схемы в качестве Примера №6 настоящего изобретения, в котором электрод затвора ее внутрисхемного диода соединен с множественными линиями.

Фиг. 11 демонстрирует часть схемы в качестве Примера №7 настоящего изобретения, в котором электрод затвора ее внутрисхемного диода соединен с множественными линиями.

Фиг. 12 демонстрирует часть схемы в качестве Примера №8 настоящего изобретения, в котором электрод затвора ее внутрисхемного диода соединен с множественными линиями.

Фиг. 13 демонстрирует часть схемы в качестве Примера №9 настоящего изобретения, в котором электрод затвора ее внутрисхемного диода соединен с множественными линиями.

Фиг. 14 демонстрирует часть схемы в качестве Примера №10 настоящего изобретения, в котором электрод затвора ее внутрисхемного диода соединен с множественными линиями.

Фиг. 15 демонстрирует часть схемы в качестве Примера №11 настоящего изобретения, в котором электрод затвора ее внутрисхемного диода соединен с множественными линиями.

Фиг. 16 демонстрирует часть схемы в качестве Примера №12 настоящего изобретения, в котором электрод затвора ее внутрисхемного диода соединен с множественными линиями.

Фиг. 17 демонстрирует часть схемы в качестве Примера №13 настоящего изобретения, в котором первый электрод (электрод истока) ее внутрисхемного диода соединен с множественными линиями.

Фиг. 18 демонстрирует часть схемы в качестве Примера №14 настоящего изобретения, в котором первый электрод (электрод истока) ее внутрисхемного диода соединен с множественными линиями.

Фиг. 19 демонстрирует часть схемы в качестве Примера №15 настоящего изобретения, в котором тип удельной проводимости ее внутрисхемного диода является P-типом.

Фиг. 20 является схематическим видом в разрезе, демонстрирующим внутрисхемный диод в соответствии с первым предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 21(a) является схематическим видом в плане, демонстрирующим подложку с активной матрицей для жидкокристаллической (ЖК) панели, тогда как Фиг. 21(b) является видом в плане, схематично демонстрирующим структуру ее отдельного пикселя.

Фиг. 22 демонстрирует иллюстративную конфигурацию для сдвигового регистра в соответствии со вторым предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 23 демонстрирует иллюстративную конфигурацию для другого сдвигового регистра в соответствии со вторым предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 24 демонстрирует иллюстративную конфигурацию для сдвигового регистра в качестве сравнительного примера.

Фиг. 25(a) и 25(b) являются графиками, показывающими вольтамперные характеристики диода MM и транзистора MN в сдвиговом регистре сравнительного примера.

Фиг. 26 демонстрирует иллюстративную конфигурацию для еще одного сдвигового регистра в соответствии со вторым предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 27 демонстрирует конфигурацию для схемы в соответствии с третьим предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 28 демонстрирует конфигурацию для другой схемы в соответствии с третьим предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 29 демонстрирует конфигурацию для еще одной схемы в соответствии с третьим предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 30 демонстрирует конфигурацию для очередной схемы в соответствии с третьим предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 31 демонстрирует конфигурацию для очередной схемы в соответствии с третьим предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 32 демонстрирует конфигурацию для очередной схемы в соответствии с третьим предпочтительным вариантом осуществления настоящего изобретения.

Фиг. 33(a) демонстрирует традиционную схему со схемой ЭСР-защиты, а Фиг. 33(b) демонстрирует часть схемы, показанной на Фиг. 33(a).

Фиг. 34 демонстрирует, как работает схема защиты в соответствии с настоящим изобретением.

Фиг. 35 демонстрирует пример традиционной схемы ЭСР-защиты, предусмотренной для внутренней схемы ИС.

Фиг. 36 демонстрирует традиционную подложку с активной матрицей со схемой ЭСР-защиты.

Фиг. 37 демонстрирует традиционную схему со схемой ЭСР-защиты.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Когда схема, включающая в себя тонкопленочные транзисторы и тонкопленочные диоды, изготавливается путем нанесения полупроводниковой пленки на изолирующую подложку, иногда трехконтактные тонкопленочные диоды формируются, как описано выше, для того, чтобы изготовить тонкопленочные транзисторы и тонкопленочные диоды посредством одного и того же технологического процесса. Однако авторы настоящего изобретения обнаружили и подтвердили с помощью экспериментов, что трехконтактные тонкопленочные диоды в такой схеме больше подвержены воздействию статического электричества, чем трехконтактные тонкопленочные транзисторы. Причина этого будет описана ниже.

В этом описании изобретения диоды, которые формируют большую часть схемы и которые необходимы, чтобы дать возможность этой схеме выполнять предназначенную ей функцию, будем называть в данном документе как "внутрисхемные диоды", тогда как диоды, входящие в состав схемы защиты, будем называть в данном документе как "защитные диоды", чтобы четко различать эти два типа диодов друг от друга.

Фиг. 1 и 2 демонстрируют, как статическое электричество воздействует на внутрисхемный диод и внутрисхемный транзистор, которые, как предполагается, являются N-канальным диодом и N-канальным транзистором, соответственно, в данном примере.

Внутрисхемный диод 1, показанный на Фиг. 1, имеет три вывода электродов G, S и D затвора, истока и стока. Электрод G затвора соединяется с линией 3, тогда как электрод D стока соединяется с другой линией 5 (например, линией VDD). Электрод S истока замыкается накоротко с электродом G затвора. В таком внутрисхемном диоде 1, когда положительный заряд статического электричества поступает через линию 3 на электрод G затвора, одновременно положительное напряжение также подается и на электрод S истока, который соединен с электродом G затвора. Именно поэтому потенциал электрода S истока становится больше, чем электрода D стока, таким образом, включая диод 1 и производя ток большой величины, который течет между электродами S и D истока и стока. В результате канальный слой этого диода 1 может испортиться.

С другой стороны, во внутрисхемном транзисторе 10, показанном на Фиг. 2, его электрод S истока не замыкается накоротко с его электродом G затвора, а соединяется с третьей линией 7, но ни с линией 3, ни с линией 5. В этом транзисторе электроды G, D и S соединяются с тремя разными линиями. Именно поэтому, даже когда положительный заряд статического электричества поступает на электрод G затвора, например, уровни потенциала на электродах S и D истока и стока по-прежнему сохраняются практически равными друг другу. Таким образом, весьма вероятно, что транзистор 10 не включится. Как следствие, внутрисхемный транзистор 10 менее подвержен воздействию статического электричества, и гораздо меньше вероятность того, что канальный слой внутрисхемного транзистора 10 испортится из-за статического электричества.

С учетом этих результатов авторы настоящего изобретения обнаружили, что, если предусматривается схема защиты для трехконтактного диода, который легче всего поддается воздействию статического электричества среди разнообразных внутрисхемных элементов, эта схема защиты может эффективно предотвращать ухудшение под влиянием статического электричества характеристики этого внутрисхемного элемента или приведение схемы к неправильной работе. Это составляет основную идею настоящего изобретения.

Фиг. 3(a) и 4(a) демонстрируют конфигурации схем для применения в предпочтительном варианте осуществления настоящего изобретения. А именно, Фиг. 3(a) демонстрирует конфигурацию схемы для использования в ситуации, когда тип удельной проводимости защищаемого внутрисхемного диода является N-типом (т.е., если внутрисхемный диод является N-канальным диодом). С другой стороны, Фиг. 4(a) демонстрирует конфигурацию схемы для использования в ситуации, когда тип удельной проводимости защищаемого внутрисхемного диода является P-типом (т.е., если внутрисхемный диод является P-канальным диодом).

Схема, показанная на Фиг. 3(a), включает в себя N-канальный внутрисхемный диод 1 и схему защиты с защитным диодом 20, которая защищает внутрисхемный диод 1. Внутрисхемный диод 1 является трехконтактным диодом, который имеет электрод G1 затвора, первый электрод S1 (электрод истока) и второй электрод D1 (электрод стока). И его первый электрод S1 и электрод G1 затвора замыкаются накоротко друг с другом.

В этом описании изобретения один из двух электродов трехконтактного диода, который замыкается накоротко с электродом затвора, будем называть в данном документе как "первый электрод", тогда как другой электрод - как "второй электрод". Поэтому, полагая, что ток течет от истока к стоку, первый электрод N-канального диода является его электродом истока, а первый электрод P-канального диода является его электродом стока.

Анодный электрод защитного диода 20 соединяется с линией 3, которая электрически соединена с электродом G1 затвора внутрисхемного диода 1, тогда как его катодный электрод соединяется с линией 9 (которая является линией VDD в этом примере). Следует отметить, что линия 9 не должна быть именно линией VDD, а может быть также линией, которая имеет больший потенциал, чем линия VDD. Кроме того, предпочтительно, чтобы линия 9 не соединялась с транзистором, а включалась параллельно. Более того, как показано на Фиг. 3(b), сигнал на линии 9 может быть сигналом синхронизации, который устанавливается на высокий уровень при высоком уровне сигнала на линии 3. То есть потенциал сигнала на линии 9 просто должен быть не меньше, чем на линии 3. В этом случае ток не течет из линии 3 в линию 9, форма волны никогда не имеет усеченных краев, а рассеивание мощности никогда не увеличивается.

В примере, продемонстрированном на Фиг. 3(a), защитный диод 20 является трехконтактным диодом, включающим в себя электрод затвора, первый электрод и второй электрод. Тип удельной проводимости защитного диода 20 является N-типом, что совпадает с типом удельной проводимости внутрисхемного диода 1. Электрод затвора и первый электрод защитного диода 20 соединяются с линией 3, а его второй электрод соединяется с линией 9 VDD.

Когда положительный заряд статического электричества поступает в схему, продемонстрированную на Фиг. 3(a), через линию 3, ток течет из линии 3 в линию 9 VDD через защитный диод 20. В результате, величина тока, который течет через электрод G1 затвора защищаемого внутрисхемного диода 1, значительно уменьшается, как и величина тока, который течет между первым и вторым электродами S1 и D1 внутрисхемного диода 1. Следовательно, защитный диод 20 может предотвратить порчу внутрисхемного диода 1 из-за подачи статического электричества, а также может предотвратить неправильную работу схемы.

С другой стороны, никакого другого защитного диода не расположено на линии 3, так что ток течет через диод в противоположном направлении относительно защитного диода 20. И поэтому отрицательный заряд статического электричества, который введен в схему через линию 3, подается на внутрисхемный диод 1. В результате, первый электрод S1 внутрисхемного диода 1 приобретает более низкий потенциал, чем его второй электрод D1. Даже в таком случае ток не течет между этими первым и вторым электродами S1 и D1, и, следовательно, гораздо меньше вероятность порчи внутрисхемного диода 1 из-за подачи отрицательного заряда статического электричества. По этой причине, даже не предусматривая другой такой защитный диод, чтобы ток протекал через него в противоположном направлении относительно защитного диода 20, внутрисхемный диод 1 все-таки может быть надлежащим образом защищен от ЭСР, как и предполагалось.

Несмотря на то, что в примере, продемонстрированном на Фиг. 3(a), предполагается, что защитный диод 20 является диодом N-канального типа, также может предусматриваться P-канальный защитный диод 22, как показано на Фиг. 3(c).

Схема, показанная на Фиг. 4(a), включает в себя P-канальный внутрисхемный диод 2 и схему защиты с защитным диодом 22, которая защищает внутрисхемный диод 2. Внутрисхемный диод 2 является трехконтактным диодом, который имеет электрод G2 затвора, первый электрод D2 (электрод стока) и второй электрод S2 (электрод истока). И его первый электрод D2 и электрод G2 затвора замыкаются накоротко друг с другом.

Катодный электрод защитного диода 22 соединяется с линией 3, которая электрически соединена с электродом G2 затвора внутрисхемного диода 2, тогда как его анодный электрод соединяется с линией 8 (которая является линией VSS в этом примере). Следует отметить, что линия 8 не должна быть именно линией VSS, а может быть также линией, которая имеет меньший потенциал, чем линия VSS. Кроме того, предпочтительно, чтобы линия 8 не соединялась с транзистором, а включалась параллельно. Более того, как показано на Фиг. 4(b), сигнал на линии 8 может быть сигналом синхронизации, который устанавливается на низкий уровень при низком уровне сигнала на линии 3. То есть потенциал сигнала на линии 8 просто должен быть не больше, чем на линии 3. В этом случае ток не течет из линии 3 в линию 8, форма волны никогда не имеет усеченных краев, а рассеивание мощности никогда не увеличивается.

Когда отрицательный заряд статического электричества поступает в схему, продемонстрированную на Фиг. 4(a), через линию 3, ток течет из линии 8 VSS в линию 3 через защитный диод 22. В результате, защитный диод 22 может предотвратить поступление отрицательного заряда статического электричества на электрод G2 затвора внутрисхемного диода 2 и может предотвратить протекание тока большой величины от второго электрода S2 к первому электроду D2.

В этом примере никакого другого защитного диода не расположено на линии 3, так что ток течет через диод в противоположном направлении относительно защитного диода 22. Тем не менее, даже если отрицательный заряд статического электричества поступает на электрод G2 затвора внутрисхемного диода 2 через линию 3, ток не течет между вторым и первым электродами S2 и D2 внутрисхемного диода 2. Вот почему, даже не предусматривая другой такой защитный диод, внутрисхемный диод 2 все-таки может быть надлежащим образом защищен от ЭСР, как и предполагалось.

Хотя защитный диод 20 в примере, продемонстрированном на Фиг. 4(a), и является диодом P-канального типа, N-канальный защитный диод 20 тоже может использоваться, как показано на Фиг. 4(c).

Как можно видеть, если типом удельной проводимости защищаемого внутрисхемного диода 1 является N-тип, как показано на Фиг. 3, защитный диод 20, 22 должен быть расположен таким образом, чтобы иметь такое направление смещения, которое минимизирует накопление положительных зарядов на электроде G1 затвора и на первом электроде S1 внутрисхемного диода 1. То есть, если положительные заряды подаются на линию 3, которая соединяется либо с электродом G1 затвора, либо с первым электродом S1 внутрисхемного диода 1, защитный диод 20 должен быть расположен таким образом, чтобы отводить эти положительные заряды из линии 3 в другую линию 9 посредством защитного диода 20. С другой стороны, если типом удельной проводимости защищаемого внутрисхемного диода 2 является P-тип, как показано на Фиг. 4, защитный диод 20, 22 должен быть расположен таким образом, чтобы иметь такое направление смещения, которое минимизирует накопление отрицательных зарядов на электроде G2 затвора и на первом электроде D2 внутрисхемного диода 2. То есть, если отрицательные заряды подаются на линию 3, которая соединяется либо с электродом G2 затвора, либо с первым электродом D2 внутрисхемного диода 2, защитный диод 22 должен быть расположен таким образом, чтобы отводить эти положительные заряды из линии 3 в другую линию 8 посредством защитного диода 22.

Согласно этому предпочтительному варианту осуществления, поскольку схема защиты предусматривается для трехконтактного диода 1 или 2, который легче всего поддается воздействию статического электричества среди разнообразных внутрисхемных элементов, диод 1 или 2 может быть эффективно защищен от ЭСР без чрезмерного увеличения размера схемы.

Помимо этого схема защиты этого предпочтительного варианта осуществления не включает в себя какой-либо дополнительный защитный диод, который бы располагался таким образом, чтобы ток протекал через него в противоположном направлении относительно защитного диода 20 или 22. Таким образом, по сравнению с традиционной схемой защиты (см. Фиг. 35-37) число защитных диодов для оснащения может быть сокращено наполовину. В результате, размер схемы может быть уменьшен более эффективно при надлежащей защите от ЭСР внутрисхемного диода 1 или 2.

Защитный диод 20 или 22 этого предпочтительного варианта осуществления может располагаться в любой позиции при условии, что если напряжение, которое не ниже предварительно заданного напряжения, подается на внутрисхемный диод 1 или 2, то защитный диод 20 или 22 включается и производит разряд прежде, чем включится внутрисхемный диод 1 или 2. Кроме того, согласно этому предпочтительному варианту осуществления, электрод G1 или G2 затвора и первый электрод S1 или D2 внутрисхемного диода 1 или 2 не всегда должны напрямую соединяться с входной/выходной секцией по линии 3. В некоторых случаях другой внутрисхемный элемент, такой как транзистор, может помещаться между входной/выходной секцией и внутрисхемным диодом 1 или 2.

Предпочтительно, чтобы защитный диод 20 или 22 располагался на линии 3 как можно ближе к внутрисхемному диоду 1 или 2. Традиционная схема защиты располагается на входной/выходной секции схемы. И поэтому линия, которая соединяет схему защиты с защищаемым внутрисхемным элементом, достаточно велика, чтобы работать как, своего рода, антенна, которая притягивает статическое электричество. В результате, заряд статического электричества может поступать в защищаемый элемент. С другой стороны, если схема защиты располагается близко к защищаемому элементу (т.е. внутрисхемному диоду 1 или 2), то характеристика внутрисхемного диода 1 или 2 не ухудшается из-за статического электричества не только в случаях, когда заряд статического электричества поступает в схему через ее входную/выходную секцию, но и когда заряд статического электричества генерируется внутри схемы в ходе производственного процесса и поступает в схему через линию 3.

Согласно этому предпочтительному варианту осуществления защитный диод 20 или 22 просто должен быть расположен так, чтобы иметь предварительно заданное направление смещения, описанное выше и необязательно должен быть трехконтактным тонкопленочным диодом, как описано выше. Однако же для упрощения производственного процесса будет предпочтительнее, если защитный диод 20 или 22 является трехконтактным диодом, поскольку тогда защитный диод 20 или 22 и внутрисхемный диод 1 или 2 могут формироваться путем нанесения одной и той же полупроводниковой пленки. В этом случае предпочтительно, чтобы внутрисхемный диод 1 или 2 и защитный диод 20 или 22 имели одинаковый тип удельной проводимости.

Предпочтительно, чтобы схема этого предпочтительного варианта осуществления включала в себя не только внутрисхемный диод 1 или 2, но также еще и тонкопленочный транзистор. Это особенно предпочтительно, поскольку тонкопленочный транзистор, защитный диод и внутрисхемный диод могут формироваться за один раз путем нанесения одной и той же полупроводниковой пленки. В этом случае даже более предпочтительно, чтобы все эти элементы были трехконтактными, так как тогда такие элементы могут изготавливаться поср