Сдвиговый регистр, схема управления дисплеем, панель отображения и устройство отображения

Иллюстрации

Показать всеИзобретение относится к сдвиговому регистру и различным устройствам управления дисплеем. Техническим результатом является уменьшение размеров различных схем управления. Сдвиговый регистр предназначен для использования в схеме управления дисплеем, которая одновременно выбирает линии сигнала. Сдвиговый регистр включает в своем каскаде: триггер (FF), включающий в себя вывод инициализации (INITB); и схему генерирования сигнала, которая принимает сигнал одновременного выбора (сигнал AONB) и которая генерирует выходной сигнал (OUTB) каскада, используя выходной сигнал (Q, QB) триггера. Выходной сигнал (OUTB) каскада в триггере становится активным в результате активации сигнала одновременного выбора, оставаясь активным в течение периода одновременного выбор. Выходной сигнал (Q, QB) триггера (FF) является неактивным, в то время как вывод (INITB) инициализации, вывод (SB) установки и вывод (R) сброса триггера и вывод (INITB) инициализации триггера принимают сигнал одновременного выбора (сигнал AONB). 10 н. и 19 з.п. ф-лы, 34 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к сдвиговому регистру и различным устройствам управления дисплеем.

Уровень техники

В Патентной литературе 1 (см. фиг.34) раскрыта компоновка, в которой на элементы NAND (НЕ-И) подают (i) соответствующие выходные сигналы из соответствующих каскадов сдвигового регистра, включенного в схему управления затвором, и (И) сигнал DCG (цифрового генератора сигнала), и в которой элементы (НЕ-И) подают свои соответствующие выходные сигналы в соответствующие линии развертки. Такая компоновка позволяет (i) одновременно выбирать все линии сигнала развертки, делая сигнал DCG активным, когда устройство жидкокристаллического дисплея включают и выключают, и, таким образом, (ii) записывают Vcom (потенциал общего электрода) во все пиксели.

Список литературы

Патентная литература 1

Публикация, Tokukai №2000-347627 заявки на патент Японии (Дата публикации: 15 декабря 2000 г.)

Раскрытие изобретения

Техническая задача

Описанная выше обычная компоновка, к сожалению, требует использовать (i) элементы (НЕ-И), на которые подают соответствующие выходные сигналы от сдвигового регистра, и сигнал DCG и (ii) компоненты, которые инициализируют сдвиговый регистр после одновременного выбора всех линий сигнала развертки (например, (i) схему для генерирования сигнала инициализации и (ii) линию передачи). Это требование не позволяет уменьшить размеры схемы управления затвором.

Цель настоящего изобретения состоит в том, чтобы обеспечить сдвиговый регистр, который позволяет уменьшить размеры схемы управления дисплеем (различные схемы управления дисплеем).

Решение задачи

Сдвиговый регистр в соответствии с настоящим изобретением представляет собой сдвиговый регистр для схемы управления дисплеем, который одновременно выбирает линии сигнала, например, в заданные моменты времени, сдвиговый регистр, содержит в его каскаде: триггер, включающий в себя вывод инициализации; и схему генерирования сигнала, которая принимает сигнал одновременного выбора и которая генерирует выходной сигнал упомянутого каскада, с использованием выходного сигнала триггера, причем выходной сигнал упомянутого каскада становится активным в результате активации сигнала одновременного выбора, оставаясь активным в течение периода одновременного выбора; в то время как вывод инициализации триггера является активным, выходной сигнал триггера является неактивным, независимо от состояния другого входного вывода (триггера); и на вывод инициализации поступает одновременный сигнал выбора.

Представленная выше компоновка позволяет использовать сигнал одновременного выбора, в качестве сигнала для инициализации сдвигового регистра, и, таким образом, исключается необходимость дополнительно генерировать такой сигнал и подавать этот сигнал в каждый каскад. Это позволяет уменьшить размеры схемы управления дисплеем (то есть, различных схем управления дисплеем), включающий в себя сдвиговый регистр.

Полезные эффекты изобретения

Настоящее изобретение позволяет уменьшить размер схемы управления дисплеем (устройства управления дисплеем).

Краткое описание чертежей

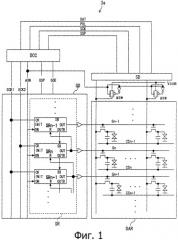

На фиг.1 показана схема, схематично иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

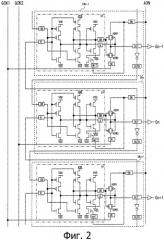

На фиг.2 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.1.

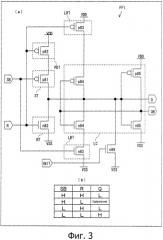

На фиг.3(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.2, и (b) показана таблица истинности для триггера.

На фиг.4 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.1 при включении.

На фиг.5 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.1 при выключении.

На фиг.6 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея фиг.1 при принудительном выключении.

На фиг.7 показана схема, иллюстрирующая другую конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

На фиг.8 показана принципиальная схема, иллюстрирующая вариант сдвигового регистра, представленного на фиг.2.

На фиг.9(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.8, и (b) показана таблица истинности для триггера.

На фиг.10 показана схема, иллюстрирующая еще одну другую конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

На фиг.11 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.10.

На фиг.12(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.11, и (b) показана таблица истинности для триггера.

На фиг.13 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.10 при включении.

На фиг.14 показана схема, иллюстрирующая еще одну конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 1 осуществления.

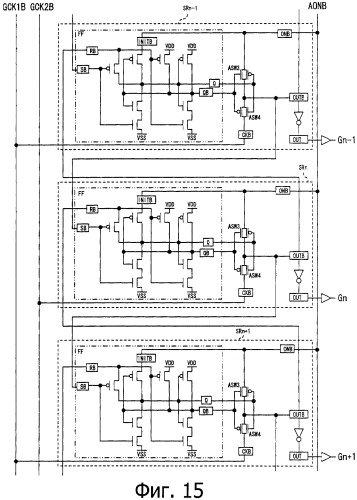

На фиг.15 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.14.

Фиг.16(а) показана принципиальная схема триггера сдвигового регистра, представленного на фиг.15, (b) показана временная диаграмма операций, и (с) показана таблица истинности для триггера.

На фиг.17 показана временная диаграмма, иллюстрирующая управление устройством жидкокристаллического дисплея фиг.14 при включении.

На фиг.18 показана принципиальная схема, иллюстрирующая вариант сдвигового регистра, представленного на фиг.15.

На фиг.19 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 2 осуществления.

На фиг.20 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.19.

На фиг.21 показана временная диаграмма, иллюстрирующая, как управляют устройством жидкокристаллического дисплея фиг.19 при включении.

На фиг.22 показана принципиальная схема, иллюстрирующая детальную конфигурацию (НЕ-И) по фиг.20.

На фиг.23 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 3 осуществления.

На фиг.24 показана принципиальная схема, иллюстрирующая каждый каскад сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.23.

На фиг.25 показана принципиальная схема, иллюстрирующая схему D-защелки схемы G-CS (блок наведения и управления) управления устройства жидкокристаллического дисплея, представленного на фиг.23.

На фиг.26 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея по фиг.23.

На фиг.27 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея фиг.23.

На фиг.28 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 4 осуществления.

На фиг.29 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея фиг.28.

На фиг.30 показана временная диаграмма, иллюстрирующая управления устройством жидкокристаллического дисплея фиг.28.

На фиг.31 показана принципиальная схема, иллюстрирующая пример конфигурации каждого каскада сдвигового регистра.

На фиг.32 показана схема, иллюстрирующая конфигурацию устройства жидкокристаллического дисплея в соответствии с вариантом 5 осуществления.

На фиг.33 показана принципиальная схема, иллюстрирующая часть сдвигового регистра устройства жидкокристаллического дисплея, представленного на фиг.32.

На фиг.34 показана принципиальная схема, иллюстрирующая конфигурацию обычного сдвигового регистра.

Осуществление изобретения

Варианты осуществления настоящего изобретения описаны ниже со ссылкой на фиг.1-33. В описании, представленном ниже, RS-триггер (триггер с раздельной установкой 0 и 1) (ниже обозначаемый FF, соответственно) имеет (i) вывод установки единицы (вывод S или вывод SB), на который подают сигнал установки (сигнал S или сигнал SB), (ii) вывод сброса (вывод R или вывод RB), на который подают сигнал сброса (сигнал R или сигнал RB), (iii) выходной вывод (вывод Q), на который выводят сигнал Q, и (iv) вывод инвертированного выхода (вывод QB), на который выводят сигнал QB. Представленное ниже описание относится к (i) потенциалу источника питания с высоким потенциалом (VDD), такому, как Vdd (ниже называется Высоким, соответственно) и (ii) потенциалу источника питания с низким потенциалом (VSS), такому, как Vss (ниже называется Низким, соответственно). Сигнал S (сигнал установки), сигнал R (сигнал сброса) и сигнал Q (выходной сигнал), каждый представляет собой сигнал, который имеет Высокий потенциал в течение его активного периода, тогда как сигнал SB (сигнал шины установки), сигнал RB (сигнал шины сброса) и сигнал QB (инвертированный выходной сигнал), каждый представляет сигнал, который имеет Низкий потенциал в течение его активного периода.

Вариант 1 осуществления

На фиг.1 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3а жидкокристаллического дисплея в соответствии с настоящим изобретением. Устройство 3а жидкокристаллического дисплея включает в себя: блок DAR дисплея; схему GD управления затвором; схему SD управления истоком; и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором сигнал AON (сигнал одновременного выбора), импульс GSP запуска затвора, сигнал GOE разрешения включения затвора и сигналы GCK1 и GCK2 тактовой частоты затвора. Схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема GD управления затвора включает в себя сдвиговый регистр SR, имеющий множество каскадов. В представленном ниже описании используется, соответственно, символ i-ого каскада Sri, для обозначения i-ого каскада (где i=1… n-1, n, n+1…) сдвигового регистра.

Сдвиговый регистр подает из его i-ого каскада SRi выходной сигнал (сигнал OUT) в линию Gi сигнала развертки, в блок DAR дисплея через буфер. Например, сдвиговый регистр подает со своего n-ого каскада SRn сигнал OUT в линию Gn сигнала развертки через буфер. Линия Gn сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, соединенного с электродом пикселя в PIXn. Электрод пикселя в PIXn формирует накопительный конденсатор (вспомогательный конденсатор), вместе с линией CSn накопительного конденсатора.

Устройство 3а жидкокристаллического дисплея включает в себя аналоговый переключатель asw и инвертор, в соответствии каждой сигнальной линией данных. Инвертор имеет вход, соединенный с сигнальной линией AON. Линия сигнала данных имеет конец, соединенный с первым электропроводным выводом аналогового переключателя asw, тогда как второй электропроводный вывод аналогового переключателя asw соединен с Vcom (потенциал общего электрода) источника питания. Аналоговый переключатель asw имеет (i) затвор стороны канала Р, соединенный с выходом инвертора и (И) затвор стороны канала N, соединенный с сигнальной линией AON.

На фиг.2 показана принципиальная схема, иллюстрирующая подробную конфигурацию части сдвигового регистра SR. Как показано на фиг.2, сдвиговый регистр включает в себя, в каждом из его каскадов: RS-триггер FF, включающий в себя вывод SB, вывод R и вывод INIT; два аналоговых переключателя ASW1 и ASW2; инвертор; вывод CK; вывод ON; вывод OUT; и вывод OUTB. Вывод INIT триггера FF соединен с выводом ON. Вывод Q триггера FF соединен с затвором на стороне канала Р аналогового переключателя ASW1 и с затвором на стороне канала N аналогового переключателя ASW2. Вывод QB FF соединен с затвором на стороне канала N аналогового переключателя ASW1 и с затвором на стороне канала Р аналогового переключателя ASW2. Аналоговый переключатель ASW1 имеет первый электропроводный электрод, соединенный с выводом ON, тогда как аналоговый переключатель ASW2 имеет первый электропроводный электрод, соединенный с выводом CK. Аналоговый переключатель ASW1 имеет второй электропроводный электрод, соединенный со вторым электропроводным электродом аналогового переключателя ASW2 и с выводом OUT, который представляет собой выходной вывод каскада. Вывод OUT соединен с выводом OUTB через инвертор.

Сдвиговый регистр SR выполнен таким образом, что вывод OUTB первого каскада соединен с выводом SB его следующего второго каскада и, что вывод OUT второго каскада соединен с выводом R первого каскада. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, тогда как вывод OUT (n+1)-ого каскада SRn+1 соединен с выводом R n-ого каскада SRn. Сдвиговый регистр SR имеет свой исходный каскад SR1, имеющий вывод SB, на который подают сигнал GSPB. Схема GD управления затвором выполнена таким образом, что вывод ON каждого каскада соединен с сигнальной линией AON, и что вывод CK каждого каскада с нечетным номером соединен с линией GCK (то есть, линией, через которую подают GCK), которая отличается от линии GCK, с которой соединен вывод CK каждого каскада с четным номером. Например, вывод CK n-ого каскада SRn соединен с сигнальной линией GCK2, тогда как вывод CK (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1.

Триггер FF на фиг.2 представляет собой FF1, показанный на фиг.3. Как показано на фиг.3, FF1 включает в себя: транзистор р84 с Р каналом и транзистор п84 с N каналом, составляющие схему КМОП; транзистор р85 с Р каналом и транзистор п85 с N каналом, составляющие схему КМОП; транзисторы р81, р82 и р83 с Р каналом; транзисторы n82, n83 и n99 с N каналом; вывод SB; вывод R; и выводы Q, и QB. р84 имеет затвор, соединенный с затвором n84, стоком р85, стоком n85 и выводом QB. р84 имеет сток, соединенный со стоком n84, стоком р81, стоком n82, затвором р85, затвором n85, стоком n99 и выводом Q. n84 имеет исток, соединенный со стоком n83. У р84 есть исток, соединенный со стоком р83. р81 имеет исток, соединенный со стоком р82. Вывод INIT соединен с затвором n99. Вывод SB соединен с затвором р81 и затвором n83. Вывод R соединен с затвором n82, затвором р82 и затвором р83. n85 имеет исток, соединенный с VSS. р82, р83 и р85, каждый имеет исток, соединенный с VDD. n82, n99 и n83, каждый имеет исток, соединенный с VSS. В FF1 р84, n84, р85 и n85 составляют схему LC защелки;

р81 используется, как транзистор ST установки; n82 используется, как транзистор RT сброса; р83 и n83, каждый используется, как транзистор LRT освобождения защелки; и р82 используется, как транзистор PDT определения приоритета.

(b) На фиг.3 показана таблица истинности для FF1. Как показано в позиции (b) на фиг.3, сигнал Q FF1 (i) является Низким (неактивным), в то время как сигнал SB является Высоким (неактивным), и сигнал R является Высоким (активным), (ii) сохраняет текущий потенциал, в то время как сигнал SB является Высоким (неактивным), и сигнал R является Низким (неактивным), (in) является Низким (неактивным), в то время как сигнал SB является Низким (активным), и сигнал R является Высоким (активным), и (iv) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Низким (неактивным). В триггере FF1, в случае, когда сигнал SB и сигнал R оба становятся активными, в то время когда вывод INIT является Высоким (активным), n82, n99 и р85 включают так, что сигнал Q становится Низким, и сигнал QB становится Высоким (неактивным).

На фиг.4-6 показаны временные диаграммы, иллюстрирующие осуществление управления устройством За жидкокристаллического дисплея, когда его включают, выключают и принудительно выключают, соответственно. На фиг.4-6 AON представляет сигнал AON (сигнал одновременного выбора); GSPB представляет сигнал шины импульса запуска затвора; GCK1 представляет сигнал GCK.1; и GCK2 представляет сигнал GCK2. Кроме того, SBi, Ri, Qi и OUTi (i=n-1, n и n+1), соответственно, представляют сигнал SB (потенциал на выводе SB), сигнал R (потенциал вывода R), сигнал Q (потенциал вывода Q) и сигнал OUT (потенциал вывода OUT) i-ого каскада SRi.

Когда устройство 3а жидкокристаллического дисплея включают и выключают, выполняется операция подготовки. В частности, операция подготовки делает сигнал AON активным (Высоким) в течение заданного периода. Поскольку ASW1 каждого каскада сдвигового регистра SR является включенным, сигнал OUT каждого каскада становится активным (Высоким), в результате активации, таким образом, что выбирают все линии сигнала развертки. Кроме того, аналоговый переключатель asw, соответствующий каждой линии сигнала данных, включается в результате активации сигнала AON, так, что во все линии сигнала данных подают Vcom. Поскольку в триггере каждого каскада, вывод INIT, в который подают сигнал AON, становится активным (Высоким), сигнал Q становится Низким (неактивным), и сигнал QB становится Высоким (неактивным). После окончания описанной выше операции подготовки (то есть, после того, как сигнал AON станет неактивным), устройство 3а жидкокристаллического дисплея достигает состояния, в котором Vcom было записано в каждый PIX в блоке DAR дисплея и, в котором сдвиговый регистр SR был инициализирован (то есть, выходной сигнал триггера в каждом каскаде стал неактивным).

Сдвиговый регистр SR устройства 3а жидкокристаллического дисплея выполняет следующую операцию в течение каждого периода вертикальной развертки (то есть, во время отображения каждого кадра): Когда сигнал SB, подаваемый в первый каскад, становится активным (=Низким), FF первого каскада устанавливается в единицу. Это обеспечивает Высокое (активное) состояние сигнала Q, и первый каскад в свою очередь принимает сигнал GCK через аналоговый переключатель ASW2. Когда сигнал GCK, подаваемый в первый каскад, становится активным (Высоким), сигнал OUT первого каскад становится активным (Высоким), и сигнал SB следующего второго каскада также становится активным. Это приводит к тому, что сигнал FF второго каскада становится активным, и второй каскад, в свою очередь, принимает сигнал GCK. Когда сигнал GCK второго каскада становится активным (Высоким), происходит сброс FF первого каскада. Это приводит к тому, что сигнал Q первого каскада становится Низким (неактивным) и включает аналоговый переключатель ASW1 первого каскада. Поскольку сигнал AON является Низким в этот момент времени, сигнал OUT первого каскад также становится Низким (неактивным).

Устройство 3а жидкокристаллического дисплея, когда его включают и выключают, одновременно выбирает все линии сигнала развертки таким образом, что идентичный потенциал (например, Vcom) записывают во все пиксели. Это предотвращает нарушение изображения, вызванное включением и выключением устройства 3а жидкокристаллического дисплея. По сравнению с обычной компоновкой (см. фиг.34), в настоящей компоновке (i) сигнал AON подают в ASW1, для устранения элемента НЕ-И на фиг.34, который принимает выходной сигнал каждого каскада и (ii) подает сигнал AON на вывод INIT каждого FF, для устранения необходимости в компоненте, который генерирует и передает сигнал для инициализации сдвигового регистра. Это позволяет уменьшить размеры схемы управления затвором. Кроме того, в настоящей компоновке сдвиговый регистр инициализируется (то есть, инициализируется триггер каждого каскада) при одновременном выборе всех линий сигнала развертки. Настоящая компоновка, таким образом, позволяет закончить операцию подготовки более быстро, чем в обычной компоновке, в которой по-отдельности выполняется одновременный выбор всех линий сигнала развертки и инициализация сдвигового регистра.

На фиг.7 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3b жидкокристаллического дисплея, которая включает в себя сдвиговый регистр SR по фиг.1 в схеме управления истоком. Такая конфигурация обеспечивает (i) прием исходным каскадом сдвигового регистра SR импульса SSP запуска истока и (ii) прием выводом CK каждого каскада сигнала SCK1 или SCK.2 шины тактовой частоты истока. Сигнал OUT i-ого каскада SRi подают в схему SAC выборки. Затем данные, выборка которых была выполнена на основе сигнала OUT, подают в линию SLi сигнала данных блока DAR дисплея через DAC. Например, сигнал OUT n-ого каскада SRn подают в схему SAC выборки, и данные, подаваемые на основе сигнала OUT, затем подают в линию SLn сигнала данных блока DAR дисплея через DAC. Линия SLn сигнала данных в блоке DAR дисплея, соединена с истоком транзистора, который соединен с электродом пикселя в PIXn.

Каждый каскад устройства 3а жидкокристаллического дисплея может быть выполнен, как показано на фиг.8. На фиг.8 иллюстрируется триггер FF, который представляет собой FF2, показанный на фиг.9. Как показано на фиг.9, триггер FF2 включает в себя: транзистор р84 с Р каналом и транзистор n84 с N каналом, составляющие схему КМОП; транзистор р85 с Р каналом и транзистор п85 с N каналом составляют схему КМОП; транзисторы р82, р83, р86 и р87 с Р каналом; транзисторы n81, n82, n83 и n88 с N каналом; вывод SB; вывод R; и выводы Q и QB. р84 имеет затвор, соединенный с затвором n84, стоком р85, стоком n85 и выводом QB. р84 имеет сток, соединенный со стоком n84, стоком р82, стоком n81, затвором р85, затвором n85, стоком n88 и выводом Q. n84 имеет исток, соединенный со стоком п83. р84 имеет исток, соединенный со стоком р83. р83 имеет исток, соединенный со стоком р87. р82 имеет исток, соединенный со стоком р86. n81 имеет исток, соединенный со стоком р82. Вывод INIT соединен с соответствующими затворами п88, р86 и р87. Вывод SB соединен с затвором р82, затвором n81 и затвором n83. Вывод R соединен с затвором n82 и затвором р83. n85 имеет исток, соединенный с VSS. р86, р87 и р85, каждый имеет исток, соединенный с VDD. n82, n88 и n83, каждый имеет исток, соединенный с VSS.

В позиции (b) на фиг.9 показана таблица истинности для FF2. Как показано в позиции (b) на фиг.9, сигнал Q FF2 (i) является Низким (неактивным), в то время как сигнал SB является Высоким (неактивным), и сигнал R является Высоким (активным), (ii) сохраняет текущий потенциал, в то время как сигнал SB является Высоким (неактивным), и сигнал R является Низким (неактивным), (iii) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Высоким (активным), и (iv) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Низким (неактивным). В триггере FF2, в случае, когда оба сигнал SB и сигнал R становятся активными, в то время как вывод INIT является Высоким (активным), р86 и р87 выключаются, и п88, и р85 включаются так, что сигнал Q становится Низким, и сигнал QB становится Высоким (неактивным).

Когда устройство 3а жидкокристаллического дисплея, имеющее конфигурацию по фиг.8 включают и выключают, выполняют операцию подготовки. В частности, операция подготовки делает сигнал AON активным (Высоким) в течение заданного периода. Поскольку ASW1 каждого каскада сдвигового регистра SR является включенным, сигнал OUT каждого каскада становится активным (Высоким) в результате активации, таким образом, что выбирают все линии сигнала развертки. Кроме того, аналоговый переключатель asw, соответствующий каждой линии сигнала данных, включают в результате активация сигнала AON, таким образом, что во все линии сигнала данных подают Vcom. Поскольку в триггере каждого каскада, вывод INIT, на который подают сигнал AON, становится активным (Высоким), сигнал Q становится Низким (неактивным), и сигнал QB становится Высоким (неактивным). После окончания представленной выше операции подготовки (то есть, после того, как сигнал AONB становится неактивным), устройство 3а жидкокристаллического дисплея достигает состояния, в котором Vcom было записано в каждый PIX в блоке DAR дисплея и, в котором сдвиговый регистр SR был инициализирован (то есть, выходной сигнал триггера каждого каскада стал неактивным).

Компоновка, показанная на фиг.8, обеспечивает установку триггера FF так, что она имеет приоритет по сравнению с его сбросом. Таким образом, когда одновременный выбор заканчивается (то есть, когда сигнал AON возвращается из активного состояния в неактивное состояние), сигнал SB, более вероятно, становится неактивным до сигнала R. Компоновка, показанная на фиг.8, таким образом, предотвращает неправильную работу, то есть, предотвращает выполнение сдвиговым регистром, после его инициализации, операции установки, в результате того, что сигнал R становится неактивным прежде, чем сигнал SB.

На фиг.10 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3х жидкокристаллического дисплея. Устройство 3х жидкокристаллического дисплея включает в себя: блок DAR дисплея; схему GD управления затвором; схему SD управления истоком; и схему DCC управления дисплеем. Схема DCC управления дисплеем подает в схему GD управления затвором сигнал AONB (сигнал одновременного выбора), импульс GSP запуска затвора, сигнал СОЕ разрешения включения затвора и сигналы GCK1 и GCK2 тактовой частоты затвора. Схема DCC управления дисплеем подает в схему SD управления истоком импульс SSP запуска истока, цифровые данные DAT, сигнал POL полярности и сигнал SCK тактовой частоты истока. Схема GD управления затвором включает в себя сдвиговый регистр SR, имеющий множество каскадов. Представленное ниже описание используют в качестве соответствующего символа i-ого каскада SRi для обозначения i-ого каскада (где i=1… n-1, n, n+1…) сдвигового регистра.

Сдвиговый регистр подает со своего i-ого каскада SRi выходной сигнал (сигнал OUT) в линию Gi сигнала развертки в блоке DAR дисплея через буфер. Например, сдвиговый регистр подает из его n-ого каскада SRn сигнал OUT в линию Gn сигнала развертки через буфер. Линия Gn сигнала развертки в блоке DAR дисплея соединена с затвором транзистора, соединенным с электродом пикселя в PIXn. Электрод пикселя в PIXn формирует накопительный конденсатор (вспомогательный конденсатор), вместе с линией CSn накопительного конденсатора.

Устройство 3х жидкокристаллического дисплея включает в себя аналоговый переключатель asw и инвертор, в соответствии с каждой сигнальной линией данных. Инвертор имеет вход, соединенный с сигнальной линией AON. Линия сигнала данных имеет конец, соединенный с первым электропроводным выводом аналогового переключателя asw, тогда как второй электропроводный вывод аналогового переключателя asw соединен с Vcom (потенциал общего электрода) источника питания. Аналоговый переключатель asw имеет (i) затвор стороны N канала, соединенный с выходом инвертора и (n) затвор стороны Р канала, соединенный с сигнальной линией AONB.

На фиг.11 показана принципиальная схема, иллюстрирующая подробную конфигурацию части сдвигового регистра SR. Как показано на фиг.11, сдвиговый регистр включает в себя, в каждом из его каскадов: RS-триггер FF, включающий в себя вывод SB, вывод R и вывод INITB; два аналоговых переключателя ASW13 и ASW14; инвертор;

вывод CKB; вывод ONB; вывод OUT; и вывод OUTB. Вывод INITB триггера FF соединен с выводом ONB. Вывод Q FF соединен с затвором на стороне Р канала аналогового переключателя ASW13 и с затвором на стороне N канала аналогового переключателя ASW14. Вывод QB FF соединен с затвором на стороне N канала аналогового переключателя ASW13 и с затвором на стороне Р канала аналогового переключателя ASW14. Аналоговый переключатель ASW13 имеет первый электропроводный электрод, соединенный с выводом ONB, тогда как аналоговый переключатель ASW14 имеет первый электропроводный электрод, соединенный с выводом CKB. Аналоговый переключатель ASW13 имеет второй электропроводный электрод, соединенный со вторым электропроводным электродом аналогового переключателя ASW14 и с выводом OUTB, который представляет собой выходной вывод каскада. Вывод OUTB соединен с выводом через инвертор.

Сдвиговый регистр SR выполнен таким образом, что вывод OUTB первого каскада соединен с выводом SB его следующего второго каскада и, что вывод OUT второго каскада соединен с выводом R первого каскада. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, тогда как вывод OUT (n+1)-ого каскада SRn+1 соединен с выводом R n-ого каскада SRn. Исходный каскад SR1 сдвигового регистра SR имеет вывод SB, который соединен сигналом GSPB. Схема GD управления затвором выполнена таким образом, что вывод ONB каждого каскада соединен с сигнальной линией AONB и, что вывод CKB каждого каскада с нечетным номером соединен с линией GCK (то есть, линией, через которую подают сигнал GCK), который отличается от линии GCK, с которой соединен вывод CKB каждого из каскада с четным номером. Например, вывод CKB n-ого каскада SRn соединен с сигнальной линией GCK2B, тогда как вывод CKB (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1B.

На фиг.11 иллюстрируется триггер FF, который представляет собой FF3, показанный на фиг.12. Как показано на фиг.12, триггер FF3 включает в себя: транзистор р84 Р канала и транзистор n84 N канала, составляющие схему КМОП; транзистор р85 с Р каналом и транзистор n85 с N каналом, составляющие схему КМОП; транзисторы р82 и р83 с Р каналом; транзисторы n81, n82 и n83 с N каналом; вывод SB; вывод R; и выводы Q, и QB. р84 имеет затвор, соединенный с затвором п84, стоком р85, стоком n85 и выводом QB. р84 имеет сток, соединенный со стоком п84, стоком р82, стоком n81, затвором р85, затвором n85 и выводом Q. n84 имеет исток, соединенный со стоком n83. n84 имеет исток, соединенный со стоком n83. n81 имеет исток, соединенный со стоком n82. Вывод INITB соединен с истоком р82. Вывод SB соединен с затвором р82, затвором n81 и затвором n3. Вывод R соединен с затвором n82 и затвором р83. n85 имеет исток, соединенный с VSS. р83 и р85, каждый имеет исток, соединенный с VDD. n82, n83 и n85, каждый имеет исток, соединенный с VSS.

В позиции (b) на фиг.12 показана таблица истинности для FF3. Как показано в (b) на фиг.12, сигнал Q FF3 (i) является Низким (неактивным), в то время как сигнал SB является Высоким (неактивным), и сигнал R является Высоким (активным), (и) сохраняют текущий потенциал, в то время как сигнал SB является Высоким (неактивным), и сигнал R является Низким (неактивным), (iii) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Высоким (активным), и (iv) является Высоким (активным), в то время как сигнал SB является Низким (активным), и сигнал R является Низким (неактивным). В триггере FF3, в случае, когда сигнал SB и сигнал R оба становятся активными, в то время как вывод INITB является Низким (активным), р85 включается так, что сигнал Q становится Низким, и сигнал QB становится Высоким (неактивным). Кроме того, в течение периода одновременного выбора (то есть, в то время как сигнал INITB является Низким; сигнал SB является Низким; и сигнал R является Высоким), сигнал Q имеет Vss+Vth (то есть, пороговое напряжение р82), и сигнал QB имеет Vdd (Высокий).

На фиг.13 показана временная диаграмма, иллюстрирующая управление устройством 3х жидкокристаллического дисплея во время включения. На фиг.13 AONB представляет сигнал AONB (сигнал одновременного выбора); GSPB представляет сигнал шины импульса запуска затвора; GCK1B представляет сигнал GCK1B; и GCK2B представляет сигнал GCK2B. Кроме того, SBi, Ri, Qi и OUTi (i=n-1, n, и n+1), соответственно, представляют сигнал SB (потенциал вывода SB), сигнал R (потенциал вывода R), сигнал Q (потенциал вывода Q) и сигнал OUT (потенциал вывод OUT) i-ого каскада SRL

Когда устройство 3х жидкокристаллического дисплея включают, выполняется операция подготовки. В частности, операция подготовки приводит к тому, что сигнал AONB становится активным (Низким) в течение заданного периода. Поскольку ASW13 каждого каскада сдвигового регистра SR является включенным, сигнал OUT каждого каскада становится активным (Высоким) в результате активации, так, что происходит выбор всех линий сигнала развертки. Кроме того, включают аналоговый переключатель asw, соответствующий каждой линии сигнала данных, в результате активации сигнала AON, так, что во все линии сигнала данных подают Vcom. Поскольку в триггере каждого каскада, вывод INITB, на который подают сигнал AONB, становится активным (Низким), сигнал Q становится Низким (неактивным), и сигнал QB становится Высоким (неактивным). После окончания описанной выше операции подготовки (то есть, после того, как сигнал AONB становится неактивным), устройство 3х жидкокристаллического дисплея достигает состояния, в котором Vcom записано в каждый PIX блока DAR дисплея и, в котором сдвиговый регистр SR был инициализирован (то есть, выходной сигнал триггера в каждом каскаде стал неактивным).

Устройство 3х жидкокристаллического дисплея, когда его включают и выключают, одновременно выбирает все линии сигнала развертки так, что идентичный потенциал (например, Vcom) записывают во все пиксели. Это предотвращает нарушение изображения, связанное с включением и выключением устройства 3х жидкокристаллического дисплея. По сравнению с обычной компоновкой (см. фиг.34), в настоящей компоновке (i) подают сигнал AONB ASW13 для устранения необходимости в элементе НЕ-И фиг.34, который принимает выходной сигнал каждого каскада, и (И) подают сигнал AONB на вывод INITB каждого FF для устранения необходимости в компоненте, который генерирует и передает сигнал для инициализации сдвигового регистра. Это позволяет уменьшить размеры схемы управления затвором. Кроме того, настоящая компоновка инициализирует сдвиговый регистр (то есть, инициализирует триггер каждого каскада) при одновременном выборе всех линий сигнала развертки. Настоящая компоновка, таким образом, может закончить операцию подготовки быстрее, чем обычная компоновка, которая осуществляет одновременный выбор всех линий сигнала развертки и инициализацию сдвигового регистра по-отдельности. Кроме того, настоящая компоновка обеспечивает установку триггера FF так, чтобы она имела приоритет над его сбросом. Таким образом, когда одновременный выбор заканчивается (то есть, когда сигнал AONB возвращается из активного состояния в неактивное состояние), сигнал SB, более вероятно, становится неактивным прежде сигнала R. Настоящая компоновка, таким образом, предотвращает неправильную работу, то есть, предотвращает выполнение сдвиговым регистром, после его инициализации операции установки, из-за того, что сигнал R становится неактивным, до сигнала SB.

На фиг.14 показана принципиальная схема, иллюстрирующая конфигурацию устройства 3с жидкокристаллического дисплея, которое представляет собой вариант устройства 3х жидкокристаллического дисплея.

На фиг.15 показана принципиальная схема, иллюстрирующая подробную конфигурацию части сдвигового регистра SR, включенного в устройство 3с жидкокристаллического дисплея. Как показано на фиг.15, сдвиговый регистр включает в себя, в каждом из его каскадов: RS-триггер FF, включающий в себя вывод SB, вывод RB и вывод INITB; два аналоговых переключателя ASW3 и ASW4; инвертор; вывод CKB; вывод ONB; вывод OUT; и вывод OUTB. Вывод INITB триггера FF соединен с выводом ONB. Вывод Q FF соединен с затвором на стороне Р канала аналогового переключателя ASW3 и с затвором на стороне N канала аналогового переключателя ASW4. Вывод QB FF соединен с затвором на стороне N канала аналогового переключателя ASW3 и с затвором на стороне Р канала аналогового переключателя ASW4. Аналоговый переключатель ASW3 имеет первый электропроводный электрод, соединенный с выводом ONB, в то время как аналоговый переключатель ASW4 имеет первый электропроводный электрод, соединенный с выводом CKB. Аналоговый переключатель ASW3 имеет второй электропроводный электрод, соединенный со вторым электропроводным электродом аналогового переключателя ASW4 и с выводом OUTB, который представляет собой выходной вывод каскада. Вывод OUTB соединен с выводом OUT через инвертор.

Сдвиговый регистр SR установлен так, что вывод OUTB первого каскада соединен с выводом SB следующего второго каскада, и вывод OUTB второго каскада соединен с выводом RB первого каскада. Например, вывод OUTB n-ого каскада SRn соединен с выводом SB (n+1)-ого каскада SRn+1, в то время как вывод OUTB (n+1)-ого каскада SRn+1 соединен с выводом RB n-ого каскада SRn. Исходный каскад SR1 сдвигового регистра SR имеет вывод SB, на который подают сигнал GSPB. Схема GD управления затвором выполнена таким образом, что вывод ONB каждого каскада соединен с сигнальной линией AONB, и вывод CKB каждого каскада с нечетным номером соединен с линией GCKB (то есть, линией, через которую подают GCK сигнал тактовой частоты затвора), которая отличается от линии GCKB, с которой соединен вывод CKB каждого каскада с четным номером. Например, вывод CKB n-ого каскада SRn соединен с сигнальной линией GCK2B, в то время как вывод CKB (n+1)-ого каскада SRn+1 соединен с сигнальной линией GCK1B.

Триггер FF на фиг.15 представляет собой FF4, показанный на фиг.16. Как показано на фиг.16, FF4 включает в себя: транзистор р6 с Р каналом и транзистор n5 с каналом N, составляющие схем