Квадратурный компенсатор импульсных помех

Иллюстрации

Показать всеИзобретение относится к области цифровых систем приема и обработки сигналов и предназначено для уменьшения влияния аддитивных случайных импульсных помех. Достигаемый технический результат - уменьшение вероятности ошибочного приема канального символа, повышение помехоустойчивости. Квадратурный компенсатор импульсных помех включает в себя фильтр низких частот (ФНЧ) синфазного канала, ФНЧ квадратурного канала, блок выделения помехи, идентичные компенсатор импульсной помехи синфазного канала и компенсатор импульсной помехи квадратурного канала. Квадратурный компенсатор импульсных помех по варианту включает в себя фильтр низких частот (ФНЧ) синфазного канала, ФНЧ квадратурного канала, блок выделения помехи, идентичные компенсатор импульсной помехи синфазного канала и компенсатор импульсной помехи квадратурного канала и формирователь управляющих импульсов. 2 н. и 15 з.п. ф-лы, 11 ил.

Реферат

ОБЩАЯ ХАРАКТЕРИСТИКА ИЗОБРЕТЕНИЯ

Область техники

Изобретение относится к области цифровых систем приема и обработки сигналов и предназначено для уменьшения влияния аддитивных случайных импульсных помех.

Уровень техники

Задача борьбы с негативным воздействием случайных импульсных помех, имеющихся в радиоканале, актуальна для радиосистем связи и локации и поэтому давно является предметом инженерных разработок.

Известны способы и устройства борьбы с воздействием случайных импульсных помех, описанные, например, в патентах США: 7706542, 7573959, 7366491, 7302024, 7298312, 7236545, 7103122, 6122332, 6690805, 5867539, 5812673, 5703904, 5311087, 5140704, 4704736 др.

В устройстве стробирования и обработки импульсных помех в системах с SCDMA Chip Blanking and Processing in SCDMA to Mitigate Impulse and Burst Noise and/or Distortion, описанном в патентах США 7573959 и 7236545, содержатся блок задержки Delay Block, блок обнаружения импульсной помехи Impulse Noise Detection Block и т.д. Однако данные устройства предназначено для борьбы с импульсными помехами длительностью от одного до нескольких чипов.

В патенте США 7103122 описан подавитель помех Noise Canceller, включающий обнаружитель помехи Noise Detector, переключатель Switch, устройство выборки-хранения Hold Circuit и т.д. Здесь также предполагается, что длительность помехи много меньше, чем период несущего колебания.

Устройство подавления импульсного шума описано в патенте США 6993309 и включает блок обнаружения импульсной помехи Pulse Noise Detection Unit, блок компенсации импульсной помехи Pulse Noise Correction Unit и т.д. Однако данное устройство предполагает использование аналоговой фазовой модуляции.

Подавитель шумов Noise Reducing в соответствии с патентом США 6347146 включает в себя шумовой дискриминатор Noise Discriminator, устройство стробирования шума Noise Blanker, два квадратурных канала и использует аналоговую фазовую модуляцию.

В патенте США 5311087 описано устройство подавления импульсных помех Noise Removing Circuit, включающее устройство выборки-хранения Sample-and-hold Circuit, обнаружитель помехи Noise Detector и т.д. Устройство для уменьшения импульсного шума в цифровых приемниках по патенту США 6122332 включает обнаружитель импульсного шума Impulsive Noise Detector, блок подавления импульсного шума Impulsive Noise Correcting Unit, элемент задержки Delay Circuit и т.д. Однако данные устройства не учитывают особенности обработки квадратурных компонент принимаемого сигнала, в частности, наличие корреляции этих компонент при импульсной помехе.

Наиболее близким к заявленному решению является устройство для борьбы с импульсными помехами в радиосистемах с аналоговой фазовой модуляцией по патенту США 7706542 Noise Removal Device от 27.04.2010, содержащее блок выделения помехи Noise Extraction Unit, устройство выборки-хранения Hold Unit, сглаживающий фильтр Noise Smoothing Unit, устройство генерации сигналов управления Hold Control Signal Generation Unit, фильтр низких частот ФНЧ Low Pass Filter, пороговое устройство Comparator, блок вычисления модуля Absolute Value Circuit и т.п. Однако данное устройство предназначено для борьбы с импульсными помехами, длительность которых много меньше периода несущей или промежуточной частоты, и не может быть напрямую использовано в радиосистемах с цифровой модуляцией.

Целью заявляемого решения является устранение недостатков известных технических решений.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Целью заявленного технического решения является устранение негативного влияния импульсных помех, возникающих в радиоканале. К области его применения относятся цифровые системы радиосвязи, радиолокации, радионавигации и т.д. Наибольшая эффективность компенсации воздействия случайных импульсных помех с использованием данного технического решения достигается в случае, когда длительность импульса помехи меньше длительности канального импульса полезного сигнала.

Технический результат, получаемый от использования данного изобретения, заключается в уменьшении вероятности ошибочного приема канального символа и, как следствие, в повышении помехоустойчивости соответствующей радиосистемы.

Заявленная цель достигается посредством обнаружения импульсной помехи, определения ее параметров и интерполяции сигнала на время воздействия импульса помехи. Особенностью настоящего технического решения является учет корреляционной взаимосвязи импульсов помехи в квадратурных каналах, что обеспечивает его большую помехоустойчивость по сравнению с известными методами борьбы с импульсными помехами на основе различных ограничителей сигнала.

Известные компенсаторы импульсных помех включают в себя фильтр низких частот ФНЧ синфазного канала 1, ФНЧ квадратурного канала 3, блок выделения помехи 5.

В первом варианте заявленного квадратурного компенсатора импульсных помех введены идентичные компенсатор импульсной помехи синфазного канала 2 и компенсатор импульсной помехи квадратурного канала 4, причем выходы ФНЧ синфазного 1 и квадратурного 3 каналов соединены с первыми входами компенсаторов 2 и 4 соответствующего канала и соответственно с первым и вторым входом блока выделения помехи 5, выход которого соединен с вторыми входами компенсаторов 2 и 4 синфазного и квадратурного каналов, выходы которых являются соответственно синфазным и квадратурным выходом квадратурного компенсатора импульсных помех, входами которого являются входы ФНЧ синфазного 1 и квадратурного 3 канала.

При этом компенсаторы импульсной помехи в синфазном и квадратурном канале 2 и 4 выполнены в виде последовательно соединенных элемента задержки 21 и управляемого интерполятора 23, причем выход элемента задержки 21 подключен одновременно к первому входу управляемого интерполятора 23, первым входом компенсатора помехи является вход элемента задержки 21, вторым входом - второй вход управляемого интерполятора 23, а выходом - выход управляемого интерполятора 23.

Во втором варианте заявленного квадратурного компенсатора импульсных помех введены идентичные компенсатор импульсной помехи синфазного канала 2 и компенсатор импульсной помехи квадратурного канала 4, формирователь управляющих импульсов 6, причем выходы ФНЧ синфазного 1 и квадратурного 3 каналов соединены с первыми входами компенсаторов 2 и 4 соответствующего канала и соответственно с первым и вторым входом блока выделения помехи 5, выход которого соединен с вторыми входами компенсаторов 2 и 4 синфазного и квадратурного каналов и с входом формирователя управляющих импульсов 6, выход которого соединен с третьими входами компенсаторов 2 и 4 синфазного и квадратурного каналов, выходы которых являются соответственно синфазным и квадратурным выходом квадратурного компенсатора импульсных помех, входами которого являются входы ФНЧ синфазного 1 и квадратурного 3 канала.

При этом компенсаторы импульсной помехи в синфазном и квадратурном канале 2 или 4 выполнены в виде последовательно соединенных первого элемента задержки 21, управляемого интерполятора 23, сглаживающего фильтра 24 и коммутатора 25, а также второго элемента задержки 22, причем выход первого элемента задержки 21 подключен к первому входу управляемого интерполятора 23 и к входу второго элемента задержки 22, выход которого подключен ко второму входу коммутатора 25, первый вход которого соединен с выходом сглаживающего фильтра 24, первым входом компенсатора помехи является вход первого элемента задержки 21, вторым входом - второй вход управляемого интерполятора 23, третьим входом - третий вход коммутатора 25, а выходом - выход управляемого интерполятора 23.

Формирователь управляющих импульсов 6 выполнен в виде последовательно соединенных сглаживающего фильтра 61 и релейного элемента 62.

В упомянутых квадратурных компенсаторах импульсных помех блок выделения помехи 5 выполнен в виде двух каналов, каждый из которых содержит последовательно соединенные блок вычисления модуля 51 и 54, пороговое устройство 52 и 55, формирователь импульсов 53 и 56, а также логический блок ИЛИ 57, причем входы первого 51 и второго 54 блоков вычисления модуля являются соответственно первым и вторым входами блока выделения помехи 5, вторые входы пороговых устройств 52 и 55 соединены с выходом блока формирования порога 58, выходы формирователей импульсов 53 и 56 соединены с соответствующими входами логического блока ИЛИ 57, выход которого является выходом блока выделения помехи 5.

В компенсаторах помехи синфазного и квадратурного каналов управляемый интерполятор 23 выполнен в виде устройства выборки-хранения 231 и коммутатора 232, причем первый вход управляемого интерполятора 23 подключен ко второму входу коммутатора 232 и к первому входу устройства выборки-хранения 231, выход которого подключен к первому входу коммутатора 232, второй вход управляемого интерполятора 23 соединен со вторым управляющим входом устройства выборки-хранения 231 и с третьим управляющим входом коммутатора 232, выход которого является выходом управляемого интерполятора 23.

В блоке выделения помехи формирователь импульсов 53 или 56 содержит последовательно соединенные формирователь заднего фронта 534, устройство задержки 535, логический блок И 533, триггер 531, а также логический блок НЕ 532, причем вход формирователя импульсов 53 соединен с входом формирователя заднего фронта 534, входом логического блока НЕ 532 и входом установки в «логическую единицу» триггера 531, выход логического блока НЕ 532 соединен с вторым входом логического блока И 533, выход которого соединен с входом установки в «логический ноль» триггера 531, выход триггера 531 является выходом формирователя импульсов 53.

В формирователе импульсов устройство задержки 535 содержит два триггера 5351 и 5356, два логических блока ИЛИ 5352 и 5358, формирователь заднего фронта 5353, два формирователя переднего фронта 5355 и 5359, два элемента задержки 5354 и 5357, причем вход устройства задержки 535 соединен с входами установки в «логическую единицу» первого 5351 и второго 5356 триггеров, выходы первого 5351 и второго 5356 триггеров соединены с соответствующими входами первого логического блока ИЛИ и с входами соответственно первого 5355 и второго 5356 формирователей переднего фронта, выход первого формирователя переднего фронта 5355 через первый элемент задержки 5354 подключен к входу установки в «логический ноль» первого триггера 5351, а также к первому входу второго логического блока ИЛИ 5358, выход второго формирователя переднего фронта 5359 через второй элемент задержки 5357 подключен к второму входу второго логического блока ИЛИ 5358, выход которого подключен к входу установки в «логический ноль» второго триггера 5356, выход первого логического блока ИЛИ 5352 соединен с входом формирователя заднего фронта 5353, выход которого является выходом устройства задержки 535.

А в устройстве задержки формирователь переднего фронта 5355 и 5359 содержит последовательно соединенные элемент задержки 53551, логический блок XOR 53552 и логический блок И 53553, причем вход формирователя переднего фронта 5355 подключен к входу элемента задержки 53551, второму входу логического блока XOR 53552 и второму входу логического блока И 53553, выход которого является выходом формирователя переднего фронта 5355.

В управляемом интерполяторе и устройстве задержки формирователь заднего фронта 534 и 5353 содержит последовательно соединенные элемент задержки 53531, логический блок XOR 53532 и логический блок И 53533, причем вход формирователя заднего фронта 5353 подключен к входу элемента задержки 53531, второму входу логического блока XOR 53532, выход элемента задержки 53531 подключен к второму входу логического блока И 53533, выход которого является выходом формирователя заднего фронта 5353.

ПЕРЕЧЕНЬ ФИГУР

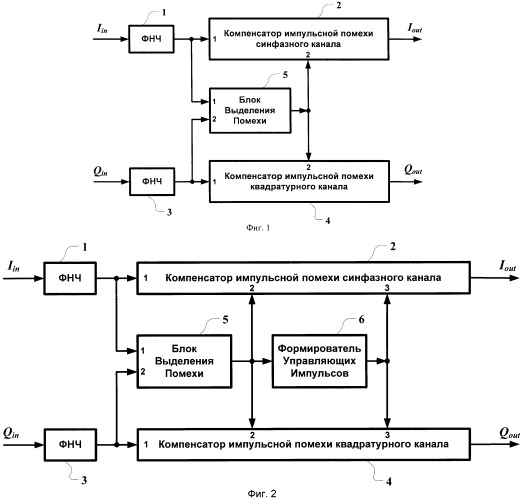

На Фиг.1 приведена структурная схема первого варианта реализации заявленного устройства.

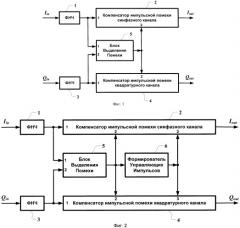

На Фиг.2 приведена структурная схема второго варианта реализации заявленного устройства.

На Фиг.3 приведена структурная схема варианта реализации компенсатора помех в синфазном и квадратурном каналах для первого варианта реализации заявленного устройства 2 и 4.

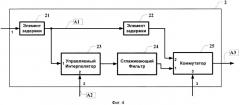

На Фиг.4 приведена структурная схема варианта реализации компенсатора помех в синфазном и квадратурном каналах для второго варианта реализации заявленного устройства 2 и 4.

На Фиг.5 представлен вариант реализации управляемого интерполятора нулевого порядка 23.

Фиг.6 содержит структурную схему блока выделения помехи 5.

Фиг.7 описывает реализацию формирователя импульсов 53.

На Фиг.8 приведена структурная схема устройства задержки 535.

На Фиг.9 приведена структурная схема формирователя сигнала, соответствующего переднему фронту импульса 5355.

На Фиг.10 приведена структурная схема формирователя сигнала, соответствующего заднему фронту импульса 5353.

Фиг.11 описывает реализацию формирователя управляющих импульсов 6.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Первый вариант реализации квадратурного компенсатора импульсных помех приведен на Фиг.1.

Данный компенсатор импульсных помех реализован в виде фильтра низких частот ФНЧ синфазного канала 1, ФНЧ квадратурного канала 3, блока выделения помехи 5, а также включает идентичные компенсатор импульсной помехи синфазного канала 2 и компенсатор импульсной помехи квадратурного канала 4, причем выходы ФНЧ синфазного 1 и квадратурного 3 каналов соединены с первыми входами компенсаторов 2 и 4 соответствующего канала и соответственно с первым и вторым входом блока выделения помехи 5, выход которого соединен с вторыми входами компенсаторов 2 и 4 синфазного и квадратурного каналов, выходы которых являются соответственно синфазным и квадратурным выходом квадратурного компенсатора импульсных помех, входами которого являются входы ФНЧ синфазного 1 и квадратурного 3 канала.

Сигналы каждого из квадратурных каналов через фильтры низких частот ФНЧ 1 и 3 подаются на первый вход компенсаторов помех соответствующего канала 2 и 4, а также соответственно на первый и второй входы блока выделения помехи 5. Блок выделения помехи 5 на основе анализа принимаемых сигналов формирует управляющие сигналы, соответствующие по времени моментам появления импульсов помехи. Эти управляющие сигналы поступают на вторые входы компенсаторов помех синфазного и квадратурного каналов 2 и 4 и используются для подавления импульсных помех.

Второй вариант реализации квадратурного компенсатора импульсных помех приведен на Фиг.2.

Данный квадратурный компенсатор импульсных помех реализован в виде фильтра низких частот ФНЧ синфазного канала 1, ФНЧ квадратурного канала 3, блока выделения помехи 5, а также включает идентичные компенсатор импульсной помехи синфазного канала 2 и компенсатор импульсной помехи квадратурного канала 4, формирователь управляющих импульсов 6, причем выходы ФНЧ синфазного 1 и квадратурного 3 каналов соединены с первыми входами компенсаторов 2 и 4 соответствующего канала и соответственно с первым и вторым входом блока выделения помехи 5, выход которого соединен с вторыми входами компенсаторов 2 и 4 синфазного и квадратурного каналов и с входом формирователя управляющих импульсов 6, выход которого соединен с третьими входами компенсаторов 2 и 4 синфазного и квадратурного каналов, выходы которых являются соответственно синфазным и квадратурным выходом квадратурного компенсатора импульсных помех, входами которого являются входы ФНЧ синфазного 1 и квадратурного 3 канала.

Сигналы каждого из квадратурных каналов через фильтры низких частот ФНЧ 1 и 3 подаются на первый вход компенсаторов помех соответствующего канала 2 и 4, а также соответственно на первый и второй входы блока выделения помехи 5. Блок выделения помехи 5 на основе анализа принимаемых сигналов формирует управляющие сигналы, соответствующие по времени моментам появления импульсов помехи. Эти управляющие сигналы поступают на вторые входы компенсаторов помех синфазного и квадратурного каналов 2 и 4 и используются для подавления импульсных помех.

Кроме того, выходной сигнал блока выделения помехи 5 поступает на вход формирователя управляющих импульсов 6, который формирует дополнительные управляющие сигналы, подаваемые на третьи входы компенсаторов помех синфазного и квадратурного каналов, выходы которых являются выходами квадратурного компенсатора импульсных помех.

Поскольку предлагаемые квадратурные компенсаторы импульсных помех предназначены для борьбы с импульсными помехами, у которых длительность импульсов меньше длительности канальных импульсов полезного сигнала, то полоса пропускания ФНЧ выбирается исходя из минимального искажения импульсов помехи и максимально возможной фильтрации аддитивного белого гауссовского шума АБГШ. То есть она должна быть согласована со спектром ожидаемых импульсных помех.

Вариантом реализации первого квадратурного компенсатора импульсных помех Фиг.1 является устройство, в котором компенсаторы помехи в синфазном и квадратурном канале 2 и 4 в соответствии с Фиг.3 выполнены в виде последовательно соединенных элемента задержки 21 и управляемого интерполятора 23, причем выход элемента задержки 21 подключен входу управляемого интерполятора 23, первым входом компенсатора помехи является вход элемента задержки 21, вторым входом - второй вход управляемого интерполятора 23, а выходом - выход управляемого интерполятора 23. Величина задержки в элементе задержки выбирается равной задержке сигнала в блоке выделения помехи 5.

Управляемый интерполятор 23 осуществляет стробирование (вырезание) импульсной помехи в соответствии с управляющим сигналом, приходящим на второй вход компенсаторов помехи 2 и 4 и поступающим затем на второй вход управляемого интерполятора 23. При этом на время действия импульсной помехи поведение сигнала определяется на основе интерполяции входного сигнала. На практике обычно достаточно использовать интерполяторы нулевого или первого порядка.

Вариантом реализации второго квадратурного компенсатора импульсных помех Фиг.2 является устройство, в котором компенсаторы помехи в синфазном и квадратурном канале 2 и 4 в соответствии с Фиг.4 выполнены в виде в виде последовательно соединенных первого элемента задержки 21, управляемого интерполятора 23, сглаживающего фильтра 24 и коммутатора 25, а также второго элемента задержки 22, причем выход первого элемента задержки 21 подключен входу управляемого интерполятора 23 и к входу второго элемента задержки 22, выход которого подключен ко второму входу коммутатора 25, первый вход которого соединен с выходом сглаживающего фильтра 24, первым входом компенсатора импульсной помехи 2 является вход первого элемента задержки 21, вторым входом - второй вход управляемого интерполятора 23, третьим входом - третий вход коммутатора 25, а выходом - выход коммутатора 25.

Управляемый интерполятор 23 осуществляет стробирование (вырезание) импульсной помехи в соответствии с управляющим сигналом, приходящим на второй вход компенсаторов помехи 2 и 4 и поступающим затем на второй вход управляемого интерполятора 23. При этом на время действия импульсной помехи поведение сигнала определяется на основе интерполяции входного сигнала. На практике обычно достаточно использовать интерполятор нулевого порядка.

Сглаживающий фильтр 24 представляет собой ФНЧ, характеристики которого выбираются исходя из требуемого порядка итоговой интерполяции сигнала на время действия импульса помехи.

Коммутатор 25 осуществляет передачу на выход компенсатора импульсных помех каждого канала сигнала с входа 1, когда управляющий сигнал равен «логическому нулю», и с входа 2, когда управляющий сигнал равен логической единице. Данный коммутатор реализован аналогично коммутатору 232 в управляемом интерполяторе 23. Элемент задержки 22 осуществляет задержку сигнала на время равное задержке сигнала в сглаживающем фильтре 24.

Управляемый интерполятор 23 в компенсаторах импульсных помех 2 и 4 в соответствии с Фиг.5 выполнен в виде устройства выборки-хранения 231 и коммутатора 232, причем первый вход управляемого интерполятора 23 подключен ко второму входу коммутатора 232 и к первому входу устройства выборки-хранения 231, выход которого подключен к первому входу коммутатора 232, второй вход управляемого интерполятора 23 соединен со вторым управляющим входом устройства выборки-хранения 231 и с третьим управляющим входом коммутатора 232, выход которого является выходом управляемого интерполятора 23.

Управляемый интерполятор 23 в случае использования алгоритма интерполяции нулевого порядка работает следующим образом Фиг.5: входной сигнал, содержащий смесь полезного сигнала, например с модуляцией BPSK, АБГШ и случайной импульсной помехи, поступает на вход 2 коммутатора 232 и на вход устройства выборки-хранения 231, выход которого подключен к входу 1 коммутатора 232. В номинальном режиме, когда импульсной помехи нет, входной сигнал управляемого интерполятора 23 через вход 2 коммутатора 232 передается на его выход. При появлении управляющего сигнала на входе 2 управляемого интерполятора 23 устройство выборки-хранения 231 запоминает величину входного сигнала и передает ее на вход 1 коммутатора 232. А коммутатор 232 переключается на считывание сигнала с входа 1. После возвращения управляющего сигнала на входе 2 управляемого интерполятора 23 к значению «логический ноль» коммутатор 232 возвращается к считыванию сигнала с входа 2. Таким образом, на время воздействия импульсной помехи уровень сигнала на выходе управляемого интерполятора 23 фиксируется и тем самым существенно уменьшается воздействие импульсной помехи.

Блок выделения помехи 5, структурная схема которого приведена на Фиг.6, в квадратурных компенсаторах импульсной помехи, представленных на Фиг.1 и 2, выполнен в виде двух каналов, каждый из которых содержит последовательно соединенные блок вычисления модуля 51 и 54, пороговое устройство 52 и 55, формирователь импульсов 53 и 56, а также логический блок ИЛИ 57, причем входы первого 51 и второго 54 блоков вычисления модуля являются соответственно первым и вторым входами блока выделения помехи 5, вторые входы пороговых устройств 52 и 55 соединены с выходом блока формирования порога 58, выходы формирователей импульсов 53 и 56 соединены с соответствующими входами логического блока ИЛИ 57, выход которого является выходом блока выделения помехи 5.

Блок выделения помехи 5 работает следующим образом: для сигналов, получаемых из каждого квадратурного канала, вычисляется абсолютное значение в блоках 51 и 52. Затем оно в пороговых устройствах 52 и 55 сравнивается с порогом, величина которого, нормированная к среднеквадратическому значению информационного сигнала, задается блоком формирования порога 58 и может быть рассчитана, например, в соответствии с формулой

U p = 1 + U n T s τ p h s n 2 , ( 1 )

где Ts - длительность канального символа, τр - средняя длительность импульсов помехи, h s n 2 - символьное отношение сигнал-шум (текущее или прогнозируемое), Un - коэффициент, зависящий от отношения сигнал-помеха h s p 2 . Величина Un может лежать в диапазоне от 3 до 6 при изменении отношения сигнал-помеха в диапазоне от 0 до 20 дБ.

Поскольку длительность импульсов на выходе пороговых устройств 52 и 55 определяется временем превышения импульсов помехи заданного порога, поэтому длительность этих импульсов будет меньше реальной длительности импульсов помехи. Для более полной компенсации импульсов помехи в формирователях импульсов 53 и 56 осуществляется увеличение длительности импульсов. Затем сформированные в каждом квадратурном канале управляющие импульсы объединяются в логической схеме ИЛИ 57.

Реализация блоков формирователей импульсов 53 и 56 приведена на Фиг.7. Каждый формирователь импульсов 53 и 56 содержит последовательно соединенные формирователь заднего фронта (534), устройство задержки (535), логический блок И (533), триггер (531), а также логический блок НЕ (532), причем вход формирователя импульсов (53) соединен с входом формирователя заднего фронта (534), входом логического блока НЕ (532) и входом установки в «логическую единицу» триггера (531), выход логического блока НЕ (532) соединен с вторым входом логического блока И (533), выход которого соединен с входом установки в «логический ноль» триггера (531), выход триггера (531) является выходом формирователя импульсов (53).

Формирователь импульсов 53 и 56 работает следующим образом: передним фронтом входного импульса триггер 531 переводится в состояние логической единицы. Формирователь заднего фронта 534 формирует короткий импульс, соответствующий заднему фронту входного импульса. Этот импульс задерживается на заданный интервал времени в устройстве задержки 535 и переводит триггер 531 в состояние «логического ноля». Логические схемы НЕ 532 и И 533 необходимы для предотвращения перевода триггера в состояние «логического ноля» при близком расположении входных импульсов, то есть когда задержанный задний фронт одного импульса попадает на длительность следующего за ним импульса.

Устройство задержки 535 (Фиг.8) содержит два триггера (5351 и 5356), два логических блока ИЛИ (5352 и 5358), формирователь заднего фронта (5353), два формирователя переднего фронта (5355 и 5359), два элемента задержки (5354 и 5357), причем вход устройства задержки (535) соединен с входами установки в «логическую единицу» первого (5351) и второго (5356) триггеров, выходы первого (5351) и второго (5356) триггеров соединены с соответствующими входами первого логического блока ИЛИ и с входами соответственно первого (5355) и второго (5356) формирователей переднего фронта, выход первого формирователя переднего фронта (5355) через первый элемент задержки (5354) подключен к входу установки в «логический ноль» первого триггера (5351), а также к первому входу второго логического блока ИЛИ (5358), выход второго формирователя переднего фронта (5359) через второй элемент задержки (5357) подключен ко второму входу второго логического блока ИЛИ (5358), выход которого подключен к входу установки в «логический ноль» второго триггера (5356), выход первого логического блока ИЛИ (5352) соединен с входом формирователя заднего фронта (5353), выход которого является выходом устройства задержки (535).

Устройство задержки 535 работает следующим образом: входной импульс, приходящий из формирователя заднего фронта 534 переводит первый 5351 и второй 5356 триггеры в состояние «логическая единица». В первом формирователе переднего фронта 5355 формируется короткий импульс, соответствующий переднему фронту импульса на выходе триггера 5351. Этот импульс с задержкой, определяемой первым элементом задержки 5354, переводит первый триггер 5351 в состояние «логического ноля». Величина задержки в элементе задержки 5354 может быть выбрана большей или равной средней длительности импульсов помехи.

Учитывая, что на входе устройства задержки 535 могут присутствовать импульсы с интервалом следования меньше величины задержки в первом элементе задержки 5354, предусмотрен дополнительный параллельный канал, включающий второй триггер 5356. второй формирователь переднего фронта 5359, второй элемент задержки 5357 и вторую схему ИЛИ 5358. Задержка во втором элементе задержки 5357 может быть выбрана равной задержке в первом элементе задержки 5354. Этот канал совместно с первой схемой ИЛИ 5352 и формирователем заднего фронта 5353 обеспечивает формирование выходного импульса, задержанного на заданную величину относительно последнего из близко расположенной пары входных импульсов.

Формирователь переднего фронта 5355, 5359 обеспечивает формирование короткого импульса, соответствующего переднему фронту импульса на его входе, и содержит последовательно соединенные элемент задержки (53551), логический блок XOR (53552) и логический блок И (53553), причем вход формирователя переднего фронта (5355) подключен к входу элемента задержки (53551), второму входу логического блока XOR (53552) и второму входу логического блока И (53553), выход которого является выходом формирователя переднего фронта (5355). Блок-схема формирователя переднего фронта приведена на Фиг.9. Элемент задержки 53551 в случае дискретных систем обеспечивает задержку на один такт.

Формирователь заднего фронта 5353, 534 обеспечивает формирование короткого импульса, соответствующего заднему фронту импульса на его входе, и содержит последовательно соединенные элемент задержки (53531), логический блок XOR (53532) и логический блок И (53533), причем вход формирователя заднего фронта (5353) подключен к входу элемента задержки (53531), второму входу логического блока XOR (53532), выход элемента задержки 53531 подключен к второму входу логического блока И (53533), выход которого является выходом формирователя заднего фронта (5353). Блок-схема формирователя переднего фронта приведена на Фиг.10. Элемент задержки 53531 в случае дискретных систем обеспечивает задержку на один такт.

Формирователь управляющих импульсов 6 предназначен для формирования «окна», в котором осуществляется замена фрагмента принимаемого сигнала на функцию, получаемую в результате сглаживания сигнала, в котором осуществлена компенсация импульсной помехи с использованием интерполятора нулевого порядка. Формирователь управляющих импульсов 6 выполнен в виде последовательно соединенных сглаживающего фильтра 61 и релейного элемента 62. Сглаживающий фильтр 61 аналогичен сглаживающему фильтру 24. Таким образом, на выходе релейного элемента 62 формируется прямоугольный импульс, длительность которого равна длительности окна, в котором в коммутаторе 25 осуществляется замена фрагмента принимаемого сигнала на сигнал с выхода сглаживающего фильтра 24.

На Фиг.12 приведены примеры эпюр сигналов, поясняющие работу компенсатора импульсных помех 2 (Фиг.4). Эпюры сигналов приведены для точек, обозначенных на Фиг.4 как A1, А2, A3. Данные сигналы представляют собой соответственно: входной сигнал до компенсации импульсной помехи (точка А1), сигнал на выходе блока выделения помехи 5 (точка А2) и сигнал на выходе компенсатора импульсной помехи 2 (точка A3).

1. Квадратурный компенсатор импульсных помех, включающий в себя фильтр низких частот (ФНЧ) синфазного канала (1), ФНЧ квадратурного канала (3), блок выделения помехи (5), отличающийся тем, что введены идентичные компенсатор импульсной помехи синфазного канала (2) и компенсатор импульсной помехи квадратурного канала (4), причем выходы ФНЧ синфазного (1) и квадратурного (3) каналов соединены с первыми входами компенсаторов импульсной помехи (2 и 4) соответствующего канала и соответственно с первым и вторым входом блока выделения помехи (5), выход которого соединен с вторыми входами компенсаторов (2 и 4) синфазного и квадратурного каналов, выходы которых являются соответственно синфазным и квадратурным выходом квадратурного компенсатора импульсных помех, входами которого являются входы ФНЧ синфазного (1) и квадратурного (3) канала.

2. Устройство по п.1, отличающееся тем, что компенсаторы импульсной помехи в синфазном и квадратурном канале (2 и 4) выполнены в виде последовательно соединенных элемента задержки (21) и управляемого интерполятора (23), причем выход элемента задержки (21) подключен к первому входу управляемого интерполятора (23), первым входом компенсатора импульсной помехи является вход элемента задержки (21), вторым входом - второй вход управляемого интерполятора (23), а выходом - выход управляемого интерполятора (23).

3. Устройство по п.2, отличающееся тем, что управляемый интерполятор (23) выполнен в виде устройства выборки-хранения (231) и коммутатора (232), причем первый вход управляемого интерполятора (23) подключен ко второму входу коммутатора (232) и к первому входу устройства выборки-хранения (231), выход которого подключен к первому входу коммутатора (232), второй вход управляемого интерполятора (23) соединен со вторым (управляющим) входом устройства выборки-хранения (231) и с третьим (управляющим) входом коммутатора (232), выход которого является выходом управляемого интерполятора (23).

4. Устройство по п.1, отличающееся тем, что блок выделения помехи (5) выполнен в виде двух каналов, каждый из которых содержит последовательно соединенные блок вычисления модуля (51 и 54), пороговое устройство (52 и 55), формирователь импульсов (53 и 56), а также логический блок ИЛИ (57), причем входы первого (51) и второго (54) блоков вычисления модуля являются соответственно первым и вторым входами блока выделения помехи (5), вторые входы пороговых устройств (52 и 55) соединены с выходом блока формирования порога (58), выходы формирователей импульсов (53 и 56) соединены с соответствующими входами логического блока ИЛИ (57), выход которого является выходом блока выделения помехи (5).

5. Устройство по п.4, отличающееся тем, что формирователь импульсов (53 или 56) содержит последовательно соединенные формирователь заднего фронта (534), устройство задержки (535), логический блок И (533), триггер (531), а также логический блок НЕ (532), причем вход формирователя импульсов (53) соединен с входом формирователя заднего фронта (534), входом логического блока НЕ (532) и входом установки в логическую единицу триггера (531), выход логического блока НЕ (532) соединен с вторым входом логического блока И (533), выход которого соединен с входом установки в логический ноль триггера (531), выход триггера (531) является выходом формирователя импульсов (53).

6. Устройство по п.5, отличающееся тем, что устройство задержки (535) содержит два триггера (5351 и 5356), два логических блока ИЛИ (5352 и 5358), формирователь заднего фронта (5353), два формирователя переднего фронта (5355 и 5359), два элемента задержки (5354 и 5357), причем вход устройства задержки (535) соединен с входами установки в логическую единицу первого (5351) и второго (5356) триггеров, выходы первого (5351) и второго (5356) триггеров соединены с соответствующими входами первого логического блока ИЛИ и с входами соответственно первого (5355) и второго (5356) формирователей переднего фронта, выход первого формирователя переднего фронта (5355) через первый элемент задержки (5354) подключен к входу установки в логический ноль первого триггера (5351), а также к первому входу второго логического блока ИЛИ (5358), выход второго формирователя переднего фронта (5359) через второй элемент задержки (5357) подключен ко второму входу второго логического блока ИЛИ (5358), выход которого подключен к входу установки в логический ноль второго триггера (5356), выход первого логического блока ИЛИ (5352) соединен с входом формирователя заднего фронта (5353), выход которого является выходом устройства задержки (535).

7. Устройство по п.6, отличающееся тем, что формирователь переднего фронта (5355 и 5359) содержит последовательно соединенные элемент задержки (53551), логический блок XOR (53552) и логический блок И (53553), причем вход формирователя переднего фронта (5355) подключен к входу элемента задержки (53551), второму входу логического блока XOR (53552) и второму входу логического блока И (53553), выход которого является выходом формирователя переднего фронта (5355).

8. Устройство по п.7, отличающееся тем, что формирователь заднего фронта (534 и 5353) содержит последовательно соединенные элемент задержки (53531), логический блок XOR (53532) и логический блок И (53533), причем вход формирователя заднего фронта (5353) подключен к входу элемента задержки (53531), второму входу логического блока XOR (53532), выход элемента задержки 53531 подключен к второму входу логического блока И (53533), выход которого является выходом формирователя заднего фронта (5353).

9. Квадратурный компенсатор импульсных помех, включающий в себя фильтр низких частот (ФНЧ) синфазного канала (1), ФНЧ квадратурного канала (3), блок выделения помехи (5), отличающийся тем, что введены идентичные компенсатор импульсной помехи синфазного канала (2) и компенсатор импульсной помехи квадратурного канала (4), формирователь управляющих импульсов (6), причем выходы ФНЧ синфазного (1) и квадратурного (3) каналов соединены с первыми входами компенсаторов импульсной помехи (2 и 4) соответствующего канала и соответственно с первым и вторым входом блока выделения помехи (5), выход которого соединен с вторыми входами компенсаторов импульсной помехи (2 и 4) синфазного и квадратурного каналов и с входом формиров